1

(61) 1166099

(21)4488467/24-24

(22)2У.09.8

(46) 15.и7.УО. Бюл. № 26 (71) Винницкий политехнический институт

(.72) В.П.Кожемяко, Н.А.Квитка, В.С.Стратиенко и С.Н.Квитка

(53)681.325.5 (08.8)

(56)Авторское свидетельство СССР № 11660У9, кл. Г, 06 F 7/50,, 19Ь4.

(54)ПАРАЛЛЕЛЬНЫЙ НАКАПЛИВАЮЩИЙ СУММАТОР

(57)Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных машинах и цифровых устройствах роботизированных систем управления для сложения чисел с иррациональным основанием и обработки векторной информации. Целью изобретения является расширение функциональных возможностей за счет сложения чисел с иррациональным основанием J2. Сумматор содержит триггеры 1 разрядов сумматора, элементы НЕРАВНОЗНАЧНОСТЬ 2 разрядов сумматора, входные мультиплексоры 3, выходные мультиплексоры 4 с соответствующими связями. 1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Последовательный сумматор | 1989 |

|

SU1709298A2 |

| Параллельный накапливающий сумматор | 1986 |

|

SU1399726A1 |

| Параллельный накапливающий сумматор | 1988 |

|

SU1564614A1 |

| Сумматор последовательного действия | 1989 |

|

SU1689945A2 |

| Параллельный накапливающий сумматор | 1987 |

|

SU1587496A1 |

| Устройство для суммирования двоичных чисел | 1988 |

|

SU1578709A2 |

| Арифметико-логическое устройство | 1987 |

|

SU1495782A1 |

| Последовательный сумматор | 1987 |

|

SU1411734A1 |

| Преобразователь кодов | 1988 |

|

SU1501279A1 |

| Преобразователь кодов | 1988 |

|

SU1529458A1 |

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных машинах и цифровых устройствах роботизированных систем управления для сложения чисел с иррациональным основанием и обработки "векторной" информации. Целью изобретения является расширение функциональных возможностей за счет сложения чисел с иррациональным основанием √2. Сумматор содержит триггеры 1 разрядов сумматора, элементы НЕРАВНОЗНАЧНОСТЬ 2 разрядов сумматора, входные мультиплексоры 3, выходные мультиплексоры 4 с соответствующими связями. 1 ил.

,10

.10-,

,ю6

№

,ю,

.Ю,

10,

|0;

(Я

ел j

00 Ы

Ю

Й4№Ь В}136353 8гЦ5г 8,7,6,5,

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных машинах и цифровых устройствах роботизированных систем управления для сложения чисел с иррациональным основанием обработки векторной информации и является усовершенствованием изобретения по авт.ев № 11660У9

Цель изобретения - расширение функциональных возможностей за счет сложения чисел с иррациональным основанием -J.

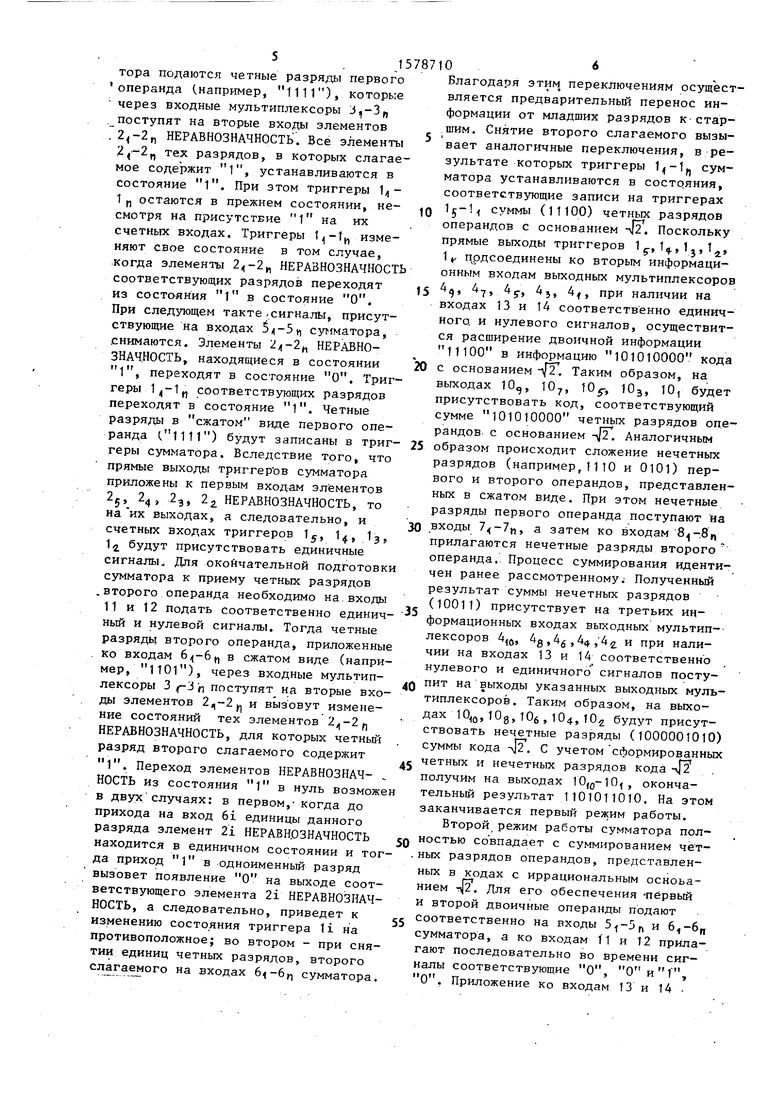

На чертеже представлена функциональная схема параллельного накапливающего сумматора (для ).

Сумматор содержит триггеры разрядов сумматора, элементы НЕРАВНОЗНАЧНОСТЬ разрядов сумматора, входные мультиплексоры J,,-3n, выходные мультиплексоры Ьц-b, входы двоичных разрядов и четных разрядов кода с иррациональным основанием первого слагаемого сумматора, входы двоичных разрядов и четных разрядов кода с иррациональным основанием второго слагаемого сумматора, входы нечетных разрядов кода с иррациональным основанием первого слагаемого сумматора, входы 8,,-8ц нечетных разрядов кода с иррациональным основанием второго слагаемого сумматора, прямые выходы триггров разрядов сумматора, выходы 10,- 10,-„разрядов суммы сумматора, с пер

... .. j t

вого по четвертый входы 11-14 задани режима сумматора и шина 15 сброса суматора.

Сумматор предназначен для сложени операндов (векторов), представленных в двоично-кодированной позиционной системе счисления с иррациональным основанием $2.

В этой системе счисления любое . число (вектор) представляется в виде .)()п-Ч...+х(42У + , +хаф)° М(1)

iВ связи с тем, что веса разрядов данного кода являются последовательностью степеней основания Ч

8л| 8 Н 4 2J2 2 if 1,

четные степени которой представляют веса разрядов двоичного кода, а нечет ные - веса разрядов двоичного кода,

зрад

умноженные на -у|2, то выражение (1) можно записать так

n-i JL1 п-2.

&±ч i-i J

2 +

-о

х;2

1/2

(2)

-

5

0

где величины принимают значения

x-,xje{0, jefl,3,5n-l

ie 0,2,4n-2. .

Первый член формулы (2) составляет сумму нечетных разрядов кода, а второй член - сумму четных разрядов кода с основанием т/2.

Особенностью такого изображения является то, что код с основанием -J используемый для записи числа единый и в то же время члены выражения (2) независимы друг от друга. Это позволяет при сложении двух операндов осуществлять параллельное и независимое сложение составных частей операндов. Если использовать операцию сжатия (опускание нулей) четных и нечетных разрядов, то при этом выражения для четных и нечетных разрядов примут

г.- ,

5 v . 7 у v 7

Z x, L , / ,

(3)

25

30

-

45

50

55

35

40

f

где i,j ,1,2,...,| - 1J.

Сжатию нечетных разрядов предшест-. вует их сдвиг вправо на один разряд. Для суммирования операндов, четные и нечетные разряды которых представлены выражением (3), используются обыкновенные двоичные сумматоры.

Входные мультиплексоры 34-3}, обеспечивают раздельное поступление в сумматор операндов в двоичном коде и в коде с иррациональным основанием т|2« Кроме того, с помощью мультиплексоров ц осуществляется сжатие информации операндов соответственно

четным и нечетным разрядам кода 2. Выходные мультиплексоры предназначены для выдачи результата суммы, выполнения формирования суммы в коде 4 путем операции расширения.

Сумматор может работать в двух режимах: . в режиме сложения операндов, представленных в коде с основанием -J, и в режиме суммирования при двоичном представлении операндов.

Параллельный накапливающий сумматор при сложении операндов в коде с иррациональным основанием | работает следующим образом.

Суммированию чисел предшествует подача импульса Сброс, который, поступая в шину 15, устанавливает все триггеры 1ч-1„ сумматора в состояние О. На входах 11 и 12 при этом должны присутствовать нулевые сигналы. После чего на входы сумма515787

тора подаются четные разряды первого

операнда (например, 1111), которые через входные мультиплексоры Ji|-3n поступят на вторые входы элементов

(1 НЕРАВНОЗНАЧНОСТЬ. Все элементы 5 тех разрядов, в которых слагаемое содержит 1, устанавливаются в состояние 1. При этом триггеры 1,, - 1п остаются в прежнем состоянии, не- JQ смотря на присутствие 1 на их счетных входах. Триггеры t,,-1h изменяют свое состояние в том случае, когда элементы 2,-2п НЕРАВНОЗНАЧНОСТЬ соответствующих разрядов переходят j из состояния 1 в состояние О. При следующем такте сигналы, присутствующие на входах 54-5ц сумматора, снимаются. Элементы НЕРАВНОЗНАЧНОСТЬ, находящиеся в состоянии 20 1, переходят в состояние О. Триггеры 1,|-1и соответствующих разрядов переходят в состояние 1. Четные разряды в сжатом виде первого операнда (,1111) будут записаны в триг- 25 геры сумматора. Вследствие того, что прямые выходы триггеров сумматора приложены к первым входам элементов 25 24, 23 22 НЕРАВНОЗНАЧНОСТЬ, то на их выходах, а следовательно, и зд счетных входах триггеров 15, 1$, 13, 1fc будут присутствовать единичные сигналы. Для окончательной подготовки сумматора к приему четных разрядов

второго операнда необходимо на входы 11 и 12 подать соответственно единич- $ ный и нулевой сигналы. Тогда четные разряды второго операнда, приложенные ко входам f, в сжатом виде (например, 1101), через входные мультиплексоры 3 f-J л поступят на вторые входы элементов 2,,-2 и вызовут изменение состояний тех элементов НЕРАВНОЗНАЧНОСТЬ, для которых четный разряд второго слагаемого содержит

40

55

87

5 JQ j 20 25 зд

$

0

40

5

106

Благодаря этим переключениям осуществляется предварительный перенос информации от младших разрядов к старшим. Снятие второго слагаемого вызывает аналогичные переключения, в результате которых триггеры )j сумматора устанавливаются в состояния, соответствующие записи на триггерах 1r-14 cvMMbi (11100) четных разрядов операндов с основанием . Поскольку прямые выходы триггеров 1 с- Ц 1 4 1v прдсоединены ко вторым информационным входам выходных мультиплексоров 4, 47, 4 j-, 4Э, 4|, при наличии на входах 13 и 14 соответственно единичного и нулевого сигналов, осуществится расширение двоичной информации 11100 в информацию 101010000 кода с основанием . Таким образом, на выходах 10, 107, , Ю3, 10, будет присутствовать код, соответствующий сумме 101010000 четных разрядов операндов с основанием -у2 Аналогичным образом происходит сложение нечетных разрядов (например,1110 и 0101) первого и второго операндов, представленных в сжатом виде. При этом нечетные разряды первого операнда поступают на входы 7,(-7п, а затем ко входам , прилагаются нечетные разряды второго операнда. Процесс суммирования идентичен ранее рассмотренному. Полученный результат суммы нечетных разрядов (10011) присутствует на третьих информационных входах выходных мультиплексоров , 4g , 4g , 44 , 1 и при наличии на входах 13 и 14 соответственно нулевого и единичного сигналов поступит на выходы указанных выходных мультиплексоров. Таким образом, на выходах , 108, 106, 104, Юг будут присутствовать нечетные разряды (ЮООООЮЮ) суммы кода . С учетом сЛормированных четных и нечетных разрядов кода получим на выходах Ю,0-Ю( , окончательный результат 110Ю110Ю. На этом заканчивается первый режим работы.

Второй режим работы сумматора полностью совпадает с суммированием четных разрядов операндов, представленных в кодах с иррациональным основанием , Для его обеспечения первый и второй двоичные операнды подают соответственно на входы ,, и ,, сумматора, а ко входам 11 и 12 прилагают последовательно во времени сигналы соответствующие О, , О. Приложение ко входам 13 и 14

нулевых сигналов позволяет получить на выходах параллельного накапливающего сумматора результат сложения двоичных операндов.

Формула изобретения

Параллельный накапливающий сумматор по авт. св. № 1166099, отличающийся тем, что, с целью . расширения функциональных возможностей за счет сложения чисел с иррациональным основанием , он содержит п входных мультиплексоров и 2п выходных мультиплексоров, причем выходы входных мультиплексоров соединены с вторыми входами элементов НЕРАВНОЗНАЧНОСТЬ соответствующих разрядов сумматора, первый и второй управляющие входы каждого входного мультиплексора соединены соответственно с первым и вторым входами1задания режима сумматора, входы двоичных разрядов и четных разрядов кода с иррациональ- ным основанием первого слагаемого сумматора соединены с первыми информационными входами соответствующих входных мультиплексоров, вторые информационные входы которых соединены с входами соответствующих двоичных разрядов и четных разрядов кода с иррациональным основанием второго слагаемого сумматора, входы нечетных разря

0

j 25 0.

30

дов кода с иррациональным основанием первого слагаемого сумматора соединены с третьими информационными входами соответствующих входных мультиплексоров, четвертые информационные входы которых соединены с входами соответствующих нечетных разрядов кода с иррациональным основанием второго слагаемого сумматора, первые и вторые управляющие входы каждого выходного мультиплексора соединены соответственно с третьим и четвертым входами задания режима сумматора, первые информационные входы п младших выходных мультиплексоров соединены с прямыми выходами триггеров соответствующих разрядов сумматора, первые информационные входы п старших выходных мультиплексоров соединены с шиной нулевого потенциала сумматора, второй информационный вход (21-1)-го выходного мультиплексора и третий информационный вход 2i-ro выходного мультиплексора объединены и подсоединены к прямому выходу триггера 1-го разряда сумматора, второй информационный вход 21-го выходного мультиплексора и третий информационный вход (21-1)-го выходного мультиплексора соединены с шиной нулевого потенциала сумматора, выходы выходных мультиплексоров являются выходами соответствующих разрядов суммы сумматора.

Авторы

Даты

1990-07-15—Публикация

1988-09-29—Подача