Изобретение относится к вычислительной технике и может найти применение в системах, используюгцих изменяемую дисциплину обслуживания.

Цель изобретения - повышение быстродействия устройства.

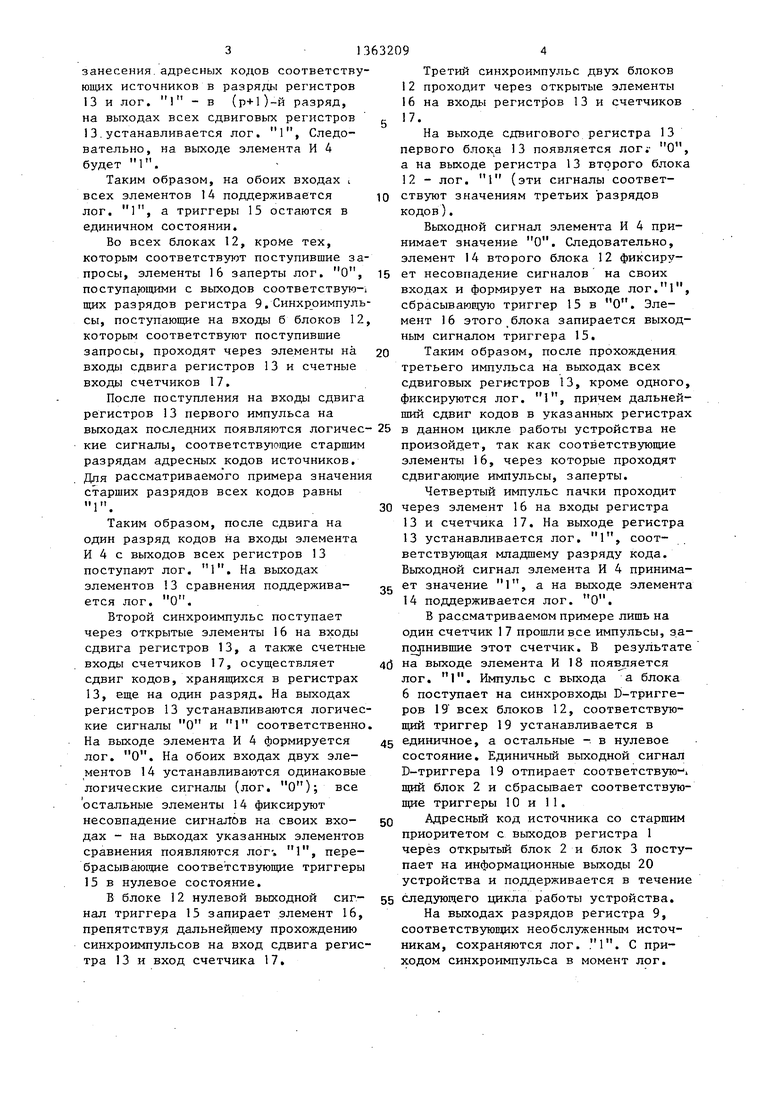

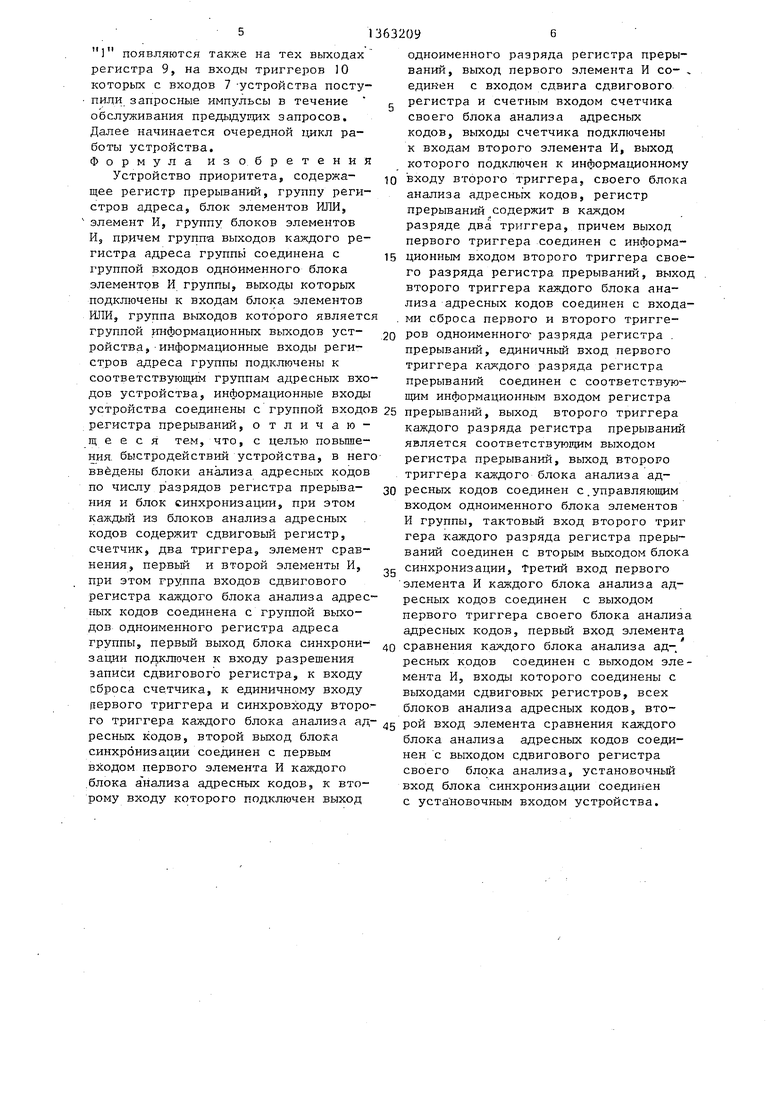

На фиг,1 приведена структурная схема устройства; на фиг,2 - структурная схема блока синхронизации.

Устройство содержит регистры 1 адреса, блоки 2 элементов И, блок 3 элементов ИЛИ,элемент И 4, группы адресных входов 5 устройства, блок 6 синхронизации, информационные входы 7 устройства, установочный вход 8 устройства, регистр 9 прерываний, содержащий в каждом разряде триггеры 10,11; устройство содержит также

блоки 12 анализа адресных кодов, каж- 20 блока 6 поступают синхроимпульсы.

дый из которых содержит сдвиговый регистр 13, элемент 14 сравнения, триггер 15, элемент И 16, счетчик 17, элемент И 18, триггер 19; устройство содержит информационные выходы 20 устройства.

Блок; синхронизации (фиг.2) содержит генератор 21 импульсов,,элемент И 22, счетчик 23, элемент И 24, элемент 25 задержки, элемент НЕ 26, элементы И 27, 28, элемент И1Ш 29.

Устройство работает следующим образом.

Запросы на обслуживание от источников фиксируются регистром 9 по индивидуальным для ка кдого источника входам 7. В регистрах хранятся адреса источников в порядке, обратном присвоенным им приоритетам.

Поиск заявки с наибольшим приоритетом осуществляется циклически с помощью блоков 12, тактируемых синхроимпульсами блока 6. С этой целью производится сравнение адресных кодо источников, зафиксировавших свои заявки на обслуживание в регистре 9, причем предпочтение отдается заявке источника с наименьшим адресным кодом. Сравнение адресных кодов осуществляется путем преобразования параллельных адресных кодов соответствующих источников в последовательный код с одновременным сравнением одноименных бит указанных кодов.

В результате сравнения адресных кодов источников, зафиксировавших свои заявки в регистре 9, определяется источник с наибольшим приоритетом при этом на выходе триггера 19 соответствуюп|его блока 12 формируется лог. 1, поступающая на соответствующий блок 2 и па вход сброса соответ- ствующего разряда регистра 9. В результате адресный источник через блоки 2 и 3 поступает на информационные выходы 20 устройства, а разряд регистра 9 обнуляется. В течение

следующего цикла работы, определяемого периодом следования синхроим-у пульсов, иа выходе блока 6 поиск заявки с более высоким приоритетом совмещается во времени с выдачей на

выходы 20 устройства адреса источника.

Блоки 12 работают следующим образом.

На входы а и б блоков I2 с выходов

На выходе б блока 6 количество импулсов в одной пачке импульсной последовательности равно количеству бит, необходимых для представления в дво25 ичной форме наибольшего кода адреса. Подготовка блока 12 к работе осуществляется синхроимпульсом (поступающим на вход а блока 12, который- сбрасывает счетчик 17, устанавливает

30. триггер 24 в единичное состояние и заносит адресный код источника, по- ступающий с выходов регистра 1, в . сдвиговьй регистр 13. Сдвиговьй регистр 13 является (р+1)-разрядным,

35 причем адресный код заносится в разряды 1,2, - , р, а в (р+1)-раз- ряд заносится лог. VI, поступающая на выход регистра, в качестве которого принят единичный выход (р+1)-го

40 разряда.

Пусть на входы 7 устройства поступили запросные импульсы, перебросившие соответствующие триггеры 10 в единичное состояние. Синхроимпульс.

45 блока 6, поступающий на синхровход регистра 9 прерываний, перебрасывает соответствующие триггеры 11 в единичное состояние, остальные триггеры 11 находятся в нулевом состоянии.

50 Пусть адресные коды источников заявок с номерами т, S и f в двоичном представлении имеют значения: 1001, 1010 и 1101, при этом приоритеты на обслуживание источников рас55 пределяются в порядке., обратном значениям кодов адресов.

Элементы 14 сравнения выдают импульсы в моменты фиксации несовпадения сигналов на их -входах. После

занесения, адресных кодов соответствующих источников в разряды регистров 13 и лог. - в (р+1)-й разряд, на выходах всех сдвиговых регистров 13.устанавливается лог, 1, Следовательно, на выходе элемента И 4 будет 1.

Таким образом, на обоих входах i всех элементов 14 поддерживается лог. 1, а триггеры 15 остаются в единичном состоянии.

Во всех блоках 12, кроме тех, которым соответствуют поступившие запросы, элементы 16 заперты лог. О, поступаю1цими с выходов соответствую- щих разрядов регистра 9.Синхроимпульсы, поступающие на входы б блоков 12, которым соответствуют поступившие запросы, проходят через элементы на входы сдвига регистров 13 и счетные входы счетчиков 17.

После поступления на входы сдвига регистров 13 первого импульса на

выходах последних появляются логичес- 25 в данном цикле работы устройства не

кие сигналы, соответствутотцие старшим разрядам адресных кодов источников. Для рассматриваемого примера значени

старших разрядов всех кодов равны

I111t

i .

Таким образом, после сдвига на один разряд кодов на входы элемента И 4 с выходов всех регистров 13 поступают лог. 1. На выходах элементов 13 сравнения поддерживается лог. О.

Второй синхроимпульс поступает через открытые элементы 16 на входы сдвига регистров 13, а также счетные входы счетчиков 17, осуществляет сдвиг кодов, хранящихся в регистрах 13, еще на один разряд. На выходах регистров 13 устанавливаются логические сигналы О и 1 соответственно На выходе элемента И 4 формируется лог. О. На обоих входах двух элементов 14 устанавливаются одинаковые логические сигналы (лог. О); все остальные элементы 14 фиксируют несовпадение сигналов на своих входах - на выходах указанных элементов сравнения появляются лог-. 1, пере- брасываюш не соответствующие триггеры 15 в нулевое состояние.

В блоке 12 нулевой выходной сигнал триггера 15 запирает элемент 16, препятствуя дальнейшему прохождению синхроимпульсов на вход сдвига регистра 13 и вход счетчика 17.

Третий синхроимпульс двух блоков 12 проходит через открытые элементы 16 на входы регистров 13 и счетчиков

7На выходе сдвигового регистра 13

первого блокд 13 появляется лог;- О, а на выходе регистра 13 второго блока 12 - лог. I (эти сигналы соответствуют значениям третьих разрядов кодов).

Выходной сигнал элемента И 4 принимает значение О. Следовательно, элемент 14 второго блока 12 фиксирует несовпадение сигналов на своих входах и формирует на выходе лог. М, сбрасывающую триггер 15 в О. Элемент 16 этого блока запирается выходным сигналом триггера 15.

Таким образом, после прохождения третьего импульса на выходах всех сдвиговых регистров 13, кроме одного, фиксируются лог. 1, причем дальнейший сдвиг кодов в указанных регистрах

5

(3

произойдет, так как соответствующие элементы 16, через которые проходят сдвигающие импульсы, заперты.

Четвертый импульс пачки проходит 0 через элемент 16 на входы регистра 13 и счетчика 17. На выходе регистра

13устанавливается лог. 1, соответствующая младшему разряду кода. Выходной сигнал элемента И 4 принимает значение 1, а на выходе элемента

14поддерживается лог. О.

В рассматриваемом примере лишь на один счетчик 1 7 прошли все импульсы, з.а- по Енивщие этот счетчик. В результате на выходе элемента И 18 появляется лог. 1. Импульс с выхода а блока 6 поступает на синхровходы D-тригге- ров 19 всех блоков 12, соответствующий триггер 19 устанавливается в

5 единичное, а остальные -. в нулевое состояние, Единичньш выходной сигнал D-триггера 19 отпирает соответствую щий блок 2 и сбрасывает соответствующие триггеры 10 и 11.

0 Адресный код источника со старшим приоритетом с выходов регистра 1 через открытьй блок 2 и блок 3 поступает на информационные выходы 20 устройства и поддерживается в течение

5 следующего цикла работы устройства.

На выходах разрядов регистра 9, соответствуюп их необслуженным источникам, сохраняются лог. 1. С приходом синхроимпульса в момент лог.

1 появляются также на тех выходах регистра 9, на входы триггеров 10 которых с входов 7 -устройства поступили, запросные импульсы в течение обслуживания предыдущих запросов. Далее начинается очередной цикл работы устройства. Формула изо, бретения

Устройство приоритета, содержащее регистр прерываний, группу регистров адреса, блок элементов ИЛИ,

элемент И, группу блоков элементов И, причем группа выходов каждого регистра адреса группы соединена с группой входов одноименного блока элементов И группы, выходы которых подключены к входам блока элементов ИЛИ, Группа выходов которого является группой ршформационных выходов устройства, -информационные входы регистров адреса группы подключены к соответствующим группам адресных вхо-

20 ров одноименного- разряда регистра . прерываний, единичный вход первого триггера каждого разряда регистра прерываний соединен с соответствующим информационным входом регистра

дов устройства, информационные входы устройства соединены с группой входов 25 прерываний, выход второго триггера регистра прерываний, отличаю- каждого разряда регистра прерываний щ е е с я тем, что, с целью повьппе- является соответствующим выходом ния, быстродейств1ш устройства, в него введены блоки анализа адресных кодов по числу разрядов регистра прерывания и блок синхронизации, при этом каждый из блоков анализа адресных кодов содержит сдвиговый регистр, счетчик, два триггера, элемент сравнения, первьш и второй элементы И, при этом группа входов сдвигового регистра каждого блока анализа адресных кодов соединена с группой выходов одноименного регистра адреса

регистра прерывании, выход второго , триггера каждого блока анализа ад30 ресных кодов соединен с.управляющим входом одноименного блока элементов И группы, тактовьй вход второго триг гера каждого разряда регистра прерываний соединен с вторым выходом блока

2g синхронизации. Третий вход первого элемента И каждого блока анализа адресных кодов соединен с выходом первого триггера своего блока анализа адресных кодов, первьй вход элемента

группы, первый выход блока синхрони- Q сравнения каждого блока анализа ад-/

зации подключен к входу разрешения записи сдвигового регистра, к входу сброса счетчика, к единичному входу liepBoro триггера и синхровходу второго триггера каждого блока анализа ад- 45 рой вход элемента сравнения каждого

ресных кодов, второй выход блока синхронизации соединен с первым входом первого элемента И каждого .блока а нализа адресных кодов, к второму входу которого подключен выход

блока анализа адресных кодов соединен с выходом сдвигового регистра своего блока анализа, установочньй вход блока синхронизации соединен с установочным входом устройства.

одноименного разряда регистра прерываний, выход первого элемента И со- един-ен с входом сдвига сдвигового (- регистра и счетным входом счетчика своего блока анализа адресных кодов, выходы счетчика подключены к входам второго элемента И, выход которого подключен к информационному

0 входу второго триггера, своего блока анализа адресных кодов, регистр прерываний содержит в каждом разряде два триггера, причем выход первого триггера соединен с информа5 ционным входом второго триггера своего разряда регистра прерываний, выход второго триггера каждого блока анализа адресных кодов соединен с входа- . ми сброса первого и второго тригге0 ров одноименного- разряда регистра . прерываний, единичный вход первого триггера каждого разряда регистра прерываний соединен с соответствующим информационным входом регистра

5 прерываний, выход второго триггера каждого разряда регистра прерываний является соответствующим выходом

25 прерываний, выход второго триггера каждого разряда регистра прерываний является соответствующим выходом

регистра прерывании, выход второго , триггера каждого блока анализа ад30 ресных кодов соединен с.управляющим входом одноименного блока элементов И группы, тактовьй вход второго триг гера каждого разряда регистра прерываний соединен с вторым выходом блока

2g синхронизации. Третий вход первого элемента И каждого блока анализа адресных кодов соединен с выходом первого триггера своего блока анализа адресных кодов, первьй вход элемента

Q сравнения каждого блока анализа ад-/

ресных кодов соединен с выходом элемента И, входы которого соединены с выходами сдвиговых регистров, всех блоков анализа адресных кодов, втоблока анализа адресных кодов соединен с выходом сдвигового регистра своего блока анализа, установочньй вход блока синхронизации соединен с установочным входом устройства.

2Г - 22 5лок синхронизации

Фиг. г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с объектами управления | 1986 |

|

SU1401469A1 |

| Многопроцессорная система | 1989 |

|

SU1686455A1 |

| Микропрограммное устройство управления | 1989 |

|

SU1633402A1 |

| Устройство для сопряжения цифровых вычислительных машин с каналами связи | 1985 |

|

SU1287171A1 |

| Устройство управления доступом к памяти для обмена массивами данных в многопроцессорной системе | 1989 |

|

SU1633418A1 |

| Устройство для сопряжения вычислительной машины с каналом связи | 1985 |

|

SU1291994A1 |

| Устройство для контроля электропотребления | 1988 |

|

SU1566371A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1990 |

|

SU1728867A1 |

| Устройство для обслуживания запросов | 1988 |

|

SU1571588A1 |

| Устройство для контроля управляющей вычислительной машины | 1988 |

|

SU1569835A1 |

Изобретение относится к вычислительной технике и может найти применение в системах, использз щих изменяемую дисциплину обслуживания. Цель изобретения - повышение быстродействия устройства.- Устройство приоритета отличается от известного тем, что в него введены блоки анали-г за адресных кодов по числу разрядов регистра прерываний и блок синхронизации, при этом кажд.ьй из блоков анализа адресньс. кодов содержит сдвиговый регистр, счетчик, два триггера, элемент сравнения и два элемента И. В устройстве сокращается время поиска запросов со старшим .приоритетом. 2 ил. Оо о. ОО to

| Устройство приоритета | 1976 |

|

SU600558A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство приоритета | 1981 |

|

SU1001102A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-12-30—Публикация

1986-07-24—Подача