СЛ

05

со

00

оо

СЛ

жит блок 1 памяти, коммутатор 2, триггер 3, регистр прерываний , триггеры 9, Ю и 13. Каждой программе обработки прерываний соответствует один пыход блока 1 памяти, на котором при обращениях к программе обработки прерываний формируются импульсы. Эти импульсы через коммутатор 2 могут поступать на вход установки в единицу триггера 3 и вызвать появление на его выходе выходного сигнала ошибки устройства, Прохождение импульсов через коммутатор 2 блокируется записью в регистр прерываний k соответствующего .кода прерывания, запись которого выполняется программно в три этапа, что исключает случайные записи. На первом этапе устанавливается в единицу триггер 10, на третьем этапе при установленных в единицу триггерах 9 и 10 производится код прерывания.заносится в регистр k,

после чего триггеры 9 и 10 автоматически сбрасываются в ноль. Триггер 13 формирует сигнал сброса в ноль регистра прерываний k после окончания выполнения программы обработки прерываний. 1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| Устройство для сопряжения вычислительной машины с линиями связи | 1985 |

|

SU1262512A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Устройство для отладки программ | 1988 |

|

SU1624461A1 |

| Устройство для контроля управляющей вычислительной машины | 1987 |

|

SU1464163A1 |

| Устройство для управления вводом-выводом | 1989 |

|

SU1735859A1 |

| Устройство для распаковки команд | 1984 |

|

SU1196865A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано в вычислительных устройствах, к работе которых предъявляются требования повышенной надежности. Цель изобретения - повышение достоверности контроля управляющей вычислительной машины при обработке вложенных прерываний. Устройство содержит блок 1 памяти, коммутатор 2, триггер 3, регистр 4 прерываний, триггеры 9, 10 и 13. Каждой программе обработки прерываний соответствует один выход блока 1 памяти, на котором при обращениях к программе обработки прерываний формируются импульсы. Эти импульсы через коммутатор 2 могут поступать на вход установки в единицу триггера 3 и вызвать появление на его выходе выходного сигнала ошибки устройства. Прохождение импульсов через коммутатор 2 блокируется записью в регистр прерываний 4 соответствующего кода прерывания, запись которого выполняется программно в три этапа, что исключает случайные записи. На первом этапе устанавливается в единицу триггер 10, на третьем этапе при установленных в единицу триггерах 9 и 10 код прерывания заносится в регистр 4, после чего триггеры 9 и 10 автоматически сбрасываются в ноль. Триггер 13 формирует сигнал сброса в ноль регистра прерываний 4 после окончания выполнения программы обработки прерываний. 1 ил.

Изобретение относится к цифровой вычислительной 1ехнике и может быть использовано в вычислительных устройствах, к работе которых предъявляются требования повышенной надежности,

Цель изобретения - повышение досто верности контроля управляющей вычислительной машины при обработке вложенных прерываний.

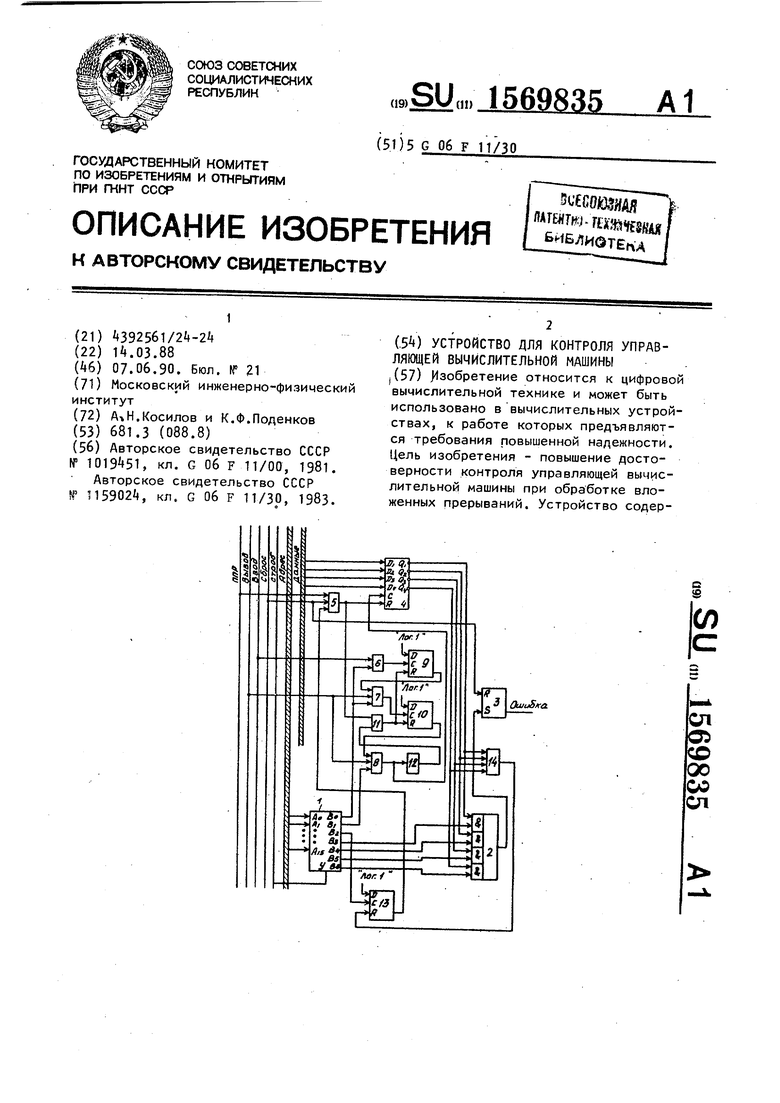

На чертеже представлена схема устройства для контроля управляющей вычислительной машины.

Устройство содержит блок 1 памяти, коммутатор 23 первый триггер 3, регистр 4 прерываний, первый элемент ИЛИ 5, первый элемент И 6, второй элемент И 7 третий элемент И 8, третий триггер 9, четвертый триггер 10, второй элемент ИЛИ 11, элемент 12 задержки, второй триггер 13 четвертый элемент И 1k„

Устройство работает следующим образом.

Каждой программе обработки прерываний соответствует один выход, начиная с четвертого и выше, блока 1 памяти и один разряд регистра прерываний. Код прерывания - код, загружаемый в регистр 4 прерываний перед запуском программы обработки прерывания. Он устанавливает в 1 COOT- ветствующий запускаемой программе разряд регистра прерываний и в О Е)се остальные его разряды. Программное обеспечение вычислительной машины, в составе которой используется предлагаемое устройство, состоит из программ обработки прерываний, число которых не превышает разрядности регистра А прерываний, и программы

)

5 0

5 Q

5

монитора. Программа-монитор (монитор) принимает запросы не прерывание, передает управление требуемой программе обработки прерывания, выполняет все необходимые действия по сохранению информации, требуемой для возврата в прерванную программу, восстанавливает выполнение прерванной программы после окончания прервавшей ее программы при вложенных прерываниях. Адресные входы устройства подключены к шине адреса вычислительной машины, в составе которой используется предлагаемое устройство. Каждому адресу (группе адресов) основной памяти вычислительной машины, в которой записаны монитор и программы обработки прерываний,соответствует адрес блока 1 памяти.Два адреса блока 1 памяти COOT ветствуют адресам внешних устройств ВУ 1 и ВУ 2.Активный сигнал на стробируюшем входе блока 1 памяти подтверждает истинность адреса на его адресных входах.При обращениях к адресам основной памяти вычислительной машины или к адресам внешних устройств на адресных входах блока 1 памяти устанавливается адрес,по которому производится обращение,а на строби- рующий вход поступает активный сигнал,

Блок 1 памяти запрограммирован следующим образом. На его первом . выходе появляется уровень Лог. 1 при обращении к адресу ВУ 1. Во всех других случаях на первом выходе блока 1 памяти,установлен уровень Лог. О. На втором выходе блока 1 памяти появляется уровень Лог. 1 при обращениях к адресу ВУ 2. Во всех остальных случаях на втором выходе блока 1 памяти установлен уроблока 1 памяти появляется уровень Лог. 1 при обращениях по адресам точек входа в монитор. Во всех других случаях на третьем выходе блока 1 памяти установлен уровень Лог. О. На четвертом выходе блока 1 памяти появляется уровень Лог. 1 при обращениях по любому адресу соответствующей ему программы обработки прерываний. Во всех остальных случаях на четвертом выходе блока 1 памяти установлен уровень Лог. О. Выходы блока 1 памяти, начиная с пятого и выше, работают при обращениях по адресам соответствующих им программ обработки прерываний аналогично его четвертому выходу. В начальный момент времени сигналом на входе сброса устройства сбрасываются в О регистр 4 прерываний, триггеры 3, 9 и 10. На инверсных выходах регистра 4 прерываний при этом устанавливают10

пускаемой программы обработки прерываний, т.е. разрешает ее выполнение. Обращение к другим программам обработки прерываний остается при этом запрещенным. Как только на инверсном выходе регистра прерываний 4 появляется уровень Лог. О, такой уровень установится на выходе элемента И 14. После этого возможна запись информации в триггер 13 по входу данных. В устройстве предусмотрены меры для исключениг случайной записи в регистр 4 прерываний.

Запись в последний производится в три этапа о Сначала необходимо выполнить ввод с адреса ВУ 1. Ори этом в триггер 9 будет записана Лог. 1. 20 Затем необходимо выполнить вывод по адресу ВУ 1. При этом, если в триггере 9 записана Лог. 1, в триггер 10 также будет записана Лог. 1.

15

Во время выполнения операций ввода ся уровни Лог. 1, на выходе элемен- 25 и вывода по адресу ВУ 1 вводимая ин- та И 14 появляется уровень Лоп. 1, формация не имеет никакого смысла,

а выводимая никуда не записывается. На третьем этапе выполняют вывод кода прерывания по адресу ВУ 2. При этом 30 на выходе элемента И 8 будет сформирован сигнал синхронизации регистра

сбрасывающий в О триггер 13. Выполняется вход в монитор, после чего выделительная машина переходит в состояние ожидания запроса на прерывание. В это время запрещены обращения по любым адресам, кроме адресов монитора. Если в результате ошибки адресации произойдет обращение к одной из программ обработки прерываний, то ьсрвый импульс на выходе блока 1 памяти, соответствующем программе, к которой произведено обращение, через коммутатор 2 поступит на вход установ- ки в 1 триггера 3, на выходе которого при этом сформируется сигнал ошибки устройства. После прихода за- пооса на прерывание монитор определяет, какой программе обработки должно быть передано управление, заносит в регистр 4 прерываний соответствующий код прерывания и передает управление программе обработки прерываний. Пос- Л -1 занесения кода прерывания в регистр

35

4 прерываний, вызывающий запись в него кода прерывания. При нарушении последовательности этапов записи в регистр 4 прерываний или отсутствии хотя бы одного из них сигнал синхронизации на выходе элемента И 8 не будет сформирован. Сигнал синхронизации регистра 4 прерываний задержилп вается с помощь/о элемента 12 задержки на время, достаточное для Записи данных в регистр 4 прерываний, после чего через элемент ИЛИ 11 он сбрасывает в О триггеры 9 и 10. Теперь

45 для записи данных в регистр 4 прерываний необходимо вновь повторить все три этапа. При поступлении на вложенное прерывание управление вновь передается монитору, причем сигналом под4 прерываний на инверсном выходе пос- 50 тверждения прерывания (ППР), означающим начало обработки поступившего запроса, через элемент ИЛИ 5 сбрасывается в О регистр 4 прерываний. Т.е. сигнал ППР запрещает обращения

пзднего, соответствующем запускаемой ;V.грамме, устанавливается уровень Лог. О, а на остальных выходах - уровни Лог. 1. Такое состояние выходов регистра 4 прерываний блокиру- ко всем программам, кроме монитора,

Монитор сохраняет всю необходимую информацию для возврата в прерванную программу, определяет, какой программе обработки прерываний необходимо

ет прохождение импульсов с выхода блока 1 памяти, соответствующего запускаемой программе, через коммутатор 2 на вход установки в 1 триг0

пускаемой программы обработки прерываний, т.е. разрешает ее выполнение. Обращение к другим программам обработки прерываний остается при этом запрещенным. Как только на инверсном выходе регистра прерываний 4 появляется уровень Лог. О, такой уровень установится на выходе элемента И 14. После этого возможна запись информации в триггер 13 по входу данных. В устройстве предусмотрены меры для исключениг случайной записи в регистр 4 прерываний.

Запись в последний производится в три этапа о Сначала необходимо выполнить ввод с адреса ВУ 1. Ори этом в триггер 9 будет записана Лог. 1. 0 Затем необходимо выполнить вывод по адресу ВУ 1. При этом, если в триггере 9 записана Лог. 1, в триггер 10 также будет записана Лог. 1.

5

4 прерываний, вызывающий запись в него кода прерывания. При нарушении последовательности этапов записи в регистр 4 прерываний или отсутствии хотя бы одного из них сигнал синхронизации на выходе элемента И 8 не будет сформирован. Сигнал синхронизации регистра 4 прерываний задерживается с помощь/о элемента 12 задержки на время, достаточное для Записи данных в регистр 4 прерываний, после чего через элемент ИЛИ 11 он сбрасывает в О триггеры 9 и 10. Теперь

для записи данных в регистр 4 прерываний необходимо вновь повторить все три этапа. При поступлении на вложенное прерывание управление вновь переается монитору, причем сигналом подко всем программам, кроме монитора,

Монитор сохраняет всю необходимую информацию для возврата в прерванную программу, определяет, какой программе обработки прерываний необходимо

передать управление, загружает в регистр k прерываний соответствующий код прерывания и передает управление требуемой программе обработки прерываний. После окончания выполнения последней управление передается монитору. При этом формируется сигнал на входе синхронизации триггера 13, в этот триггер записывается Лог. 1, которая через элемент ИЛИ 5 сбрасывает в О регистр 4 прерываний, что запрещает обращения ко всем программам, кроме монитора. При установке инверсных выходов регистра прерываний в единичные состояния на выходе элемента И k появляется уровень Лог. 1, сбрасывающий в О триггер 13 и удерживающийся на входе сброса в О этого триггера до выхода из монитора (точнее до -занесения кода прерывания в регистр k прерываний) . Таким образом, обеспечивается формирование только одного импульса

10

са устройства для подключения к одноименному выходу контролируемой вычислительной машины, выход первого триггера является выходом ошибки устройства, вход сброса регистра прерываний соединен с выходом первого элемента ИЛИ, отличающееся тем, что, с целью повышения достоверности контроля управляющей вычислительной машины при обработке вложенных прерываний, оно содержит четыре элемента И, три триггера, второй элемент ИЛИ и элемент задержки, причем первый разряд выхода блока памяти соединен с первыми входами первого и второго элементов И, второй разряд выхода блока памяти соединен с первым входом третьего элемента И, третий разряд выхода блока памяти соединен с входом синхронизации второго триггера, инверсные выходы разрядов регистра прерываний соединены с группой входов четвертого элемента И, ин15

20

30

сброса регистра прерываний при вхо 25 формационные входы регистра прерыва- де в монитор после окончания выполнения программы обработки прерывания. Монитор проверяет, не было ли прерывание, обработка которого закончилась, вложенным. Если было, восстанавливает выполнение прерванной программы, загрузив предварительно соответствующий код прерываний в регистр Ц прерываний. Если прерывание, обработка которого закончилась, не было вложен ным, монитор переходит к ожиданию очередного запроса на прерывание.

35

нии являются входами кода прерывания устройства для подключения к выходу данных контролируемой вычислительной машины, вход синхронизации регистра прерываний соединен с выходом третьего элемента И, выход которого через элемент задержки соединен с первым входом второго элемента ИЛИ, второй вход первого элемента ИЛИ соединен с входом подтверждения прерывания устройства для подключения к одноименному выходу контролируемой вычислительной машины, выход второго триггера соединен с третьим входом первого элемента ИЛИ, выход которого соединен с вторым входом второго элемента ИЛИ, выход которого соединен с входами сброса третьего и иетвертого триггеров, выход третьего триггера соединен

Формула изобретения

40

нии являются входами кода прерывания устройства для подключения к выходу данных контролируемой вычислительной машины, вход синхронизации регистра прерываний соединен с выходом третьего элемента И, выход которого через элемент задержки соединен с первым входом второго элемента ИЛИ, второй вход первого элемента ИЛИ соединен с входом подтверждения прерывания устройства для подключения к одноименному выходу контролируемой вычислительной машины, выход второго триггера соединен с третьим входом первого элемента ИЛИ, выход которого соединен с вторым входом второго элемента ИЛИ, выход которого соединен с входами сброса третьего и иетвертого триггеров, выход третьего триггера соединен

Устройство для контроля управляющей вычислительной машины, содержащее блок памяти, коммутатор, первый триггер, регистр прерываний, первый элемент ИЛИ, причем адресные и стро- с вторым входом второго элемента И,вы- бирующий входы блока памяти являются ход которого соединен с входом синхрони- адресными и стробирующим входами уст- .зации четвертого триггера , выход которого соединен с вторым входом третьего элемента И, третий вход которого и третий вход второго элемента И соединены с входом сигнала Вывод устройства для подключения к одноименному выходу контролируемой вычислительной машины, вход синхронизации третьего триггера соединен с выходом первого

прерываний, выход коммутатора соеди- элемента И, второй вход которого сое- нен с S-входом первого триггера, R- динен с входом сигнала Ввод устрой- вход которого и первый вход первого ства для подключения к одноименному элемента ИЛИ соединены с входом сбро- выходу контролируемой вычислительной

so-:

ройства для подключения к одноименным выходам контролируемой вычислительной машины, четыре старших разряда выхода блока памяти соединены с первой группой информационных входов коммутатора, вторая группа информационных входов которого соединена с инверсными выходами разрядов регистра

л- 55

10

5698358

са устройства для подключения к одноименному выходу контролируемой вычислительной машины, выход первого триггера является выходом ошибки устройства, вход сброса регистра прерываний соединен с выходом первого элемента ИЛИ, отличающееся тем, что, с целью повышения достоверности контроля управляющей вычислительной машины при обработке вложенных прерываний, оно содержит четыре элемента И, три триггера, второй элемент ИЛИ и элемент задержки, причем первый разряд выхода блока памяти соединен с первыми входами первого и второго элементов И, второй разряд выхода блока памяти соединен с первым входом третьего элемента И, третий разряд выхода блока памяти соединен с входом синхронизации второго триггера, инверсные выходы разрядов регистра прерываний соединены с группой входов четвертого элемента И, ин15

20

0

5 формационные входы регистра прерыва-

5

0

нии являются входами кода прерывания устройства для подключения к выходу данных контролируемой вычислительной машины, вход синхронизации регистра прерываний соединен с выходом третьего элемента И, выход которого через элемент задержки соединен с первым входом второго элемента ИЛИ, второй вход первого элемента ИЛИ соединен с входом подтверждения прерывания устройства для подключения к одноименному выходу контролируемой вычислительной машины, выход второго триггера соединен с третьим входом первого элемента ИЛИ, выход которого соединен с вторым входом второго элемента ИЛИ, выход которого соединен с входами сброса третьего и иетвертого триггеров, выход третьего триггера соединен

с вторым входом второго элемента И,вы- ход которого соединен с входом синхрони- .зации четвертого триггера , выход которого соединен с вторым входом третьего элемента И, третий вход которого и третий вход второго элемента И соединены с входом сигнала Вывод устройства для подключения к одноименному выходу контролируемой вычислительной машины, вход синхронизации третьего триггера соединен с выходом первого

с х .з

so-:

91569835ю

машины, выход четвертого элемента И третьего и четвертого триггеров подсоединен с входом сброса второго триг- ключены к шине единичного потенциала гера, информационные входы второго, устройства.

| Устройство для контроля электронной вычислительной машины | 1981 |

|

SU1019451A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-06-07—Публикация

1988-03-14—Подача