По сигналу Запись на входе 17 разрешения записи устройства в счетчик 5 записывается адрес канала устройства. С выхода счетчика 5 адрес , канала поступает на входы адреса блока 4 оперативной памяти и управле1

10

5

20

ния коммутатора 2. После задержки t определяемой элементом 7 задержки, сигнал записи поступает на входы установки S триггера 9 и разрешения записи блока 4 оперативной памяти и вызывает установку триггера 9 в единичное состояние и запись цифровой :информа.ции, поступающей на входы 15 устройства, в ячейки памяти блЬка 4, В результате на его выходах появляется цифровая информация, которая далее поступает на входы цифроаналогового преобразователя 3. По истечении времени t на выходе цифроаналогового преобразователя 3 устанавливается .аналоговая величина, соответствующая цифровой информации на входе 15 устройства, а по истечении времени ,с с момента установки триггера 9 в единичное состояние, которое определяется параметрами элемента 8 задержки, на входе разрешения коммутатора 2 появляется сигнал разрешения, который вызывает подключение соответствующего блока 1 аналоговой памяти к выходу . цифроаналогового преобразователя 3, после чего происходит собственно запись аналоговой информации в блок 1 аналоговой памяти, продолжающаяся до появления сигнала по истечении времени tj на выходе элемента 6 задержки, KOTopbrfi вызывает по очереди: обнуление триггера 9 и тем самым запирание ячеек памяти блока 4 оперативной памяти, обнуление элемента 8 задержки и тем самым выключение коммутатора 2 по входу разрещения, обнуление элемента 6 задержки. Задним фронтом

30

35

40

По сигналу включения регенерации на вхопе S второй триггер 10 устанавливается в единичное состояние и начинается процесс регенерации. При этом выходной сигнал триггера 10, поступающий на вход D непосредственно, а через логический элемент 13 ИСКЛЮЧАЮВДЕ ИЛИ на вход С триггера 9, устанавливает последний в единичное состояние, что вызывает появление сигнала на входе разрешения (выбор кристалла) блока 4 оперативной памяти, на выходе которого появляется цифровая информахщя, записанная в его ячейки памяти с нулевым адресом в. соответствии с сигналами, поступающими с выхода счетчика 5 на входы адреса блока 4 оперативной памяти и входы управления коммутатора 2, благодаря чему подготавливается включение канала коммутатора 2 с нулевым адресом

По истечении времени t элемента 8 задержки на вход разрешения коммутатора 2 поступает сигнал, по которому к выходу цифроаналогового преобразователя 3 подключается блок 1 аналоговой памяти с нулевым адресом. Начинается подзаряд запоминающего элемента блока t памяти. Время под - заряда t определяется элементом 6 заде;ржки и устанавливается сигналом, поступаюр им на его вход управления с триггера 10, так что t с t.

По истечении времени t j обнуляется триггер 9, что вызывает запирание ячеек памяти блока 4 оперативной памяти и коммутатора 2 по входу разрешения, а на выходе элемента 6 задержки устанавливается логический Ноль, что вызывает запуск одновибратора 11 сигналом с выхода логического инвертора 14, Передним фронтом сигнала с выхода одновибратора 11, подаваемого

выходного сигнала элемента 6 задержки 5 счетный вход счетчика 5, содержа- запускается одновибратор 11, передним ™e последнего нарапц вается на еди- фронтом которого обнуляется счетчик 5. ««ЦУ задним фронтом того же сигнала, подаваемого на вход С триггера 9 через логический элемент 13 ИСКЛО- По заднему фронту выходного сигналадд ЧАЮЩЕЕ ИЛИ, триггер 9 устанавливается

одновибратора 11 по истечении времени t процесс записи заканчивается, и устройство переходит в режим хранения. Время записи tj от начала импульса записи на входе 17 устро стна до установления аналоговой величины на выходе блока 1 аналоговой памяти

/55

в единичное состояние. С этого момента начинается регенера1щя аналоговой информации в канале с адресом 1. По окончании регенерации этого канала содержимое счетчика 5 опять наращивается на единицу, после чего производится регенерация в следующем канале. Таким образом будет происходить регенерация последовательно всех кана

ч

t «Г-г1 tjt

tg

10

5

20

,с 30

35

40

По сигналу включения регенерации на вхопе S второй триггер 10 устанавливается в единичное состояние и начинается процесс регенерации. При этом выходной сигнал триггера 10, поступающий на вход D непосредственно, а через логический элемент 13 ИСКЛЮЧАЮВДЕ ИЛИ на вход С триггера 9, устанавливает последний в единичное состояние, что вызывает появление сигнала на входе разрешения (выбор кристалла) блока 4 оперативной памяти, на выходе которого появляется цифровая информахщя, записанная в его ячейки памяти с нулевым адресом в. соответствии с сигналами, поступающими с выхода счетчика 5 на входы адреса блока 4 оперативной памяти и входы управления коммутатора 2, благодаря чему подготавливается включение канала коммутатора 2 с нулевым адресом

По истечении времени t элемента 8 задержки на вход разрешения коммутатора 2 поступает сигнал, по которому к выходу цифроаналогового преобразователя 3 подключается блок 1 аналоговой памяти с нулевым адресом. Начинается подзаряд запоминающего элемента блока t памяти. Время под - заряда t определяется элементом 6 заде;ржки и устанавливается сигналом, поступаюр им на его вход управления с триггера 10, так что t с t.

По истечении времени t j обнуляется триггер 9, что вызывает запирание ячеек памяти блока 4 оперативной памяти и коммутатора 2 по входу разрешения, а на выходе элемента 6 задержки устанавливается логический Ноль, что вызывает запуск одновибратора 11 сигналом с выхода логического инвертора 14, Передним фронтом сигнала с выхода одновибратора 11, подаваемого

5

в единичное состояние. С этого момента начинается регенера1щя аналоговой информации в канале с адресом 1. По окончании регенерации этого канала содержимое счетчика 5 опять наращивается на единицу, после чего производится регенерация в следующем канале. Таким образом будет происходить регенерация последовательно всех каналов устройства до появления на выходе переполнения счетчика 5 сигнала переполнения. Этот сигнал, появляю1ций ся как реакция счетчика 5 на передний фронт сигнала одновибратора 11, обнуляет триггер 10, инверсный выходной сигнал которого, собранный по И с выходным сигналом одновибратора 11 логическим элементом И 12, обнуляет счетчик 5, На этом процесс регенерации каналов устройства заканчивается, и оно переходит в режим хране- ния.

Время регенерации tp определяется как сумма

(t; ± t; + t

4)N,

где N - количество каналов устройств

Быстродействие предложенного устройства повышается благодаря тому, что аналоговая величина на выходе соответствующего блока аналоговой памяти устанавливается непосредственно после записи цифровой информации в ячейки блока оперативной памяти за время, необходимое для установки аналоговой величины на выходе цифроана- логового преобразователя и смены аналоговой величины в блоке аналоговой памяти.

Кроме того, в режиме регенерации в предложенном устройстве происходит .только регенерация, т.е. возобновление аналоговой информации в каждом из блоков аналоговой памяти, на что необходимо время меньшее (в пределах одного канала), чем для ее смены. Таким образом, регенерация каналов в устройстве происходит быстрее, чем в прототипе, так как tT t,. Уменьшение уровня помех в устройстве достигается за счет организации режима хранения, при котором в устройстве отсутствуют переключения.

Дополнительная возможность синхронизации процесса регенерации в устройстве обеспечивается наличием входа разрешения регенерации и организацией процесса регенерации с нулевого адреса устройства.

Формула изобретения

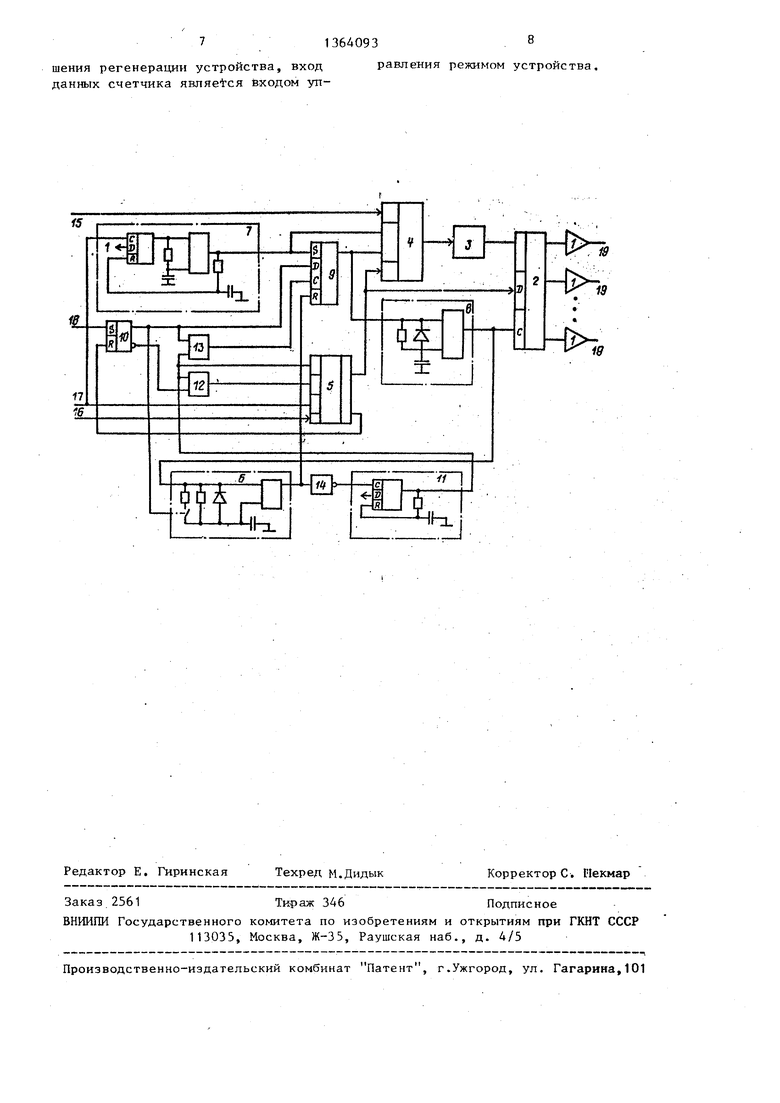

Аналоговое запоминающее устройство, содержащее блоки аналоговой памяти, выходы которых являются выходами устройства, коммутатор, выходы которого соединены с информационными вxoдa п блоков аналоговой памяти, циф- роаналоговьй преобразователь, вход которого соединен с выходом блока оперативной памяти, информационный вход блока оперативной памяти является ин- формационньсм входом устройства, счетчик, отличающееся тем,

д что, с целью повышения быстродействия, помехоза1С|ищенности и расширения области применения устройства за счет создания режима регенерации информации внешним сигналом, в него введены элементы

5 задержки, триггеры, элементы И, инвертор, одновибратор и элемент ИСКЛИОЧА- ЮЩЕЕ ИЛИ, выход которого соединен с

входом синхронизации первого триггера, прямой выход второго триггера соеди- 0 нен с управляюи им входом первого элемента задержки, с информационным входом первого триггера и с первым входом элемента ИСКЛ10ЧА10ППЕ НЛП, второй вход которого соединен с входом син- 5 хронизации счетчика, с первым входом элемента И и с выходом одновибратора, вход одновибратора соединен с выходом инвертора, вход которого соединен с выходом первого элемента задержки и 0 входом установки в Ноль первого триггера, вход установки в Единицу первого триггера соединен с выходом второго элемента задержки и входом разрешения записи блока оперативной памяти, вход разрешения выбора информации которого соединен ,с выходом первого триггера и входом третьего элемента задержки, выход третьего элемента задержки соединен с информа- 0 ционным входом первого элемента задержки и с первым управляющим входом коммутатора, второй управляющий вход которого соединен с адресным входом блока оперативной памяти и с информа- 5 ционным выходом счетчика, выход переполнения счетчика соединен с входом установки в Поль второго триггера, инверсный выход которого соединен со вторым входом элемента PI, выкод 0 элемента И соединен с входом установки в Ноль счетчика, вход разрешения приема информации счетчика является входом разрешения приема информации устройства и соединен с входом второго элемента задержки, выход циф- роаналогового преобразователя нен с информационным входом коммутатора, вход установки в Единицу второго триггера является входом разре- I

шения регенерации устройства, вход равления режимом устройства, данных счетчика являемся входом уп

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программного управления | 1981 |

|

SU987579A1 |

| Устройство для программного управления с самоконтролем | 1983 |

|

SU1130832A1 |

| Устройство для синхронизации распределенной вычислительной системы | 1988 |

|

SU1508201A1 |

| Автокоррелятор | 1990 |

|

SU1833894A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для контроля оперативной памяти | 1989 |

|

SU1705875A1 |

| УСТРОЙСТВО АНАЛИЗА ПЕРЕКРЫТИЙ КАНАЛОВ ПРИ РАЗМЕЩЕНИИ ПАРАЛЛЕЛЬНЫХ ПОДПРОГРАММ В МНОГОПРОЦЕССОРНЫХ СИСТЕМАХ | 2011 |

|

RU2460126C1 |

| Устройство для сжатия цифровых телевизионных сигналов цветного изображения | 1988 |

|

SU1529471A1 |

| Многоканальная система для анализа формы и регистрации аналоговых процессов | 1983 |

|

SU1149242A1 |

| Многоканальная система измерения и регистрации | 1988 |

|

SU1707546A1 |

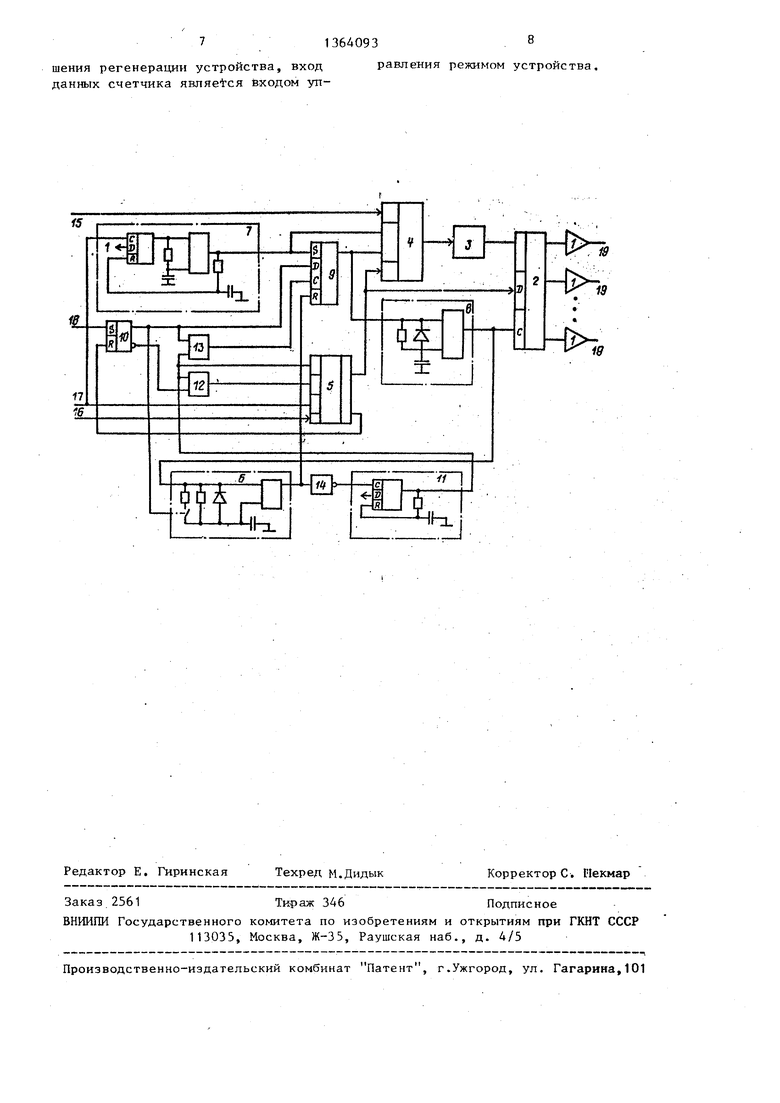

Изобретение относится к вычис- лительн ой технике, в частности к запоминающим устройствам, и может быть использовано в блоках сопряжения цифровых устройств с аналоговыми„ Цель изобретения - повышение быстродействия, помехоза1 1лщенности и расширение области применения устройства за счет создания режима регенерации информации внешним сигналом достигается введением в устройство элементов за:держки, триггеров, элемента И, Изобретение относится к вычислительной технике, в частности к запоминающим устройствам,-и может быть использовано в блоках сопряжения цифровых устройств с аналоговыми. Целью изобретения является повышение быстродействия, помехозащищенности и расширение области применения за счет создания режима регенерации информации внешним сигналомi На чертеже представлена функциональная схема предложенного устройства. инвертора, одновибратора и элемента ИСКПЮЧАЮПЩЕ ИЛИ и их связей с известными блоками. По сигналу Запись на входе 16 в счетчик 5 записывается адрес канала устройства, с выхода которого он поступает на блок 4 оперативной памяти и на коммутатор 2. После задержки элементом 7 сигнал поступает на входы триггера 9 и блока 4 и вызывает установку триггера в единичное состояние и запись цифровой ин- форма11;ии в блок 4, с выхода которого она поступает на преобразователь 3. Момент установки триггера 9 в единичное состояние определяется элементом 6 задержки. При появлении сигнала на входе разрешения коммутатора 2 им вырабатывается сигнал разрешения, который вызывает подключение соответствую ющего блока 1 к преобразователю 3. .Режим регенерации организован триггерами 10, 9, одновибратором 11, элементом 6 задержки, элементами 12 и 13 и инвертором 14. 1 ил. Устройство содержит блоки 1 аналоговой памяти, коммутатор 2, 1щфро- аналоговый преобразователь 3, блок 4 оперативной памяти, счетчик 5, элементы 6, 7 и 8 задержки, триггеры 9 и 10, одновибратор 11, элемент И 12, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 13, инвертор 14, информа11;ионный вход 15, адресный вход 16, вход 17 разрешения приема информации, вход 18 разрешения регенерации и выходы 19. Элемент 6 задержки выполнен программируемьм. Устройство работает в режимах, записи, регенерации и хранения. оэ 05 о CD 05

±1

Редактор Е. Гиринская

Техред М.Дидык

Заказ 2561Тираж 346Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

- - ----«----------.-- - ---.-.- -.--.-.-,-. - -...-,. и....«и,,я,.

Производственно-издательский комбинат Патент, г.Ужгород, ул. Гагарина,101

Корректор С. Иекмар

| Многоканальный преобразователь кода в напряжение | 1973 |

|

SU660233A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU883974A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1991-05-30—Публикация

1986-03-07—Подача