(Л

0

оо

О5

о 4 СП

f)Uff

Изобретение относится к вычислительной технике, в частности к контролю запоминающих устройств, и-может быть использовано при их производ- стве.

Цель изобретения - повышение достоверности контроля памяти.

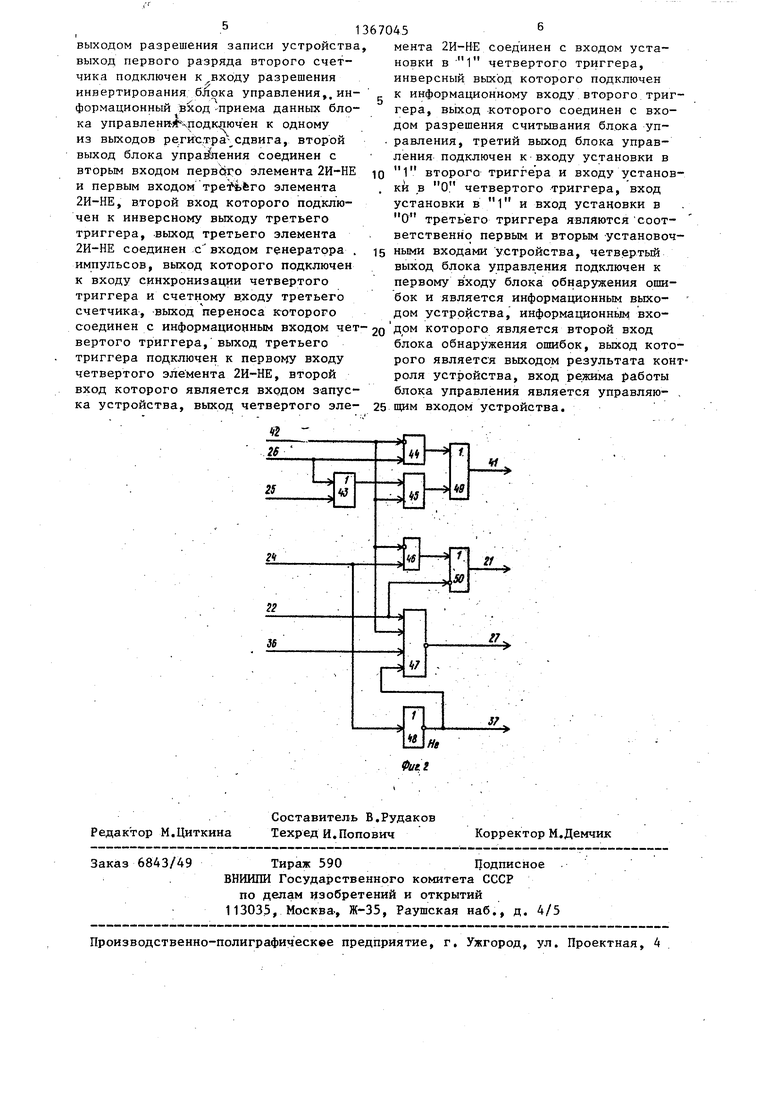

На фиг. 1 изображена структурная схема устройства для контроля памяти; на фиг. 2 - структурная схема блока управления.

Устройство для контроля памяти (фиг. 1) содержит блок 1 свертки по модулю два, блок 2 обнаружения ошибок, первый счетчик 3, регистр 4 сдвига, первый 5, второй 6, третий 7 и четвертый 8 триггеры, первый 9, второй 10, третий 11 и четвертый 12 элементы 2И-НЕ, второй 13 и третий 14 счетчики, генератор 15 импульсов и блок 16 управления. Выход 17 элемента 2И-НЕ 9 подключен к инверсному входу элемента 10, входу синхронизации.первого триггера 5, счетному входу .первого счетчика 3, рчетному входу второго счетчика 13, а первый вход элемента 2И-НЕ 9 подклчен к входу синхронизации второго триггера 6 и является входом 18 синхронизации устройства. Выход 19 элемента 2И-НЕ 10 подключен к входу синхронизации регистра 4 сдвига, а

В этом режиме в контролируемую па мять записывается псевдослучайный циклический код, далее контролируема память переводится в режим считыва- 35 ния, при эт ом производится сравнение считанной информации с записанной (эталонной). При несовпадении считан ной и эталонной информации контролируемая память считается неисправной, в противном случае контроль продолжается в течение заданного времени. Если по истечении этого времени не обнаружено несовпадение считанной и эталонной информации, то контролируе

40

прямой вход элемента 2И-НЕ 10 - к выходу 20 первого триггера 5, входы синхронизации и установки О которого подключены к первому выходу 21 блока 16, выход 22 переноса первого счетчика 3 подключен к входу разрешения счета второго счетчика 13, а выход 23 разрядов счетчика 3 является адресным выходом устройства, выход 24 нулевого разряда второго счетчика 14 является выходом разрешения записи устройства,, а выход 25 первого разряда счетчика. 13 подключен к 45 мая память считается исправной. Для одному из входов блока 16, вход прие- реализации этого режима на вход 42 ма данных блока 16 подключен к одному из выходов 26 регистра 4 сдвига, второй выход 27 блока 16 подключен к второму входу элемента 2И-НЕ 9 и к 50 первому входу элемента 2И-НЕ 11, второй вход которого подключен к инверсному выходу 28 триггера 27. Вход 29 синхронизации счетчика 14 и вход синхронизации четвертого триггера 8 под- §5 ключены к выходу генератора 15, а выход 30 счетчика 14 - к информационному входу четвертого триггера 8, инверсный выход 31 которого подключен

блока 16 подается уровень О. В исходном состоянии регистр 4 сдвига .находится в состоянии 1, триггер 5 также в состоянии 1, на выходе 27 блока 16 формируется уровень 1, а первый 3 и второй 13 счетчики уста новлены в состояние О. I .

На вход 18 устройства поступают прямоугольные импульсы, период следо вания которых равен длительности цик ла обращения к контролируемой памяти. Эти импульсы инвертируются пер

к информационному входу второго триггера 6. Входы 32 и 33 третьего триггера 7 являются соответственно первым и вторым установочными входами устройства. Прямой выход 34 триггера 7 подключен к первому входу элемента 2И-НЕ 12, второй вход 35 которого является входом запуска устройства, а выход 36 подключен к входу установки в О триггера 8. Выход 37 блока 16 подключен к входу установки в 1 триггеров 8, а выход триггера 6 подключен к входу 38 блока 16, выход 39 блока 2 обнаружения ошибок является выходом результата контро- ля устройства, вход 40 блока обнаружения ошибок является входом данных устройства, выход 41 является выходом данных устройства. Вход 42 блока Т6 является управляющим входом устройства

Блок 16 (фиг. 2) содержит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 43, первый элемент 2И 44, второй элемент 2И 45, третий элемент 2И 46, элемент 4И-НЕ 47, элемент НЕ 48, первый элемент 2ИЛИ 49, , второй элемент 2ИЛИ 50.

Устройство памяти работает следующим образом.

Режим Контроль функционирования.

В этом режиме в контролируемую память записывается псевдослучайный циклический код, далее контролируемая память переводится в режим считыва- ния, при эт ом производится сравнение считанной информации с записанной (эталонной). При несовпадении считанной и эталонной информации контролируемая память считается неисправной, в противном случае контроль продолжается в течение заданного времени. Если по истечении этого времени не обнаружено несовпадение считанной и эталонной информации, то контролируе

мая память считается исправной. Для реализации этого режима на вход 42

мая память считается исправной. Для реализации этого режима на вход 42

блока 16 подается уровень О. В исходном состоянии регистр 4 сдвига .находится в состоянии 1, триггер 5 также в состоянии 1, на выходе 27 блока 16 формируется уровень 1, а первый 3 и второй 13 счетчики установлены в состояние О. I .

На вход 18 устройства поступают прямоугольные импульсы, период следования которых равен длительности цикла обращения к контролируемой памяти. Эти импульсы инвертируются пер20

25

вым элементом 2И-НЕ 9 и поступают на входы первого 3 и второго 13 счетчиков и первого триггера 5, далее эти импульсы через логический элемент 2И-НЕ 10 поступают на вход 19 регистра 4 сдвига,

На выходе нулевого разряда 24 счетчика 13 формируется уровень О, который поступает на вход разрешения записи устройства и удерживает ее в режиме записи информации, которая в виде последовательности 1 и О формируется на выходе 26 регистра 4 сдвига, поступает на вход 26 блока 16 и далее на информационный вход контролируемой памяти. Одновременно с этим на выходе 23 счетчика 3, соединенного с адресным входом контролируемой памяти, формируются адреса, В состоянии последнего адреса на выходе 22 переноса счетчика 3 формируется уровень 1, вследствие чего, во-первых, на первом выходе 21 блока 16 формируется уровень О, который записывается во второй триггер 5 и тем самым блокирует поступление одного импульса синхронизации на входе синхронизаии 19 регистра сдвига 4, во-вторых, ормируется на выходе 24 нулевого азряда счетчика 13 уровень 1, пееводя тем самым контролируемую паять в режим считывания, и происходит считывание информации из контролируеой памяти с одновременным сравнением ее с эталонной информацией блоком 2 обнаружения ошибок, В момент переключения выхода 24 счетчика 13 из 1 в О, что соответствует перехоу контролируемой памяти из режима считывания в режим записи, блокирова прохождения одного импульса синронизации на вход 19 регистра 4. сдвига не происходит.

Режим Контроль времени хранения (периода регенерации).

Этот режим начинается записью в контролируемую память псевдослучайного циклического кода, далее следует пауза, по длительности равная времени хранения (периоду регенерации), только после этого считывание ин-. ормации из контролируемой памяти с одновременным сравнением. Далее то же gg самое происходит с инвертированными анными (запись - пауза - считывание), При этом блокировка прохождения одного импульса синхронизации на вход

Q

15

35

30

45

40

50

7045

19 регистра 4 сдвига происходит не только в момент перехода контролируемой памяти из режима записи в режим считывания, но и наоборот - из режима считывания в режим записи.

Режим Предварительная запись.

Этот режим начинается записью в

контролируемую память, затем контро Q линуемая память подвергается испытаниям (воздействиям) и только после этого переходит в режим считывания со сравнением. Таким образом проверяется способность контролируемой памяти

15 сохранять свои рабочие характеристики при различных видах испыта НИИ,

Формула изобретения

Устройство для контроля памяти, содержащее блок свертки по модулю два, блок обнаружения ошибок, первый счетчик, регистр сдвига и блок управления, причем выходы разрядов регистра сдвига подключены к входам блока свертки по модулю два, выход которого соединен с информационным входом регистра сдвига, отличающее с я тем, что, с целью повьш1ения достоверности контроля, в устройство введены второй и третий счетчики, с nepBoiro по четвертый триггеры, с первого по четвертый элементы 2И-НЕ и генератор импульсов, причем выход первого элемента 2И-НЁ подключен к инверсному входу второго элемента 2И-НЕ,- к входу синхронизации первого триггера и к счетным входам первого и второго счетчиков, первый вход первого элемента 2И-НЕ и вход синхронизации второго триггера объединены и являются входом синхронизации устройства, выход второго элемента

2И-НЕ соединен с входом синхронизации регистра сдвига, прямой вход второго элемента 2И-НЕ подключен к выходу первого триггера, вход синхронизации и вход установки в О которого соединены с первым выходом, блока управления, выход переноса первого счетчика подключен к входу разрешения счета второго счетчика и входу окончания цикла контроля блока управления, выходы разрядов первого счетчика являются адресными выходами устройства, выход нулевого разряда второго счетчика подключен к входу разрешения записи блока управления и является

выходом разрешения записи устройства выход первого разряда второго счетчика подключен к входу разрешения инвертирования SJTioKa управления,, информационный вход -приема данных блока управлен11- чподключ ен к одному из выходов peгиt.тpa сдвига, второй выход блока управления соединен с вторым входом первЬго элемента 2И-НЕ и первым входом элемента 2И-НЕ, второй вход которого подключен к инверсному выходу третьего триггера, выход третьего элемента 2И-НЕ соединен с входом генератора . импульсов, выход которого подключен к входу синхронизации четвертого триггера и счетному входу третьего счетчика, -выход переноса которого

соединен с информационным входом чет-2о ДОМ которого является второй вход

вертого триггера, выход третьего триггера подключен к первому входу четвертого эле мента 2И-НЕ, второй вход которого является входом запуска устройства, выход четвертого элеЙ - 26

2

мента 2И-НЕ соединен с входом установки в четвертого триггера, инверсный выход которого подключен к информационному входу второго триггера, выход которого соединен с входом разрешения считьшания блока управления, третий выход блока управления подключен к входу установки в 1 второго тригг ера и входу установки в

О

четвертого триггера, вход установки в 1 и вход установки в О

третьего триггера являются соответственно первым и вторым установоч- 5 ными входами устройства, четвертый выход блока управления подключен к первому входу блока обнаружения ошибок и является информационным выходом устройства, информационнь)м вхоблока обнаружения ошибок, выход которого является выходом результата контроля устройства, вход ре.жима работы блока управления является управляю- , 25 щим входом устройства.

4«

W

W

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля памяти | 1987 |

|

SU1587598A1 |

| Устройство для контроля памяти | 1983 |

|

SU1167660A1 |

| Устройство для функционального контроля интегральных схем | 1988 |

|

SU1737465A1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| Устройство для контроля памяти | 1987 |

|

SU1513525A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПАМЯТИ | 1990 |

|

RU2015581C1 |

| Логический анализатор | 1988 |

|

SU1654822A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1545221A1 |

| УСТРОЙСТВО ДИАГНОСТИЧЕСКОГО КОНТРОЛЯ КАНАЛА ВОСПРОИЗВЕДЕНИЯ АППАРАТУРЫ ЦИФРОВОЙ МАГНИТНОЙ ЗАПИСИ | 1991 |

|

RU2024968C1 |

Изобретение относится к вычислительной технике, в частности к контролю запоминающих устройств, и может быть использовано при их производстве. Цель изобретения - повышение достоверности контроля . Устройство содержит блок 1 свертки по модулю два, блок 2 обнаружения, первый счетчик 3, регистр 4 сдвига, первьй 5, второй 6, третий 7 и четвертый 8 триггеры, первый 9, второй 10, третий 11 и четвертый 12 элементы 2И-НЕ, второй 13 и третий 14 счетчики, генератор 15 импульсов и блок 16 управления. Устройство может работать в трех режимах: контроль функционирования памяти, контроль периода регенерацда памяти, предварительная запись в память. 2 ил.

24

36

W

If

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЗАПОМИНАЮЩИХМОДУЛЕЙ | 1972 |

|

SU428455A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для контроля памяти | 1983 |

|

SU1167660A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-01-15—Публикация

1985-10-14—Подача