UZ

00

1513525

Изобретение относится к вычислительной техзшке и может быть использовано при контроле оперативных запоминающих устройств,г

Цель изобретения - повышение достоверности контроля.

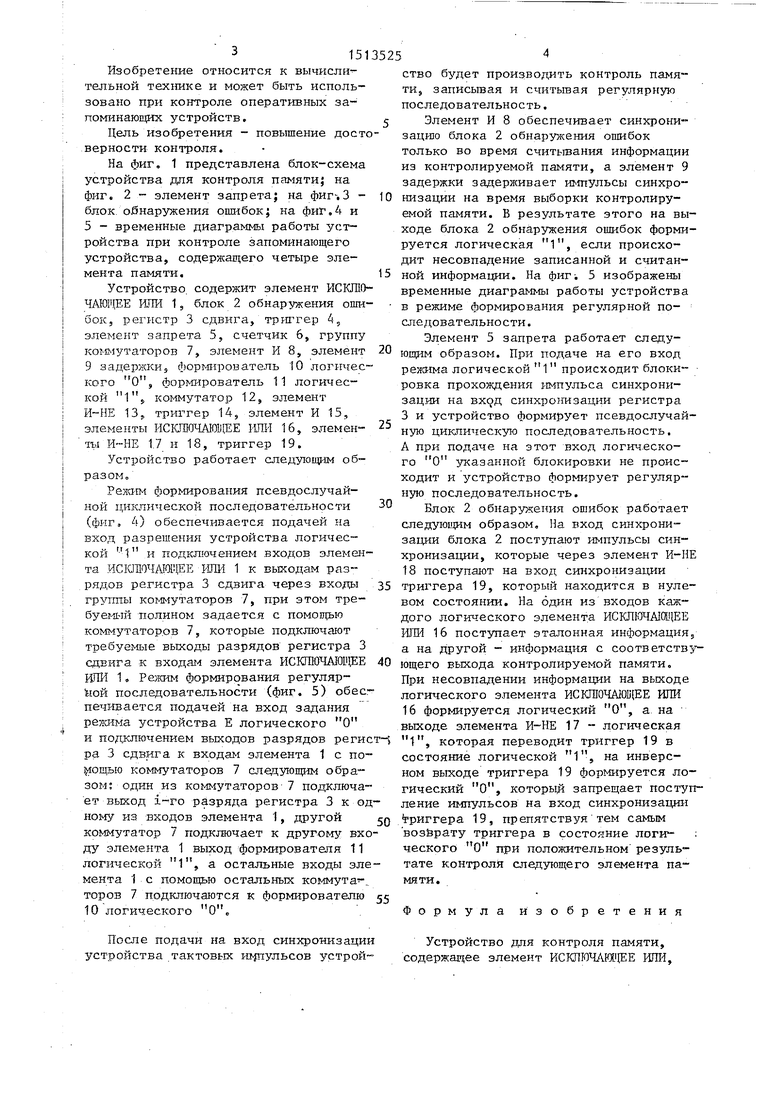

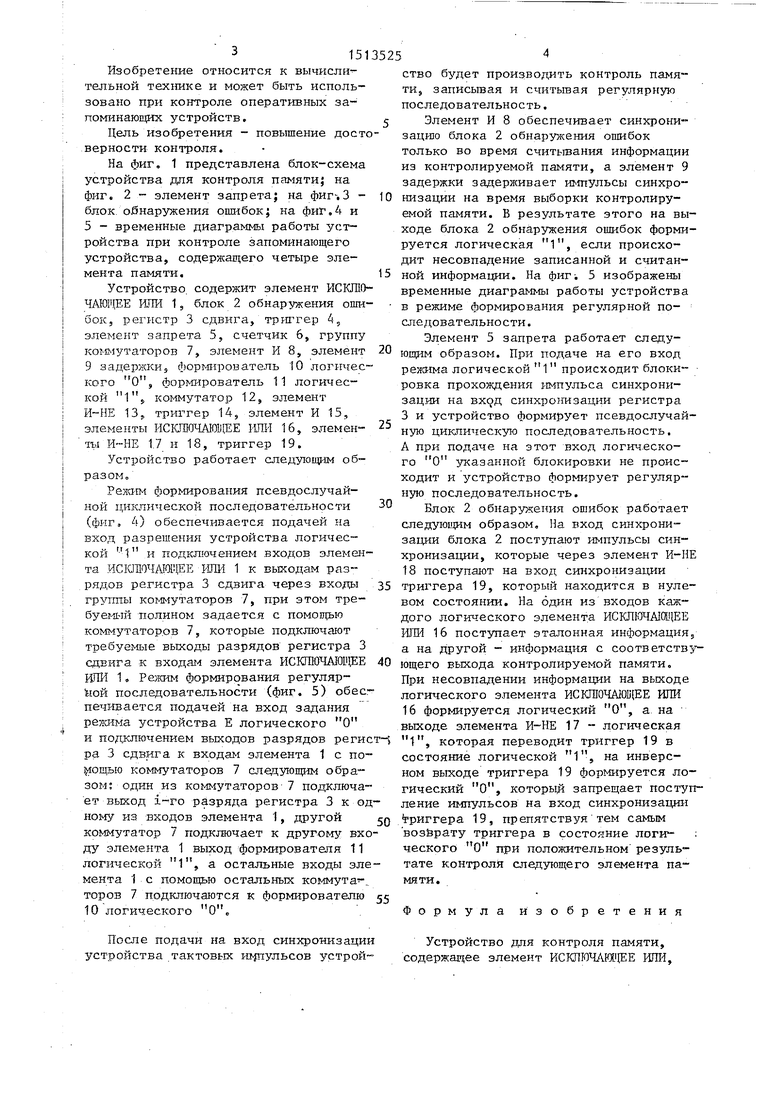

На фиг, 1 представлена блок-схема устройства для контроля памяти; на

Элемент И 8 обеспечивает синхрони зацизо блока 2 обнаружения ошибок только во время считывания информации из контролируемой памяти, а элемент 9 задержки задерживает импульсы синхрофиг. 2 - элемент запрета; на фиг-,3 - Ю низации на время выборки контролирублок обнаружения ошибок; на фиг,4 и 5 - временные диаграммы работы устройства при контроле запоминающего устройства, содержащего четыре элемента памяти.

Устройство, содержит элемент ИСКГОО- ЧАЮ1Ч,ЕЕ ИЛИ 15 блок 2 обнаружения ошибок, регистр 3 сдвига, трш гер 4, элемент запрета 5, счетчик 6, группу ког-шутаторов 7, элемент И 8, элемент 9 задержкид формирователь 10 логического О, формирователь 11 логической , коммутатор 12, элемент 13 триггер 14, элемент И 15, элементы ИСКПЮ ЧАЮ1 1ЕЕ 1ШИ 16, элемента И--НЕ 1,7 и 18, триггер 19,

Устройство работает следующим образом,

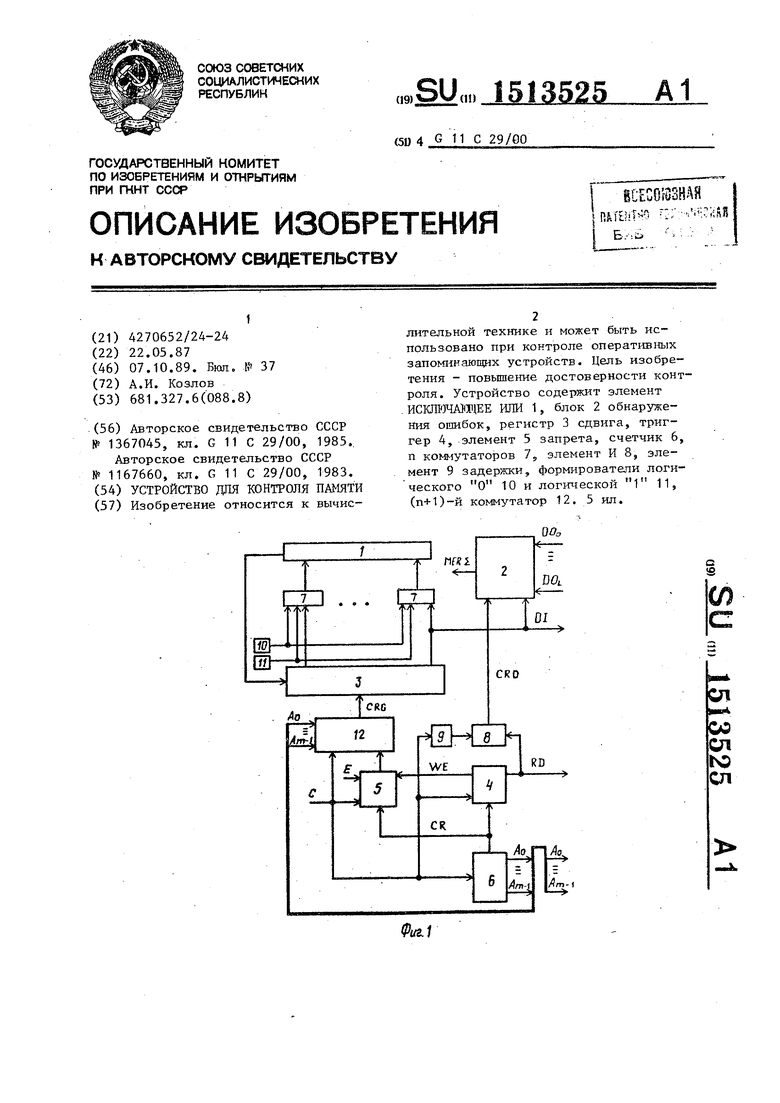

Рела-ш формирования псевдослучайной цикли ческой последовательности (фиг, 4) обеспечивается подачей на вход разрешения устройства логической 1 и подключением входов элемента ИСКгаОЧ даЩЕЕ РЖИ 1 к выходам разрядов регистра 3 сдвига через входы группы ког- мутаторов 7, при этом требуемый полином задается с помощью коммутаторов 7, которые подключают требуемые выходы разрядов регистра 3 сдвига к входам элемента ИСКПЮЧАЮЩЕ ИЛИ 1. Режим формирования регулярной последовательности (фиг. 5) обеспечивается подачей на вход задания

20

25

емой памяти. В результате этого на вы ходе блока 2 обнаружения ошибок форми руется логическая 1, если происходит несовпадение записанной и считан15 ной информации. На фиг-. 5 изображены

временные диаграммы работы устройства в режиме формирования регулярной по- следовательности.

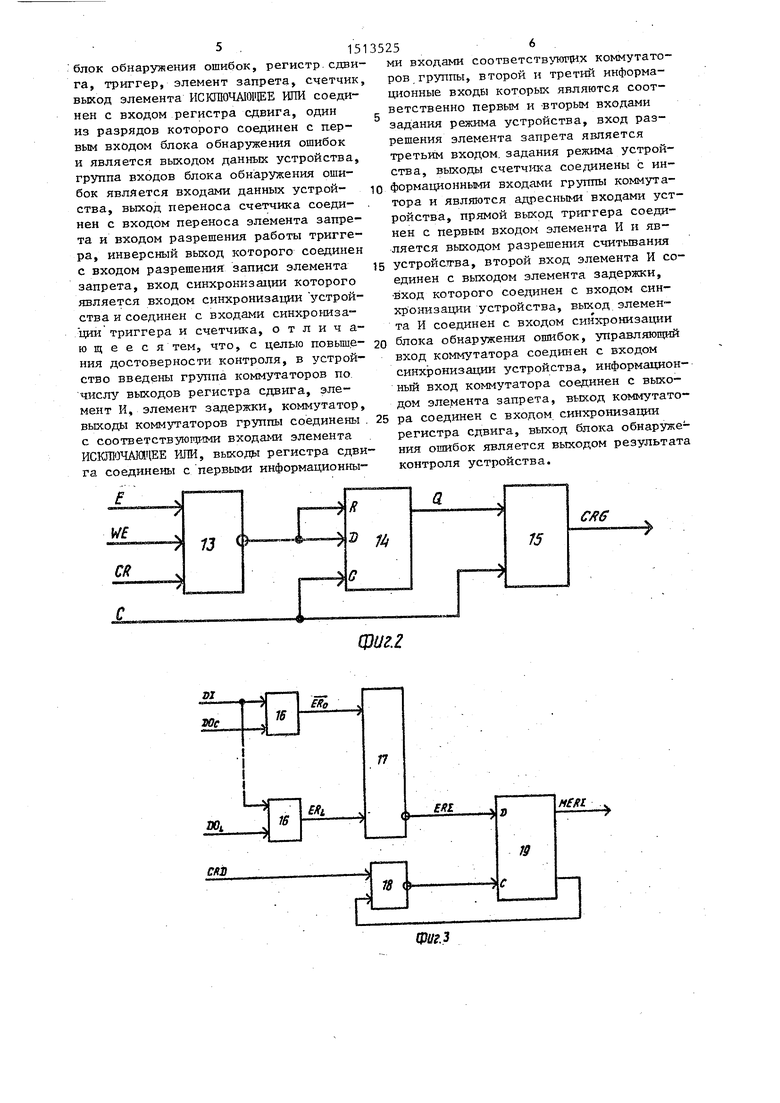

Элемент 5 запрета работает следу- юшрм образом. При подаче на его вход реиша логической 1 происходит блокировка прохождения импульса синхронизации на вход синхронизации регистра 3 и устройство формирует псевдослучай ную циклическую последовательность, А при подаче на этот вход логического О указанной блокировки не происходит и устройство формирует регуляр- HJTO последовательность.

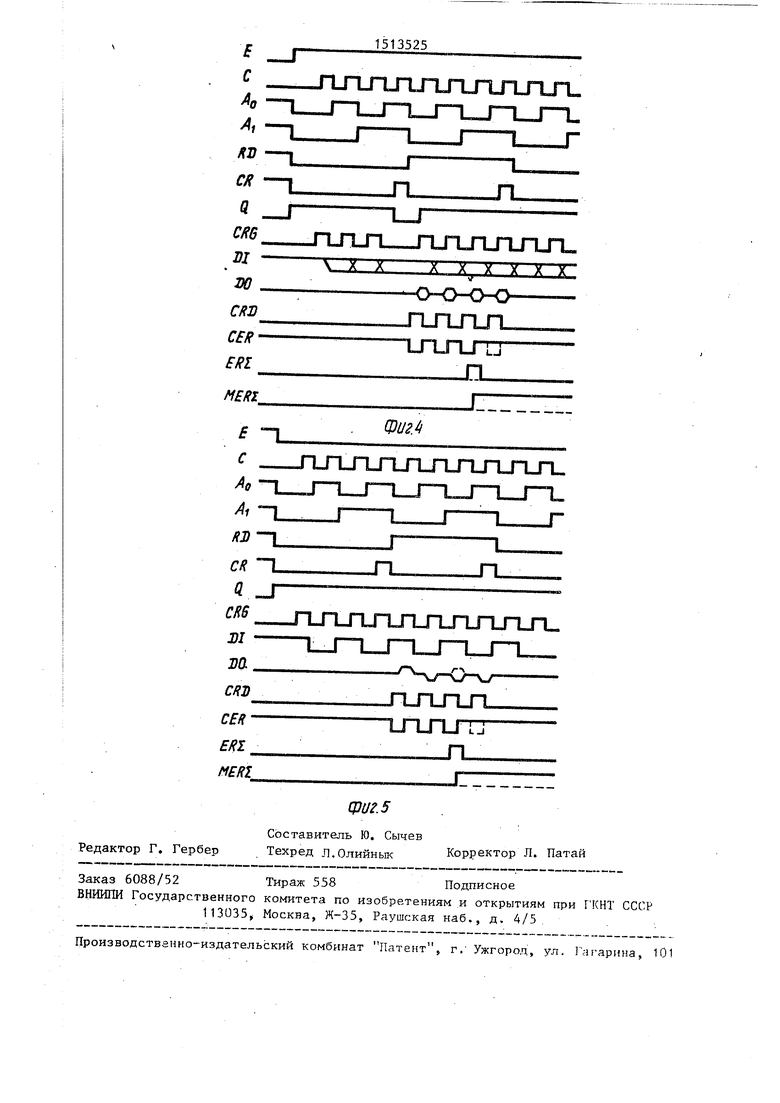

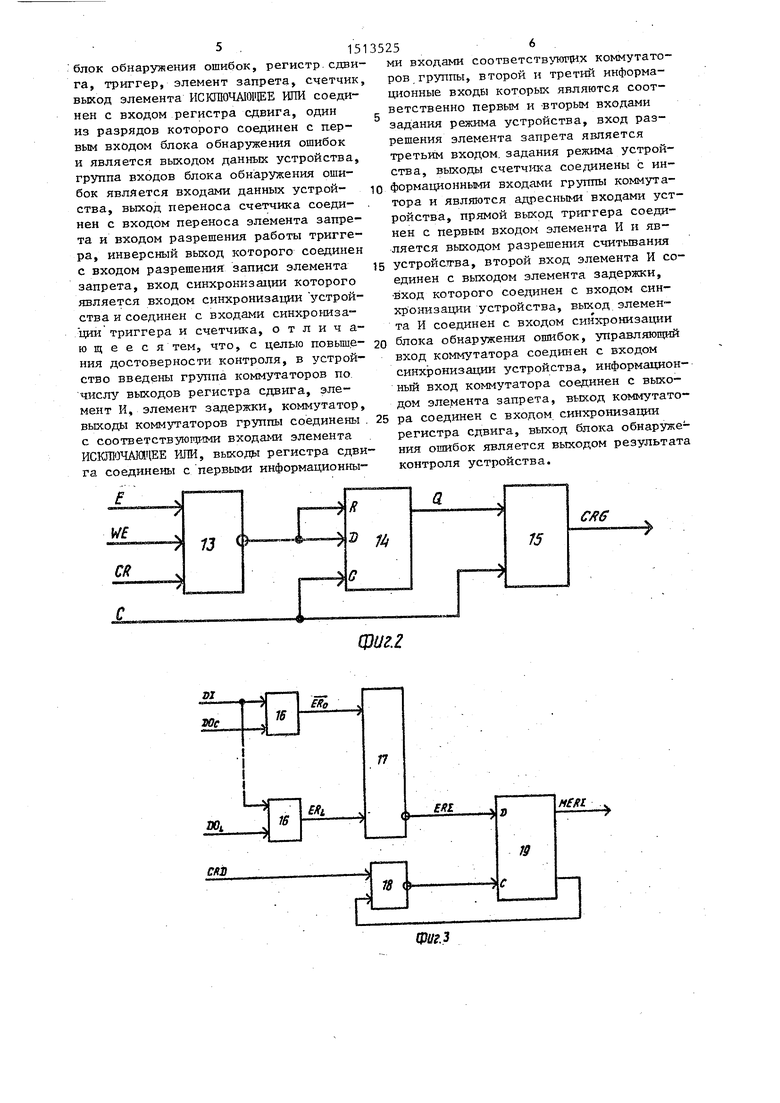

Блок 2 обнаружения ошибок работает следуюидим образом. На вход синхронизации блока 2 поступают импульсы синхронизации, которые через элемент И-Н 18 поступают на вход синхронизации

35 триггера 19, который находится в нуле вом состоянии. На один из входов каждого логического элемента ИСКЛЮЧАКШЩЕ ИЛИ 16 поступает эталонная информация а на другой - информация с соответств ющего выхода контролируемой памяти. При несовпадении информации на выходе логического элемента ИСКгаОЧА10Ь ЕЕ ИЛИ 16 формируется логический О, а на выходе элемента И-НЕ 17 - логическая

30

40

35 триггера 19, который находится в нул вом состоянии. На один из входов каждого логического элемента ИСКЛЮЧАКШЩЕ ИЛИ 16 поступает эталонная информаци а на другой - информация с соответств ющего выхода контролируемой памяти. При несовпадении информации на выход логического элемента ИСКгаОЧА10Ь ЕЕ ИЛИ 16 формируется логический О, а на выходе элемента И-НЕ 17 - логическая

релдама устройства Е логического О

и подключением выходов разрядов регист-; которая переводит триггер 19 в

1, на инверсра 3 сдвига к входам элемента 1 с по- ощью коммутаторов 7 следующим обра™ зом; один из коммутаторов-7 подключает выход i-ro разряда регистра 3 к одному из входов элемента 1, другой п коммутатор 7 подключает к другому входу элемента 1 выход формирователя 11 логической 1, а остальные входы элемента 1 с помощью остальных коммута - торов 7 подключаются к формирователю 55 10 логического О.

После подачи на вход синхронизации устройства тактовых ш пульсов устройсостояние логической

ном выходе триггера 19 формируется ло гический О, который запрещает посту ление импульсов на вход синхронизации триггера 19, препятствуя тем самым возврату триггера в состояние логи ческого О при положительном резуль тате контроля следзтощего элемента па мяти.

Формула изобретения

Устройство для контроля памяти, содержащее элемент ИСКЛЮЧАЮ1ЦЕЕ ИЛИ,

ство будет производить контроль памя ти, записывая и считывая регулярную последовательность.

Элемент И 8 обеспечивает синхрони зацизо блока 2 обнаружения ошибок только во время считывания информации из контролируемой памяти, а элемент 9 задержки задерживает импульсы синхронизации на время выборки контролиру0

5

емой памяти. В результате этого на выходе блока 2 обнаружения ошибок формируется логическая 1, если происходит несовпадение записанной и считан5 ной информации. На фиг-. 5 изображены

временные диаграммы работы устройства в режиме формирования регулярной по- следовательности.

Элемент 5 запрета работает следу- юшрм образом. При подаче на его вход реиша логической 1 происходит блоки ровка прохождения импульса синхронизации на вход синхронизации регистра 3 и устройство формирует псевдослучайную циклическую последовательность, А при подаче на этот вход логического О указанной блокировки не происходит и устройство формирует регуляр- HJTO последовательность.

Блок 2 обнаружения ошибок работает следуюидим образом. На вход синхронизации блока 2 поступают импульсы синхронизации, которые через элемент И-НЕ 18 поступают на вход синхронизации

5 триггера 19, который находится в нулевом состоянии. На один из входов каждого логического элемента ИСКЛЮЧАКШЩЕ ИЛИ 16 поступает эталонная информация, а на другой - информация с соответств - ющего выхода контролируемой памяти. При несовпадении информации на выходе логического элемента ИСКгаОЧА10Ь ЕЕ ИЛИ 16 формируется логический О, а на выходе элемента И-НЕ 17 - логическая

0

0

состояние логической

ном выходе триггера 19 формируется логический О, который запрещает поступление импульсов на вход синхронизации триггера 19, препятствуя тем самым возврату триггера в состояние логи : ческого О при положительном результате контроля следзтощего элемента памяти.

Формула изобретения

Устройство для контроля памяти, содержащее элемент ИСКЛЮЧАЮ1ЦЕЕ ИЛИ,

блок обнаружения ошибок, регистр.сдвига, триггер, элемент запрета, счетчик выход элемента ИСКЛЮЧАЮ1ЦЕЕ ИЛИ соединен с входом регистра сдвига, один из разрядов которого соединен с первым входом блока обнаружения ошибок и является выходом данных устройства, группа входов блока обнаружения ошибок является входами данных устройства, выход переноса счетчика соединен с входом переноса элемента запрета и входом разрешения работы триггера, инверсный выход которого соединен с входом разрешения записи элемента запрета, вход синхронизации которого является входом синхронизации устройства и соединен с входами синхрониза- цин триггера и счетчика, о т л и ч а- ю щ е е с я тем, что, с целью повьше- ния достоверности контроля, в устрой- ство введены группа коммутаторов по числу выходов регистра сдвига, элемент И, элемент задержки, коммутатор, выходы коммутаторов группы соединены . с соответствующими входами элемента ИСКШЗЧАКХЦЕЕ ИЛИ, выходы регистра сдвига соединены с первыми информационными входами соответствуюттих коммутаторов группы, второй и третий информационные входы которых являются соответственно первым и -вторым входами задания режима устройства, вход разрешения элемента запрета является третьим входом, задания режима устройства, выходы счетч1-ш:а соединены с инФормационными входами группы коммутатора и являются адресными входами устройства, прямой выход триггера соединен с первым входом элемента И и является выходом разрешения считьшания

устройстгва, второй вход элемента И соединен с выходом элемента задержки, вход которого соединен с входом синхронизации устройства, выход элемента И соединен с входом синхронизации

блока обнаружения ошибок, управляющий вход коммутатора соединен с входом синхронизации устройства, информационный вход коммутатора соединен с выходом элемента запрета, выход коммутато

ра соединен с входом, синхронизации регистра сдвига, выход блока обнаружения ошибок является выходом результата контроля устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля памяти | 1987 |

|

SU1587598A1 |

| Устройство для контроля памяти | 1985 |

|

SU1367045A1 |

| Устройство для контроля памяти | 1983 |

|

SU1167660A1 |

| Устройство для обмена информацией | 1982 |

|

SU1131035A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| Устройство для группового контроля логических блоков | 1986 |

|

SU1372323A1 |

| Система передачи и приема цифровой информации | 1988 |

|

SU1559361A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| Устройство для контроля магистралей электронных вычислительных машин | 1981 |

|

SU964648A1 |

| Устройство для выделения рекуррентного синхросигнала | 1983 |

|

SU1116547A1 |

Изобретение относится к вычислительной технике и может быть использовано при контроле оперативных запоминающих устройств. Цель изобретения - повышение достоверности контроля. Устройство содержит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 1, блок 2 обнаружения ошибок, регистр 3 сдвига, триггер 4, элемент 5 запрета, счетчик 6, N коммутаторов 7, элемент И 8, элемент 9 задержки, формирователи логического "0" 10 и логической "1" 11, (N+1)-й коммутатор 12. 5 ил.

фиг.г

Т

nJTJTJTJTJTJTJ-LJTJ-L.

г

L

Л.

/fJJ-1

П

п

-----

ruiLnjiJTJTJTJTjarb

Фиг.

L

Л.

П

п

| Устройство для контроля памяти | 1985 |

|

SU1367045A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для контроля памяти | 1983 |

|

SU1167660A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1989-10-07—Публикация

1987-05-22—Подача