Изобретение относится к вычислительной технике, в частности к устройствам для контроля запоминающих устройств, и может быть использовано при их производстве.

Известно устройство для контроля памяти, содержащее сумматор по модулю два, блок обнаружения ошибок, регистр сдвига, триггер, элемент запрета и счетчик с соответствующими связями [1].

Недостатком этого устройства является невозможность измерения времени потери работоспособности.

Наиболее близким к заявленному является устройство, содержащее сумматор по модулю два, блок обнаружения ошибок, первый счетчик и регистр сдвига с соответствующими связями, первый, второй, третий, четвертый триггеры, первый, второй, третий, четвертый логические элементы 2И-НЕ, второй, третий счетчики, генератор, логическое устройство, включающее логические элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, 2-2И-2ИЛИ, 4И-НЕ, инвертор, синхронизатор, блок формирования контрольных последовательностей и блок электроники выводов [2].

Известное устройство не обеспечивает достаточной достоверности контроля БИС ОЗУ. Это объясняется тем, что, во-первых, устройство-прототип не позволяет измерить время потери работоспособности и, во-вторых, осуществлять измерение во всех режимах работы ОЗУ.

Цель изобретения состоит в повышении достоверности контроля ОЗУ.

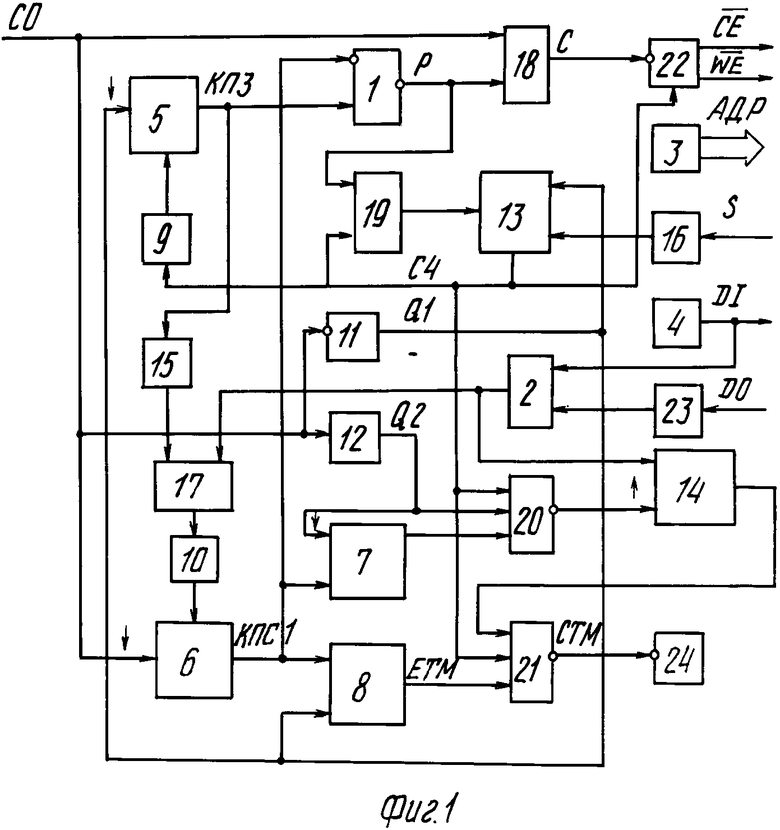

На фиг.1 показана блок-схема заявляемого устройства.

Устройство содержит логический элемент И-НЕ 1, первый логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 2, формирователь 3 адреса, формирователь 4 данных, с первого по десятый триггеры 5-14, первый 15 и второй 16 элементы задержки, первый 17 и второй 18 логические элементы И, второй логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 19, первый 20 и второй 21 логические элементы И-НЕ, синхронизатор 22, компаратор 23 и таймер 24.

Выход первого триггера 5 соединен с первым входом логического элемента И-НЕ 1. Вход синхронизации второго триггера 6 соединен с входом синхронизации устройства. Первый вход первого логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 2 соединен с выходом формирователя 4 данных и выходом данных устройства. Первый вход второго логического элемента И 18 соединен с входом синхронизации устройства, а выход - с входом синхронизатора 22, первый выход которого является выходом разрешения кристалла устройства, а второй выход - выходом разрешения записи устройства. Выход логического элемента И-НЕ1 соединен с вторым входом второго логического элемента И18 и первым входом второго логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 19, выход которого соединен с информационным входом девятого триггера 13. Входы синхронизации седьмого 11 и восьмого 12 триггеров соединены с входом синхронизации устройства. Выход седьмого триггера 11 соединен с входами синхронизации девятого 13, четвертого 8 и первого 5 триггеров, выход восьмого триггера 12 соединен с входом синхронизации третьего триггера 7 и первым входом первого логического элемента И-НЕ 20, выход которого соединен с входом синхронизации десятого триггера 14. Информационный вход первого триггера 5 соединен с выходом пятого триггера 9, установочный вход которого соединен с вторым входом второго логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 19, выходом девятого триггера 13, вторым входом первого логического элемента И-НЕ 20, первым входом второго логического элемента И-НЕ 21 и входом считывания синхронизатора 22. Вход первого элемента 15 задержки соединен с выходом первого триггера 5, а выход - с первым входом первого логического элемента И 17, выход которого соединен с установочным входом шестого триггера 10. Выход шестого триггера 10 соединен с информационным входом второго триггера 6, выход которого соединен с информационным входом четвертого триггера 8, информационным входом третьего триггера 7 и вторым входом (инвертирующим) логического элемента И-НЕ 1. Выход третьего триггера 7 соединен с третьим входом первого логического элемента И-НЕ 20, выход четвертого триггера 8 соединен с вторым входом логического элемента И-НЕ 21, выход которого соединен с входом таймера 24. Третий вход второго логического элемента И-НЕ 21 соединен с выходом десятого триггера 14, информационный вход которого соединен с выходом первого логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 2 и вторым входом первого логического элемента И 17. Вход элемента 16 задержки соединен с входом пуска устройства, а выход - с входом разрешения девятого триггера 13. Вход компаратора 23 соединен с входом данных устройства, а выход - с вторым входом первого логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 2. Выход формирователя 3 адреса является адресным выходом устройства.

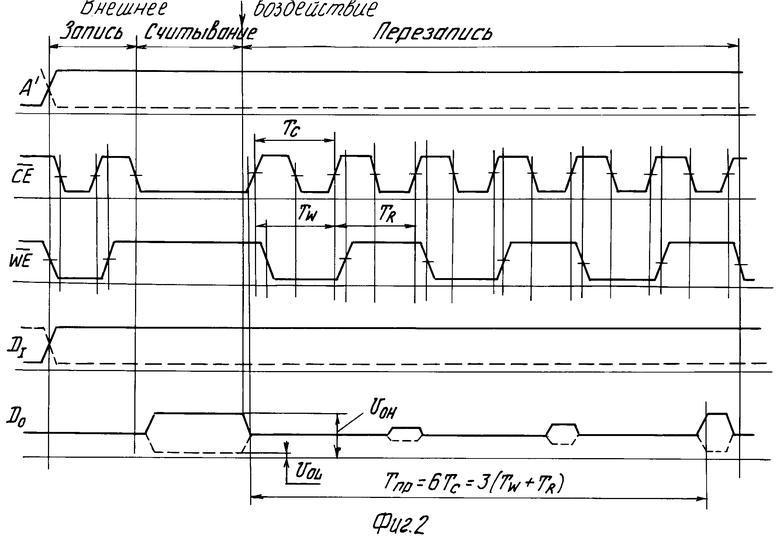

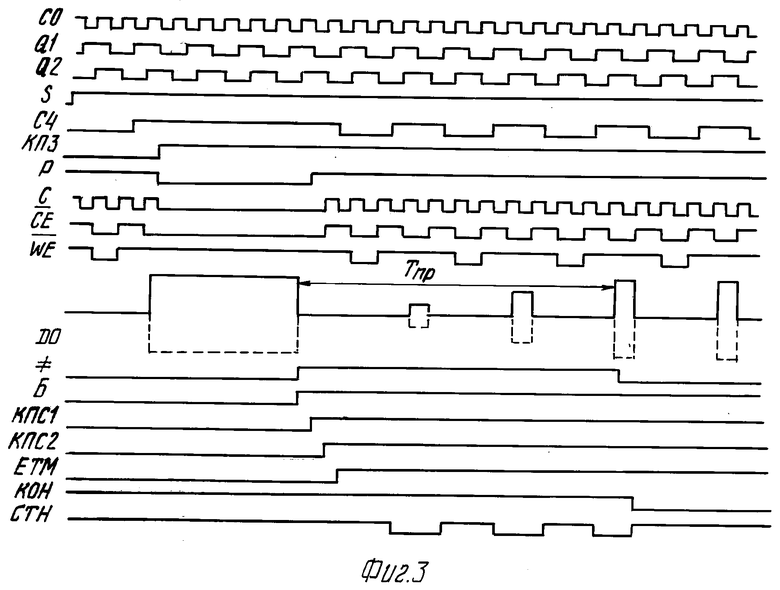

Принцип работы устройства поясняют фиг.2 и 3.

На вход синхронизации устройства поступают импульсы синхронизации СО, период следования которых равен половине периода цикла записи (TW) или цикла считывания (TR). Эти импульсы поступают на входы седьмого 11 и восьмого 12 триггеров, с выходов которых снимаются импульсы Q1 и Q2. На вход пуска устройства поступает сигнал пуска S, однако он задерживается вторым элементом задержки и тем самым запрещается работа девятого триггера 13 и обеспечивается режим записи устройства. Логический элемент И-НЕ 1 формирует команду Р, которая разрешает прохождение импульсов синхронизации С на вход синхронизатора, который в свою очередь формирует сигналы  и

и  , обеспечивающие запись данных D1, формируемых формирователем 4 данных по адресу, задаваемому формирователем 3 адреса. После срабатывания второго элемента 16 задержки разрешена работа девятого триггера 13, который переключается и переводит устройство в режим считывания. В результате переключаются пятый триггер 9, первый триггер 5, логический элемент И-НЕ и прерывается поступление импульсов синхронизации С на вход синхронизатора 22, останавливая его в состоянии считывания. Для предотвращения ложного срабатывания устройства, связанного с задержкой сигнала D0, в состав устройства введен первый элемент 15 задержки, который задерживает начало работы на время этой задержки. Устройство находится в этом режиме (статического считывания), пока контролируемая память не потеряет работоспособность в результате испытательного воздействия. Тогда сигнал D0 становится отличным от нормы, это фиксирует компаратор 23, и на выходе первого логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 2 появляется сигнал≠, который через первый логический элемент И 17 устанавливает шестой триггер 10, и на выходе второго триггера 6 формируется команда КПС1. В результате этого, во-первых, логический элемент И-НЕ 1 вырабатывает команду Р, которая разрешает поступление импульсов синхронизации С на вход синхронизатора и совместно с вторым логическим элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 19 обеспечивает переключение девятого триггера 13, обеспечивая тем самым режим перезаписи устройства, во-вторых, третий триггер 7 вырабатывает команду КПС2, в-третьих, четвертый триггер 8 вырабатывает команду ЕТМ, которая, поступая на второй логический элемент И-НЕ 21, обеспечивает прохождение на таймер 24 импульсов считывания с девятого триггера 13. Если контролируемая микросхема восстанавливает свою работоспособность, это фиксирует компаратор 23, и на выходе первого логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 2 сигнал≠ становится равным логическому "0" и запрещает тем самым прохождение импульсов считывания через второй логический элемент И-НЕ 21 на таймер 24. Таким образом, показания таймера соответствуют времени потери работоспособности, выраженной в единицах (TW+TR).

, обеспечивающие запись данных D1, формируемых формирователем 4 данных по адресу, задаваемому формирователем 3 адреса. После срабатывания второго элемента 16 задержки разрешена работа девятого триггера 13, который переключается и переводит устройство в режим считывания. В результате переключаются пятый триггер 9, первый триггер 5, логический элемент И-НЕ и прерывается поступление импульсов синхронизации С на вход синхронизатора 22, останавливая его в состоянии считывания. Для предотвращения ложного срабатывания устройства, связанного с задержкой сигнала D0, в состав устройства введен первый элемент 15 задержки, который задерживает начало работы на время этой задержки. Устройство находится в этом режиме (статического считывания), пока контролируемая память не потеряет работоспособность в результате испытательного воздействия. Тогда сигнал D0 становится отличным от нормы, это фиксирует компаратор 23, и на выходе первого логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 2 появляется сигнал≠, который через первый логический элемент И 17 устанавливает шестой триггер 10, и на выходе второго триггера 6 формируется команда КПС1. В результате этого, во-первых, логический элемент И-НЕ 1 вырабатывает команду Р, которая разрешает поступление импульсов синхронизации С на вход синхронизатора и совместно с вторым логическим элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 19 обеспечивает переключение девятого триггера 13, обеспечивая тем самым режим перезаписи устройства, во-вторых, третий триггер 7 вырабатывает команду КПС2, в-третьих, четвертый триггер 8 вырабатывает команду ЕТМ, которая, поступая на второй логический элемент И-НЕ 21, обеспечивает прохождение на таймер 24 импульсов считывания с девятого триггера 13. Если контролируемая микросхема восстанавливает свою работоспособность, это фиксирует компаратор 23, и на выходе первого логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 2 сигнал≠ становится равным логическому "0" и запрещает тем самым прохождение импульсов считывания через второй логический элемент И-НЕ 21 на таймер 24. Таким образом, показания таймера соответствуют времени потери работоспособности, выраженной в единицах (TW+TR).

Использование изобретения позволит повысить достоверность и обеспечить полноту контроля ОЗУ за счет реализации дополнительного режима контроля "запись-считывание-перезапись" с измерением фактического значения времени потери работоспособности Тпр.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство микропрограммного управления | 1989 |

|

SU1786486A1 |

| СИГНАТУРНЫЙ АНАЛИЗАТОР | 1991 |

|

RU2017209C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| УСТРОЙСТВО ОБМЕНА ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 1991 |

|

RU2020571C1 |

| УСТРОЙСТВО ДЛЯ РАЗГРАНИЧЕНИЯ ДОСТУПА ПОЛЬЗОВАТЕЛЕЙ К РАЗДЕЛАМ ТЕКСТОВЫХ ДОКУМЕНТОВ | 2001 |

|

RU2239866C2 |

| Устройство для управления считыванием графической информации | 1985 |

|

SU1357985A1 |

| УСТРОЙСТВО СЧИТЫВАНИЯ ИНФОРМАЦИИ ДЛЯ ТРАНСПОРТНОГО СРЕДСТВА | 1994 |

|

RU2083411C1 |

| Процессор быстрого преобразования Фурье | 1982 |

|

SU1086438A1 |

| Цифровой коррелятор | 1985 |

|

SU1251107A1 |

| Параллельный логический мультиконтроллер | 2016 |

|

RU2634199C1 |

Изобретение относится к вычислительной технике, к контролю запоминающих устройств. Устройство содержит элемент И - НЕ 1, первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 2, формирователь 3 адреса, формирователь 4 данных, триггеры 5 - 14, элементы 15 - 16 задержки, элементы И 17, 18, второй элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 19, элементы И - НЕ 20 - 21, синхронизатор 22, компаратор 23, таймер 24. 3 ил.

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПАМЯТИ, содержащее первый элемент И - НЕ, первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, формирователи адреса и данных, первый, второй, третий и четвертый триггеры, единичный выход первого триггера соединен с первым входом первого элемента И - НЕ, вход синхронизации второго триггера является входом синхронизации устройства, первый вход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с выходом формирователя данных и является информационным выходом устройства, отличающееся тем, что, с целью повышения достоверности контроля, в него введены триггеры с пятого по десятый, первый и второй элементы задержки, первый и второй элементы И, второй элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, второй и третий элементы И - НЕ, блок синхронизации, компаратор, таймер, первый вход второго элемента И соединен с входом синхронизации второго, седьмого и восьмого триггеров, выход второго элемента И соединен с первым входом блока синхронизации, первый и второй выходы которого являются соответственно выходами обращения и режима устройства, выход первого элемента И - НЕ соединен с вторым входом второго элемента И и первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с информационным входом девятого триггера, выход седьмого триггера соединен с входами синхронизации первого, четвертого и девятого триггеров, выход восьмого триггера соединен с входом синхронизации третьего триггера и первым входом второго элемента И - НЕ, выход которого соединен с входом синхронизации десятого триггера, информационный вход первого триггера соединен с единичным выходом пятого триггера, вход установки которого соединен с вторым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, единичным выходом девятого триггера, вторым входом второго элемента И - НЕ, первым входом третьего элемента И - НЕ и вторым входом блока синхронизации, вход первого элемента задержки соединен с единичным выходом первого триггера, выход первого элемента задержки соединен с первым входом первого элемента И, выход которого соединен с входом установки шестого триггера, выход которого соединен с информационным входом второго триггера, единичный выход которого соединен с информационными входами третьего и четвертого триггеров и вторым входом первого элемента И - НЕ, единичный выход третьего триггера соединен с третьим входом второго элемента И - НЕ, единичный выход четвертого триггера соединен с вторым входом третьего элемента И - НЕ, выход которого соединен с входом таймера, третий вход третьего элемента И - НЕ соединен с единичным выходом десятого триггера, информационный вход которого соединен с выходом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и вторым входом первого элемента И, вход второго элемента задержки является входом задания режима устройства, выход второго элемента задержки соединен с информационным входом девятого триггера, вход компаратора является информационным входом устройства, выход компаратора соединен с вторым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы формирователя адреса являются адресными выходами устройства.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля памяти | 1985 |

|

SU1367045A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1994-06-30—Публикация

1990-04-24—Подача