J5

САЭ О)

1

Изобретение относится к технике связи и может быть использовано для декодирования рекуррентных кодов совместно с четырехпозиционным двоичным каналом.

Цель изобретения - повьпиение достоверности декодирования.

На чертеже представлена схема предлагаемого устройства.

Декодер содержит первый и второй информационные входы 1 и 2, первый и второй регистры 3 и 4 сдвига, с первого по пятый полусумматоры 5- 9, первый и второй элементы ИЛИ

Выход полусумматора 5

Выход элемента

ИЛИ 10

Первый вход эйе- мента МАЖОРИТАРНОСТЬ

О 1

15

Второй вход элемента МАЖОРИТАРНОСТЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для мажоритарного декодирования имитостойких циклических кодов при трехкратном повторении комбинации | 1990 |

|

SU1709538A1 |

| Декодер мажоритарного двоичного кода | 1988 |

|

SU1566488A1 |

| Кодек несистематического сверточного кода | 1990 |

|

SU1714812A1 |

| Пороговый декодер @ -ичного кода | 1989 |

|

SU1642589A1 |

| Вероятностный мажоритарный декодер | 1986 |

|

SU1396282A1 |

| Кодек несистематического сверточного кода | 1988 |

|

SU1580567A1 |

| АДАПТИВНЫЙ ДЕКОДЕР | 2008 |

|

RU2379833C1 |

| Устройство для мажоритарного декодирования при трехкратном повторении кодовой комбинации | 1985 |

|

SU1305876A1 |

| Декодер | 1988 |

|

SU1624700A1 |

| Декодер циклического кода с исправлением ошибок и стираний | 1980 |

|

SU1083387A1 |

Изобретение Относится к технике связи и может быть использовано для декодирования циклических кодов совместно с четырехпозиционньм двоичным каналом. Целью изобретения является повьшение достоверности декодирования. Декодер содержит первый и второй информационные входы 1 и 2, первый и второй регистры 3 и 4 сдвига, с первого по пятый полусумматоры 5-9, первый и второй злементы ИЛИ 10, 11, злемент МАЖОРИТАРНОСТЬ 12, злемент И 13, управляющий вход 14, информационный выход 15. 1 ил., 1 табл. (Л

10 и 11, элемент МАЖОРИТАРНОСТЬ 12, элемент И 13, управляющий вход 14, информационный выход 15 декодера.

Декодер работает следующим образом .

На первый вход 1 декодера поступают двоичные сигналы кода, а на второй - последовательность единиц,которые соответствуют положению ненадежных разрядов кода. Работа регистров 3 и 4 тактируется внешним генератором. Входы первого и второго полусумматоров 5 и 6 подключены к выходам первого регистра в соответствии с системой проверок для некоторого информационного разряда Xj. В данном устройстве реализована следующая система проверок:

X i - YU, ©X;,, X l ,

(1)

х- X;

где X; - принятые информационные

разряды;

Y; - принятые- контрольные разряды.

Информационные и контрольные разряды размещаются в регистре в порядке увеличения индексов справа налево . Первый полусумматор 5 обеспечивает решение первого уравнения, вто рой - второго уравнения системы (l) Аналогично подключены входы первого и второго элементов ИЛИ 10 и 11 к выходам второго регистра 4.

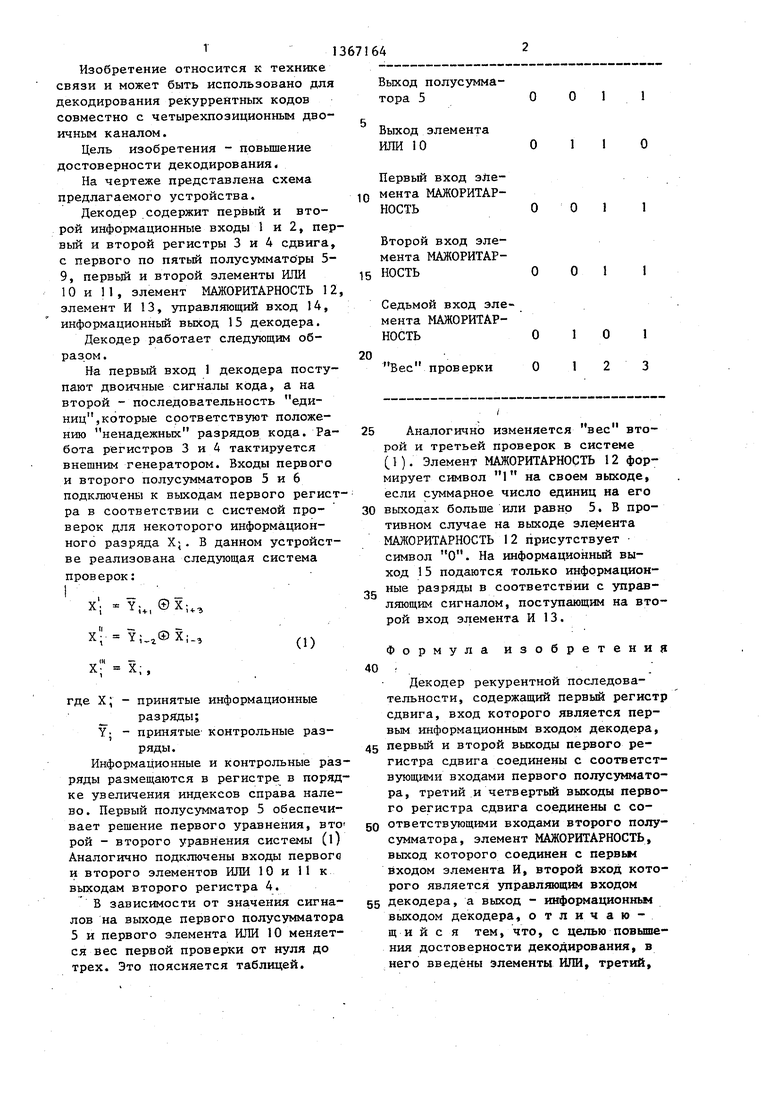

В зависимости от значения сигналов на выходе первого полусумматора 5 и первого элемента ИЛИ 10 меняется вес первой проверки от нуля до трех. Это поясняется таблицей.

Седьмой вход элемента МАЖОРИТАРНОСТЬ

Вес проверки

О

25 Аналогично изменяется вес второй и третьей проверок в системе (1). Элемент МАЖОРИТАРНОСТЬ 12 формирует символ 1 на своем выходе, если суммарное число единиц на его

30 выходах больше или равно 5. В противном случае на выходе элемента МАЖОРИТАРНОСТЬ 12 присутствует символ О. На информационный выход 15 подаются только информационные разряды в соответствии с управляющим сигналом, поступающим на второй вход элемента И 13.

35

Формула изобретения

.

Декодер рекурентной последовательности, содержащий первьй регистр сдвига, вход которого является первым информационным входом декодера,

первьй и второй выходы первого регистра сдвига соединены с соответствующими входами первого полусумматора, третий и четвертый выходы первого регистра сдвига соединены с соответствующими входами второго полусумматора, элемент МАЖОРИТАРНОСТЬ, выход которого соединен с первым входом элемента И, второй вход которого является управляющим входом

декодера, а выход - информационньм выходом декодера, отличающий с я тем, что, с целью повышения достоверности декодирования, в него введены элементы ИЛИ, третий.

313

четвертый, пятый полусумматоры и второй регистр сдвига, вход которого является вторым информационным вхо- -дом декодера, первый и второй выхо- ды второго регистра сдвига подключены к соответствующим входам первого элемента ШШ, третий и четвертый выходы второго регистра сдвига подключены к соответствующим входам второго элемента Ш1И, выход первого элемента ШШ подключен к первому входу третьего полусумматора, второй вход которого объединен с пер- вьм и вторым входами элемента МАЖО- РИТАРНОСТЬ и подключен к выходу первого полусумматора, выход второго

64

элемента ИЛИ подключен к первому входу четвертого полусуматора, второй вход которого объединен с третьим и четвертьы входами элемента МАЖОРИТАРНОСТЬ и подключен к выходу второго полусумматора, пятый выход первого регистра сдвига соединен с первым входом пятого полусумматора и пятым и шестым входами элемента МАЖОРИТАРНОСТЬ, пятый выход второго регистра сдвига соединен с вторьм входом пятого полусумматора, выходы третьего, четвертого и пятого полусумматоров соединены соответственно с седьмым, восьмым и девятьм входами элемента МАЖОРИТАРНОСТЬ.

| Бородин Л.Ф | |||

| Введение в теорию помехоустойчивого кодирования | |||

| М.: Сов.радио, 1968, с.257, фиг.11.4. |

Авторы

Даты

1988-01-15—Публикация

1986-03-07—Подача