СО

а

00

сх 1

рандов содержит группу модулей 1 сдвига, дешифратор нуля и преобразователь прямого кода в дополнительный код. Причем каждый модуль 1 сдвига включает мультипт ексоры 12 и 13, узел 14 односторонних сдвигов, схему

15 сравнения, элемент НЕ 16, элемент H-ILIH 17 и элементы И 19 и 2U. Кроме того, каждьш модуль 1 сдвига дополнительно содержит элемент И-ИЛИ 18, элементы Н 21 и 22 и группу элементов ИЛИ 23с соответствующими се язями. 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования сигналов четности при сдвигах двоичных кодов | 1989 |

|

SU1783527A1 |

| Модуль для сдвига операндов | 1988 |

|

SU1617434A1 |

| Устройство для сдвига операндов | 1987 |

|

SU1481741A1 |

| Устройство для сдвига операндов | 1988 |

|

SU1633391A1 |

| Устройство для сдвига операндов | 1986 |

|

SU1368873A1 |

| Устройство для сдвига операндов | 1986 |

|

SU1330626A1 |

| Устройство для предсказания четности результата сдвигателя | 1988 |

|

SU1649545A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ПРЕДСКАЗАННЫХ СИГНАЛОВ ЧЕТНОСТИ ПРИ СДВИГАХ ДВОИЧНЫХ КОДОВ | 1992 |

|

RU2045772C1 |

| Устройство для сдвига информации с контролем | 1985 |

|

SU1297055A1 |

| Устройство для сдвига информации с контролем | 1985 |

|

SU1325481A1 |

Изобретение относится к вычислительной технике и может быть использовано в высокопроизводительных системах обработки информации. Целью изобретения является расширение функциональных возможностей за счет выполнения арифметических сдвигов вправо. Поставленная цель достигается тем, что устройство для сдвига опе

1

Изобретение относится к вычислительной технике и может быть использовано в высокопроизводительных системах обработки информации.

Цель изобретения - расширение функгщональных возможностей за счет выполнения арифметических сдвигов вправо.

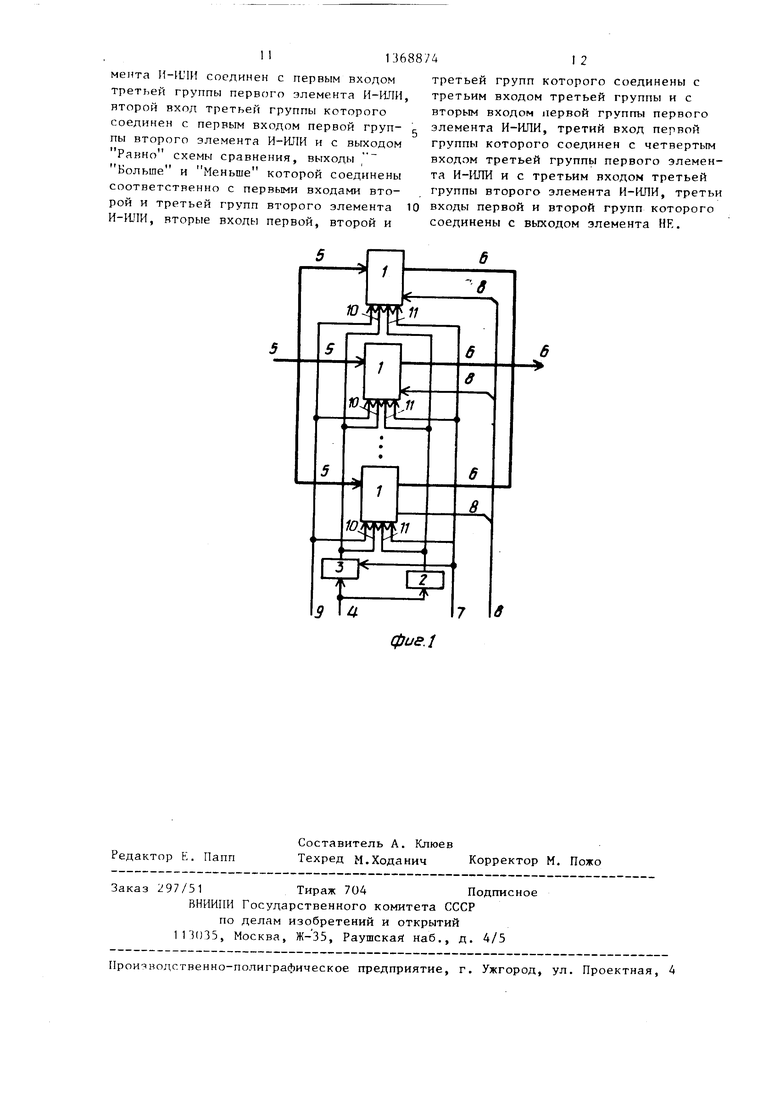

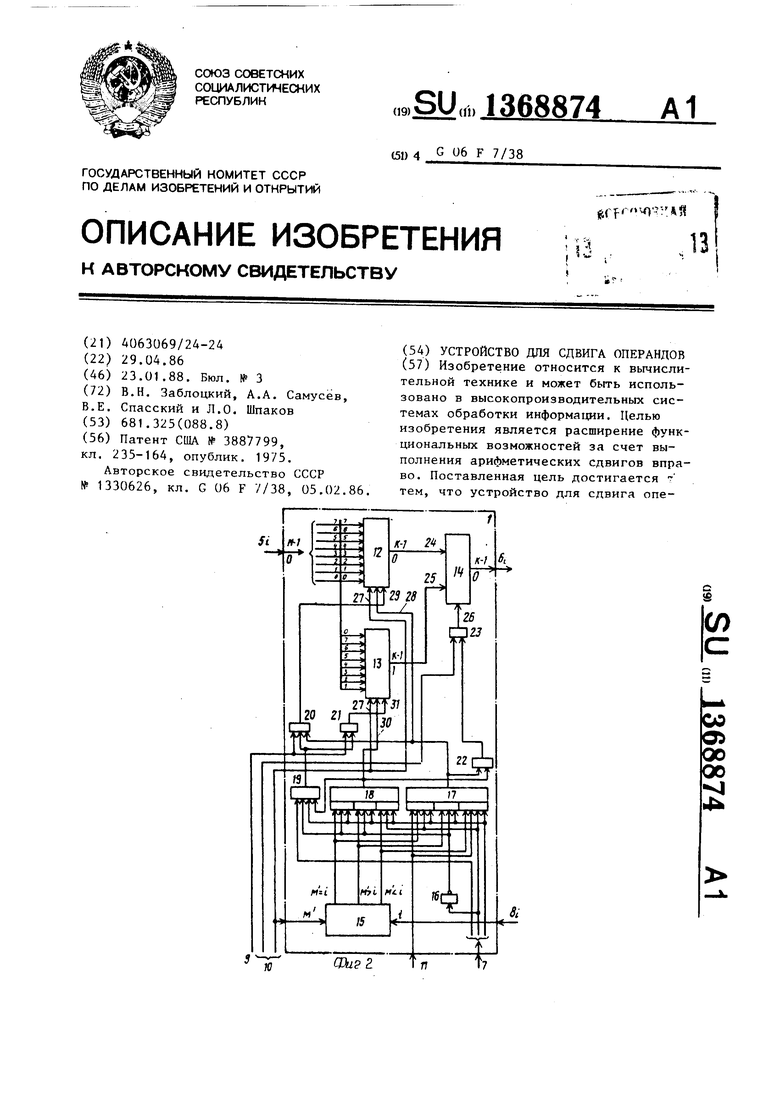

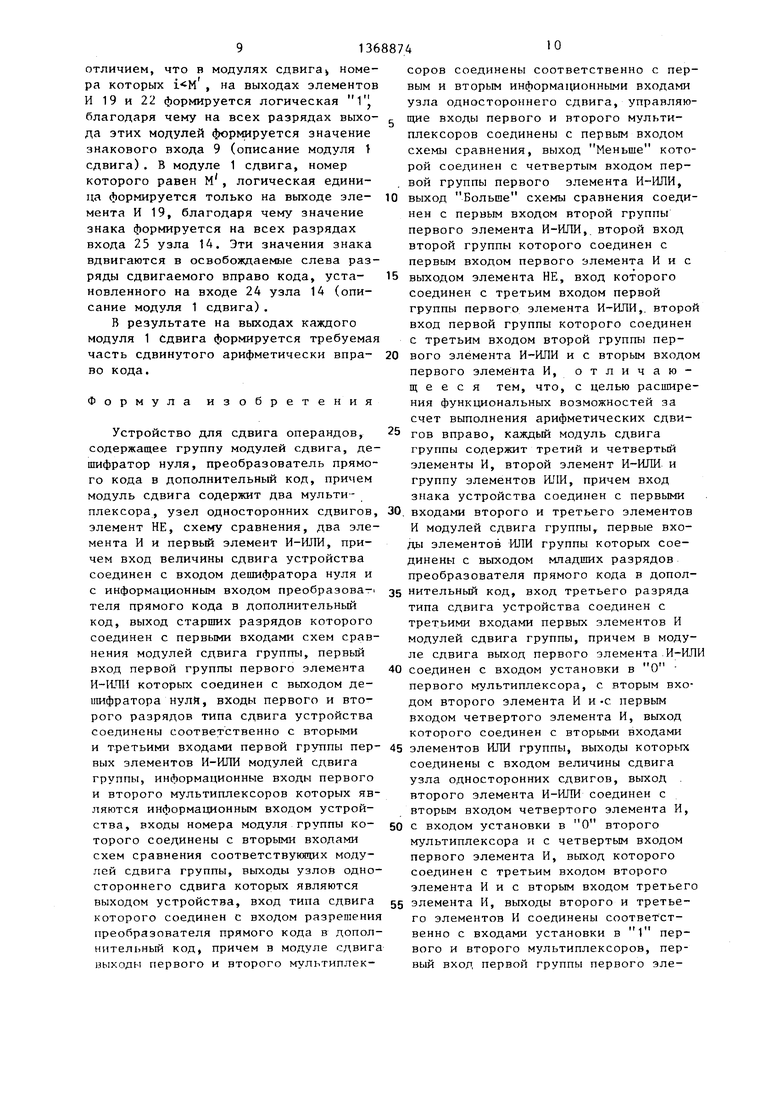

На фиг.1 изображена схема устройства для сдвига операндов, на фиг.2- схема модуля сдвига.

Устройство для сдвига операндов (фиг.1) содержит группу модулей 1 сдвига, дешифратор 2 нуля, преобразователь 3 прямого кода в дополнительный код, входы 4 величины сдвига устройства, информационный вход 5 устройства, выход 6 устройства, вход 7 типа сдвига устройства, группу входов 8 номера модуля устройства, вход 9 знака устройства, входы 10 и 11 соответственно величины сдвига и разрешения сдвига модулей 1 сдвига группы.

Модуль 1 сдвига (фиг.2) содержит мультиплексоры 12 и 13, узел 14 односторонних сдвигов, схему 15 сравнения, элемент НЕ 16, элемент И-ИЛИ 17 и 18, элементы И 19-22, группу элементов ИЛИ 23, .информационные входы 24 и 25 и управляющий вход 26 узла 14 односторонних сдвигов, управляющий вход 27 мультиплексоров 12 и 13, входы 28 и 29 установки в нуль и установки в единицу мультиплексора 12,

ВХОДЫ 30 и 31 установки в нуль и установки в единицу мультиплексора 13.

Модуль 1 сдвига предназначен для формирования части сдвинутого кода на группе разрядов выхода 6 устройства с учетом кода величины сдвига, формируемого на входе 10, кода типа сдвига, устанавливаемого на входе 7, сигнала (Лог.О) равенства или нера

0

0

5

5

Ог

0

венства (Лог.1) нулю всего кода величины сдвига, формируемого на входе 11, и кода настройки, установленного на входе 8. Кроме этого, модуль сдвига может быть использован как К-раз- рядный мультиплексор с управляющим входом, содержащим старшие разряды входов 10. При- этом на младших разрядах входа 10 постоянно устанавливаются логические О, на всех разрядах входа 8 постоянно устанавливается логическая 1, на входе 11 постоянно устанавливается логический О, на входе 7 постоянно устанавливается код логического сдвига вправо. В этом случае на выход 6 передается код с группы разрядов входа 5, номер которой равен значению кода, установленного на старших разрядах входа 10, (К - целое число, , N - количество разрядов информа1р1онного входа 5 устройства).

Модуль 1 сдвига может быть использован в качестве К-разрядного устройства логических и арифметических сдвигов с входным мультиплексором. В этом случае на младших разрядах входа 10 устанавливается код величины сдвига, на вход 7 - код типа сдвига (логического влево или логического или арифметического вправо). При этом при задании логического сдвига влево на младших разрядах входа 10 устанавливается дополнительный код величины сдвига, отличный от нулевог о, а на старших разрядах входа 10 устанавливается код со значением на единицу меньшим номера группы разрядов входа 5. На входе 11 устанавливается логическая 1, л на всех разрядах входа 8 - код М .

При логических (арифметических) сдвигах вправо на всех разрядах входа

313

8 устанавливается код М , а на входе 10 устанавливаются коды без преобра - зований. При этом, для выполнения арифметических сдвигов вправо на вхо де 9 устанавливается код знака, а на входе 7 - соответствующий код типа сдвига. Элемент И 21 пропускает значение кода знака с входа 9 на вход 31, оно поступает также на выход г группы элементов ИЛИ 23. В результате на всех разрядах входа 25 узла 14 формируется значение знака и при сдвиге вправо код знака с входа 25 вдвигается в освобождаемые разряды слева на выходе 6.

Мультиплексор 12 предназначен для передачи на вход 24 узла 14 требуемых групп сигналов входного сдвигаемого кода с входа 5 устройства под управлением кода, устанавливаемого на старших разрядах входа 10, при уста

новке логического О на входах 28 и 29. При установке на входе 28 логической 1 на всех разрядах входа 24,- кроме крайнего левого разряда, устанавливается логический О. Значение сигнала на крайнем левом разряде входа 24 может задаваться сигналом с входа 29. При логическом О (1) на входе 29 на крайнем левом разряде входа 24 формируется логический О (1).

Мультиплексор 13 предназначен для

40

передачи на вход 25 узла 14 требуемых 35 знака. На входе 8 устанавливается код групп сигналов входного сдвигаемого кода с входа 5 устройства под управлением кода на старших разрядах входа 10 при установке логического О на входах 30 и 31. При установке на входе 30 логической 1 на всех разрядах входа 25 устанавливается логический О (1) при установке на , входе 31 логического О (1).

Номер группы сигналов, передаваемых на вьгход мультиплексора 12 с входа 5, равен значению кода, сформированного на старших разрядах входа 10. Номер группы сигналов, передаваемых на выход мультиплексора 13 с вхо- 50 да 5 на единицу больше значения кода, установленного на входе 10. При равенстве кода на старших разрядах

N Г -1 -,1), на выход передают- gg

ся сигналы нулевой группы сигналов с входа 5. В данном случае номер группы сигналов равен номеру соответствующей группы разрядов входа 5,

настройки, значение которого равно номеру (i) модуля сдвига в устройстве.

Для случаев, когда на выходах элементов И-ИЛИ 17,18 и И 19, 22 формируется логический О, код с младших разрядов входа 10 транзитом передается на вход 26, элементы И 20 и 21 заблокированы, т.е. на их выходах устанавливается логический О. Под воз- 45 действием кода, сформированного на старших разрядах входа К), на входы

24и 25 осуществляется передача кода, установленного на группах разрядов входа 5.

При установке на входах 28 и 30 логической 1, при логическом О на выходах элементов И 19 и 22, на всех разрядах входов 24 и 25 формируются логические О. При этом, при установке на выходе элемента И 19 логической 1 на всех разрядах входа

25устанавливается код знака через элемент И 21. Код знака устанавливается также на крайнем левом разряде

на которых эти сигналы сформированы. Указанная передача сигналов ос т;ест- вляется только при установке логического О на входах 28-31.

Узел 14 односторонних сдвигов предназначен для сдвига вправо кода, формируемого на входе 23, на величину разрядов (бит), определяемую значением кода на входе 26 узла, с вдвиганием в освобождаемые слева разряды соответствующей правой части кода, сформированного на входе 25. На выходе узла 14 формируется сдвинутый К-разрядный код. Узел 14 может быть построен аналогично известному. В устройстве и моделе сдвига вьтолняются следующие операции. ЦП - циклический сдвиг вправо, ЦЛ - циклический сдвиг влево, ЛП

логический сдвиг вправо, ЛЛ - логический сдвиг влево, АП - арифметический сдвиг вправо. Обозначения ЦП, ЦП, Ж, ЛЛ, АП соответствуют кодам соответственно 000, 010, 001, 011, 101, устанавливаемым на входе 7.

Модуль 1 сдвига функционирует следующим образом.

На входе 10 устанавливается код величины сдвига, на входе 11 формируется сигнал логического О при равенстве значения кода на входе 10 нулю и сигнал логической 1 в противном случае. На входах 7 и 9 формируется код соответственно типа сдвига и

знака. На входе 8 устанавливается код

настройки, значение которого равно номеру (i) модуля сдвига в устройстве.

Для случаев, когда на выходах элементов И-ИЛИ 17,18 и И 19, 22 формируется логический О, код с младших разрядов входа 10 транзитом передается на вход 26, элементы И 20 и 21 заблокированы, т.е. на их выходах устанавливается логический О. Под воз- действием кода, сформированного на старших разрядах входа К), на входы

24и 25 осуществляется передача кода, установленного на группах разрядов входа 5.

При установке на входах 28 и 30 логической 1, при логическом О на выходах элементов И 19 и 22, на всех разрядах входов 24 и 25 формируются логические О. При этом, при установке на выходе элемента И 19 логической 1 на всех разрядах входа

25устанавливается код знака через элемент И 21. Код знака устанавливается также на крайнем левом разряде

«

входа 24 через элемент И 20 при формировании логической 1 одновременн на выходах элементов И-ИЛИ 17 и 19. Это необходимо при выполнении в уст- ройстве арифметических сдвигов вправо для формирования на всех разрядах выхода 6 кода знака при М i. При этом код, на всех разрядах которого сформировано значение знака, с входа 25 вдвигается в (К-1) левых разрядов выхода 6, так как на входе 26 узла 14 сформирован единичный код с максимальным значением, равным (К-1),

20

25

благодаря формированию на выходе эле- 15 сдвига - ЦП, 1Ш, ЛП, АП, ЛЛ. Значение

(М„) кода величины сдвига может находиться в пределах П СМ-K+m)(N-l). При этом значение М представляет собой значение части кода, формируемой на старших разрядах входа 4 и задающей К-кратные сдвиги.Значение га представляет собой значение части кода, формируемой на младших разрядах входа 4 и задающей битные сдвиги.

На выходе 6 устройства формируется сдвинутый код операнда, код которого установлен на входе 5. При равенстве и на выходе дешифратора 2 формируется логический О, который подается на вход 11 всех модулей 1 сдвига. р;сли при этом на входе 7 ус-, тановлен код ЛЛ, выполняется передача транзитом с входа 5 на выход 6 устройства. При установке на входе 7 35 кодов ЦП, ЛП, АП, ЦП значение сигнала на выходе дешифратора 2 не влияет на функционирование устройства и . транзитная передача кода с входа 5 на выход 6 обеспечивается благодаря передаче нулевого кода с входа 4 на

мента И 22 логической 1. В крайний же правый разряд выхода 6- передается значение знака с крайнего левого разряда входа 24 узла 14.

ПриМ 1 на выходах элементов И-ИЛИ 17 и 22 устанавливается логический О, а при арифметических сдвигах на выходах элементов И-ИЛИ 13 и 12 устанавливается логическая 1. В этом случае значение знака с входа 25 вдвигается в освобождаемые разряды сдвинутого кода на выходе 6. При М : i модуль 1 сдвига функционирует как описано выше при формировании на выходах элементов И-ИЛИ 17,18 и и 19,22 логического О.

Преобразователь 3 предназначен для пропускания кода с входа 4 на выход без изменений при установке на входе

7кода ЛП, АП и 1Щ и для формирования на выхс1де дополнительного кода при установке на входе 17 кода ЦЛ или ЛЛ. При равенстве значения кода на входе 4 нулю на выходе дешифратора 2 формируется логический О, В противном случае на выходе дешифратора 2 формируется логическая 1.

Для обеспечения работоспособности устройства вход 5 устройства необходимо соответствующим образом подключить к информационному входу каждого модуля 1 сдвига. Правило указанного подключения заключается в следующем.

8каждом i-M модуле сдвига разряды j-й группы разрядов информационного входа модуля сдвига соединяют с разрядами 1-й группы разрядов информа- ii ioHHoro входа устройства с сохранением порядка расположения разряда в группах разрядов, где

30

40

ВЫХОД преобразователя 3 и входы 11 модулей 1, а также кодам -ПП и ПЛ на входе 7.

45

Если М О или m О, то на выходе дешифратора 4 устанавливается логическая 1 и устройство функционирует следующим образом.

При циклическом сдвиге вправо в 50 каждом i-M модуле сдвига на выход мультиплексора 12 передаются сигналы с а-й группы разрядов информационного входа устройства, где

55

isM

1-м, если

i.,

--1

, если

Nr f. ..

, если KJ

Устройство работает следующим образом.

Исходное состояние устройства может быть произвольным. Для осущест- вления сдвига операнда код его устанавливается на входе 25 устройства. На входе 4 устройства устанавливается код величины сдвига. На входе 7 устройства устанавливается код типа

ВЫХОД преобразователя 3 и входы 11 модулей 1, а также кодам -ПП и ПЛ на входе 7.

45

Если М О или m О, то на выходе дешифратора 4 устанавливается логическая 1 и устройство функционирует следующим образом.

При циклическом сдвиге вправо в 50 каждом i-M модуле сдвига на выход мультиплексора 12 передаются сигналы с а-й группы разрядов информационного входа устройства, где

isM

1-м, если

iNr

JKL если

а на выход мультиплексора 13 передаются сигналы б-й группы разрядов информационного входа, где

б

1 - (М+1), если iiM+1 -(М+1-i), если ,

J К L

10

так как код с входа 4 передается транзитом на входы 10 модулей 1. В узле 14 односторонних сдвигов осу- 11ествляется сдвиг вправо на га разрядов кода с а-й группы разрядов входа 5 с вдвиганием в освобождаемые разряды соответствующей правой части кода с б-й группы разрядов .входа 5 устройства. В результате на выходах каждого модуля сдвига формируется требуемая часть сдвинутого циклически вправо кода. Совокупность частей кода на выходах всех модулей сдвига образует полный сдвинутый циклически вправо код.

При циклическом сдвиге влево в преобразователе 3 осуществляется прв образование кода в -дополнительный код. В результате на вход 10 величины сдвига модулей 1 подается код

( если , или ( -(М+1) (К-га) , если m 0.. При этом в каждом i-M модуле сдвига при на выход мультиплексора 12. передаются сигналы в-й группы разрядов входа 5 устройст- 35 ва, где

в

а на вход мультиплексора 13 передаются сигналы г-й группы разрядов, где

г

M+i-1,

При номера виг будут равны: 1-(-(М+1)),если1 Х -(М-И)) M+H-i, если i((М+1)) 1-(-М),если ) M+i, если i(-M).

Если , то узел 14 односторонних сдвигов i-ro модуля сдвига транзитом, передает код с входа 24, и, следовательно, с в-й группы разрядов входа 5 устройства на выход 6 устройства Если , то код с входа 24 передается на выход 6 со сдвигом вправо на величину, равную (К-т) бит, с вдвиганием в освобождаемые разряды соответствующей правой части кода с входа 25, и, следовательно, с г-й группы разрядов входа 5 устройства. В ре-, зультате на выходе каждого модуля 1 15 сдвига формируется соответствующая часть циклически сдвинутого влево кода. Совокупность частей кода на выходе всех модулей сдвига образует полный код, сдвинутый 1щклически 20 влево.:

При логическом сдвиге вправо устройство функционирует так же как . при циклическом сдвиге вправо с тем отличием, что.в модулях 1 сдвига, но- 25 мера которых i«:M , осуществляется блокировка выходов мультиплексоров 12 и 13, а при только выхода мультиплексора 13, так как на выходе элемента И-ИЛИ 18 модулей 1 сдвига 30 формируется единица.

В результате на выходе 6 устройства формируется логически- сдвинутый вправо код.

При логическом сдвиге влево устройство функционирует так же, как и при циклическом сдвиге влево с тем отличием, что в модулях 1 сдвига, г - -М) при

если i() , и i((M+1)) при , осуществляется блокировка выходов мультиплексоров 12 и 13 так как на вьпсодах элементов И-ИЛИ 17 и 18 формируется логическая 1, В модуле 1 сдвига с

. тКГ .. - . /iNr номером при и ,

если () -(М+1)) при осуществляется блокировка выхода только мультиплексора 50

i - ( -М), если i5.(-M) M+i, .

i - (| -М+1),если i()

45

в

г

12 с формированием на всех разрядах логического О, так как только на. выходе элемента И-ИЛИ 17 формируется логическая 1.

В результате на выходе 6 устройст- gc ва формируется логически сдвинутый влево код.

При арифметическом сдвиге вправо устройство функционирует так же, как и при логическом сдвиге вправо с тем

(М+1)) при осуществляется блокировка выхода только мультиплексора

12 с формированием на всех разрядах логического О, так как только на. выходе элемента И-ИЛИ 17 формируется логическая 1.

В результате на выходе 6 устройст- ва формируется логически сдвинутый влево код.

При арифметическом сдвиге вправо устройство функционирует так же, как и при логическом сдвиге вправо с тем

отличием, что в модулях сдвига номера которых , на выходах элементов И 19 и 22 формируется логическая 1 благодаря чему на всех разрядах выхода этих модулей формируется значение знакового входа 9 (описание модуля сдвига). В модуле 1 сдвига, номер которого равен М , логическая единица формируется только на выходе элемента И 19, благодаря чему значение знака формируется на всех разрядах входа 25 узла 14. Эти значения знака вдвигаются в освобождаемые слева разряды сдвигаемого вправо кода, установленного на входе 24 узла 14 (описание модуля 1 сдвига).

В результате на выходах каждого модуля 1 Сдвига формируется требуемая часть сдвинутого арифметически вправо кода.

Формула изобретения

Устройство для сдвига операндов, содержащее группу модулей сдвига, дешифратор нуля, преобразователь прямого кода в дополнительный код, примем модуль сдвига содержит два мультиплексора, узел односторонних сдвигов, элемент НЕ, схему сравнения, два элемента И и первый элемент И-ИЛИ, причем вход величины сдвига устройства соединен с входом дешифратора нуля и с информационным входом преобразова-i теля прямого кода в дополнительный код, выход старших разрядов которого соединен с первыми входами схем сравнения модулей сдвига группы, первый вход первой группы первого элемента И-ИПИ которых соединен с выходом дешифратора нули, входы первого и второго разрядов типа сдвига устройства соединены соответственно с вторыми

и третьими входами первой группы пер- 45 элементов ИЛИ группы, выходы которых

вых элементов И-ИЛИ модулей сдвига группы, информационные входы первого и второго мультиплексоров которых являются информационным входом устройства, входы номера модуля группы которого соединены с вторыми входами схем сравнения соответствующих модулей сдвига группы, выходы узлов одностороннего сдвига которых являются выходом устройства, вход типа сдвига которого соединен с входом разрешения преобразователя прямого кода в дополнительный код, причем в модуле сдвига 13ЫХОДЫ первого и второго мультиплексоров соединены соответственно с первым и вторым информационными входами узла одностороннего сдвига, управляющие входы первого и второго мультиплексоров соединены с первым входом схемы сравнения, выход Меньше которой соединен с четвертым входом первой группы первого элемента И-ИЛИ,

выход Больше схемы сравнения соединен с первым входом второй группы первого элемента И-ИЛИ,. второй вход второй группы которого соединен с первым входом первого элемента И и с

выходом элемента НЕ, вход которого соединен с третьим входом первой группы первого элемента И-ИЛИ,. второй вход первой группы которого соединен с третьим входом второй группы первого элемента И-ИЛИ и с вторым входом первого элемента И, отличающееся тем, что, с целью расширения функциональных возможностей за счет выполнения арифметических сдвигов вправо, каждый модуль сдвига группы содержит третий и четвертый элементы И, второй элемент И-ИЛИ и группу элементов ИЛИ, причем вход знака устройства соединен с первыми

входами второго и третьего элементов И модулей сдвига группы, первые входы элементов ИЛИ группы которьк соединены с выходом младших разрядов преобразователя прямого кода в дополнительный код, вход третьего разряда типа сдвига устройства соединен с третьими входами первых элементов И модулей сдвига группы, причем в модуле сдвига выход первого элемента.И-ИЛИ

соединен с входом установки в О первого мультиплексора, с вторым входом второго элемента И и -с первым входом четвертого элемента И, выход которого соединен с вторыми входами

соединены с входом величины сдвига узла односторонних сдвигов, выход . второго элемента И-ИЛИ соединен с вторым входом четвертого элемента И,

50 с входом установки в О второго мультиплексора и с четвертым входом первого элемента И, выход которого соединен с третьим входом второго элемента И и с вторым входом третьег

55 элемента И, выходы второго и третьего элементов И соединены соответственно с входами установки в 1 первого и второго мультиплексоров, первый вход первой группы первого элемента H-IL IM соединен с первым вхолом третьей группы первого элемента И-ИЛИ второй вход третьей группы которого соединен с первым входом первой группы второго элемента И-ИЛИ и с выходом Равно схемы сравнения, выходы Больше и Меньше которой соединены соответственно с первыми входами второй и третьей групп второго элемента И-ИЛИ, вторые входы первой, второй и

третьей групп которого соединены с третьим входом третьей группы и с вторым входом первой группы первого элемента И-ИЛИ, третий вход первой группы которого соединен с четвертым входом третьей группы первого элемента И-ШШ и с третьим входом третьей группы второго элемента И-ИЛИ, третьи входы первой и второй групп которого соединены с выходом элемента НЕ.

фие.1

| Патент США № 3887799, кл | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Сплав для отливки колец для сальниковых набивок | 1922 |

|

SU1975A1 |

| Устройство для сдвига операндов | 1986 |

|

SU1330626A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Самусёв, Шпаков | |||

Авторы

Даты

1988-01-23—Публикация

1986-04-29—Подача