Фиг.1

Изобретение относится к импульсно технике и может быть использовано в цифровой вычислительной технике.

Цель изобретения - расширение об- ласти применения за счет обеспечения формирования выходного импульса по фронту входного сигнала без дополнительного установочного сигнала, а также увеличения амплитуды выходного сигнала.

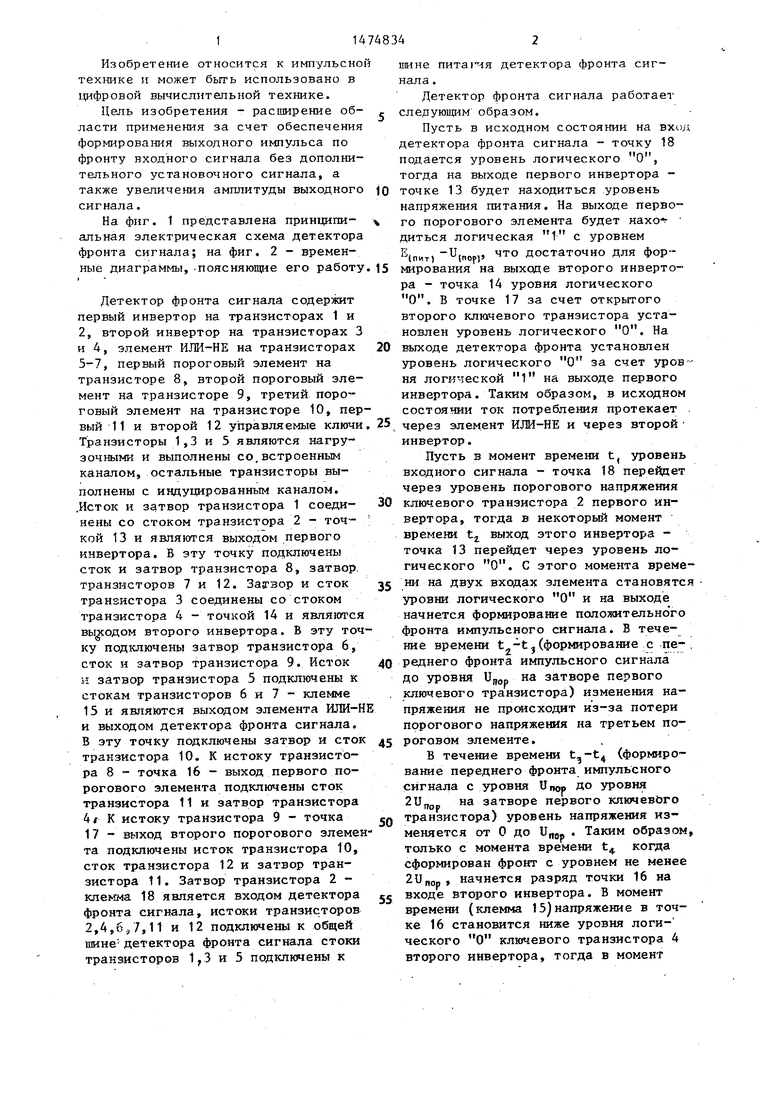

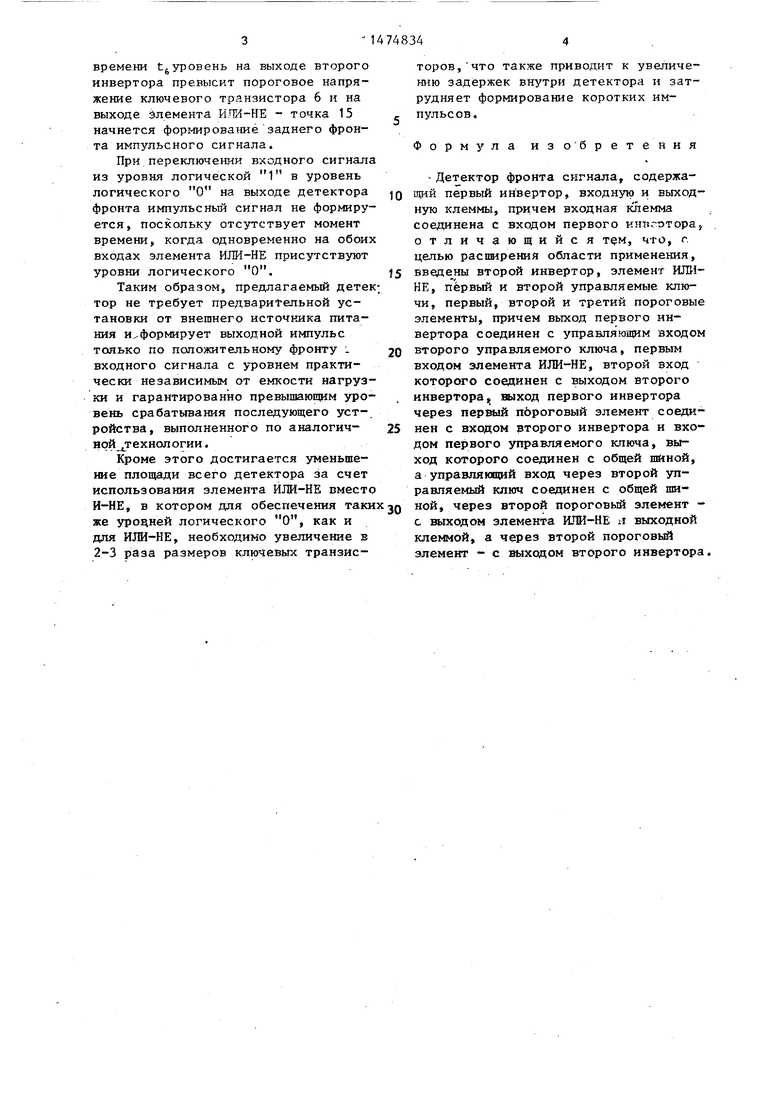

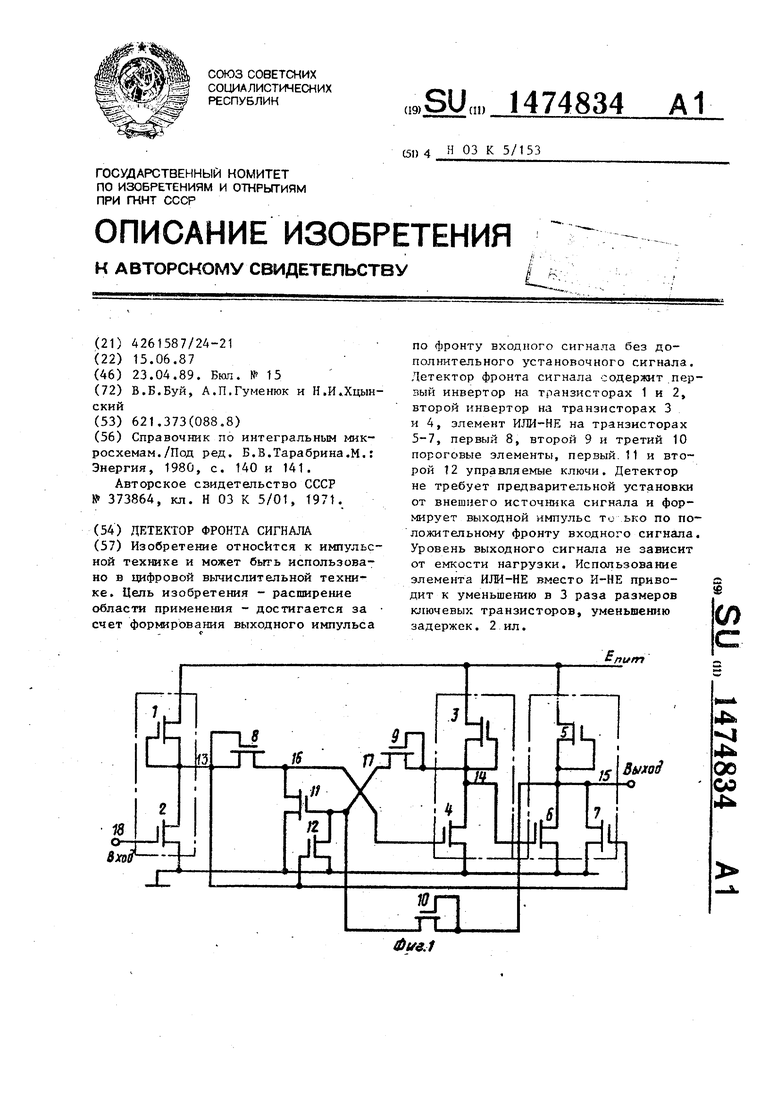

На фиг. 1 представлена принципа- альная электрическая схема детектора фронта сигнала; на фиг, 2 - временные диаграммы, поясняющие его работу

Детектор фронта сигнала содержит первый инвертор на транзисторах 1 и 2, второй инвертор на транзисторах 3 и 4, элемент ИЛИ-НЕ на транзисторах 5-7, первый пороговый элемент на транзисторе 8, второй пороговый элемент на транзисторе 9, третий пороговый элемент на транзисторе 10, первый 11 и второй 12 управляемые ключи Транзисторы 1,3 и 5 являются нагру-1 зочнымк и выполнены со.встроенным каналом, остальные транзисторы выполнены с индуцированным каналом. .Исток и затвор транзистора 1 соеди- нены со стоком транзистора 2 - точкой 13 и являются выходом первого инвертора. В эту точку подключены сток и затвор транзистора 8, затвор транзисторов 7 и 12. Заагзор и сток транзистора 3 соединены со стоком транзистора 4 - точкой 14 и являются выводом второго инвертора. В эту точку подключены затвор транзистора 6, сток и затвор транзистора 9. Исток и затвор транзистора 5 подключены к стокам транзисторов 6 и 7 - клемме 15 и являются выходом элемента ИЛИ-Н и выходом детектора фронта сигнала, В эту точку подключены затвор и сток транзистора 10. К истоку транзистора 8 - точка 16 - выход первого порогового элемента подключены сток транзистора 11 и затвор транзистора 4 К истоку транзистора 9 - точка

17 - выход второго порогового элемента подключены исток транзистора 10, сток транзистора 12 и затвор транзистора 11. Затвор транзистора 2 - клемма 18 является входом детектора фронта сигнала, истоки транзисторов ,6,7,11 и 12 подключены к общей шине детектора фронта сигнала стоки транзисторов 1,3 и 5 подключены к

шине пита}-чя детектора фронта сигнала .

Детектор фронта сигнала работает следующим образом.

Пусть в исходном состоянии на вхо детектора фронта сигнала - точку 18 подается уровень логического О, тогда на выходе первого инвертора - точке 13 будет находиться уровень напряжения питания. На выходе первого порогового элемента будет диться логическая 1 с уровнем &1пиТ) и(по() что достаточно для формирования на выходе второго инвертора - точка 14 уровня логического О. В точке 17 за счет открытого второго ключевого транзистора установлен уровень логического О. На выходе детектора фронта установлен уровень логического О за счет уров ня логической 1 на выходе первого инвертора. Таким образом, в исходном состоянии ток потребления протекает через элемент ИЛИ-НЕ и через второй инвертор.

Пусть в момент времени t( уровень входного сигнала - точка 18 перейдет через уровень порогового напряжения ключевого транзистора 2 первого инвертора, тогда в некоторый момент времени tz выход этого инвертора - точка 13 перейдет через уровень логического О. С этого момента времени на двух входах элемента становятс уровни логического О и на выходе начнется формирование положительно го фронта импульсного сигнала. В течение времени t-t(формирование с переднего фронта импульсного сигнала до уровня Uff0p на затворе первого ключевого транзистора) изменения напряжения не происходит из-за потери порогового напряжения на третьем пороговом элементе.

В течение времени (формирование переднего фронта импульсного сигнала с уровня Unm Я° уровня 2и„ на затворе первого ключевого транзистора) уровень напряжения изменяется от 0 до ипо. . Таким образом только с момента времени t4 когда сформирован фронт с уровнем не менее 2U П0р , начнется разряд точки 16 на входе второго инвертора. В момент времени (клемма 15)напряжение в точке 16 становится ниже уровня логического О ключевого транзистора 4 второго инвертора, тогда в момент

времени t6уровень на выходе второго инвертора превысит пороговое напряжение ключевого транзистора 6 и на выходе Элемента ИТИ-НЕ - точка 15начнется формирование заднего фронта импульсного сигнала.

При переключении входного сигнала из уровня логической 1 в уровень логического О на выходе детектора фронта импульсный сигнал не формируется, поскольку отсутствует момент времени, когда одновременно на обоих входах элемента ИЛИ-НЕ присутствуют уровни логического О.

Таким образом, предлагаемый детек тор не требует предварительной установки от внешнего источника питания информирует выходной импульс только по положительному фронту .

входного сигнала с уровнем практически независимым от емкости нагрузки и гарантированно превышающим уровень срабатывания последующего устройства, выполненного по аналогич- ной технологии.

Кроме этого достигается уменьшение площади всего детектора за счет использования элемента ИЛИ-НЕ вместо И-НЕ, в котором для обеспечения таких же уроцней логического О, как и для ИЛИ-НЕ, необходимо увеличение в 2-3 раза размеров ключевых транзисторов, что также приводит к увеличению задержек внутри детектора и затрудняет формирование коротких импульсов.

Формула изобретения

- Детектор фронта сигнала, содержащий первый инвертор, входную и выходную клеммы, причем входная клемма соединена с входом первого К1ш отора отличающийся тем, что, г целью распмрения области применения, введены второй инвертор, элемент ИЛИ- НЕ, первый и второй управляемые ключи, первый, второй и третий пороговые элементы, причем выход первого инвертора соединен с управляющим входом второго управляемого ключа, первым входом элемента ИЛИ-НЕ, второй вход которого соединен с выходом второго инвертора, выход первого инвертора через первый пброговый элемент соединен с входом второго инвертора и входом первого управляемого ключа, выход которого соединен с общей шиной, а управляющий вход через второй управляемый ключ соединен с общей шиной, через второй пороговый элемент - с выходом элемента ИЛИ-НЕ л выходной клеммой, а через второй пороговый элемент - с выходом второго инвертора.

ML

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство обнаружения смены адресного сигнала в интегральном исполнении на МОП-транзисторах | 1984 |

|

SU1249695A1 |

| Формирователь импульсного сигнала по переднему и заднему фронтам адресных сигналов на МОП -транзисторах | 1985 |

|

SU1381694A1 |

| Устройство формирования импульсных сигналов и уровней постоянного напряжения на МДП транзисторах | 1986 |

|

SU1370752A1 |

| Устройство формирования импульсов на МДП-транзисторах | 1986 |

|

SU1345339A1 |

| Формирователь парафазных импульсов | 1981 |

|

SU984013A1 |

| Формирователь адресных сигналов для блоков памяти | 1983 |

|

SU1163354A1 |

| Формирователь импульсов на МДП-транзисторах | 1985 |

|

SU1569973A1 |

| Сумматор | 1983 |

|

SU1101863A1 |

| Устройство считывания для многоэлементных фотоприемников инфракрасного излучения | 2016 |

|

RU2645428C1 |

| Переключатель | 1974 |

|

SU540377A1 |

Изобретение относится к импульсной технике и может быть использовано в цифровой вычислительной технике. Цель изобретения - расширение области применения - достигается за счет формирования выходного импульса по фронту входного сигнала без дополнительного установочного сигнала. Детектор фронта сигнала содержит первый инвертор на транзисторах 1,2, второй инвертор на транзисторах 3,4, элемент ИЛИ-НЕ на транзисторах 5,6,7, первый пороговый элемент 8, второй пороговый элемент 9, третий пороговый элемент 10, первый управляемый ключ 11, второй управляемый ключ 12. Устройство не требует предварительной установки от внешнего источника сигнала и формирует выходной импульс только по положительному фронту входного сигнала. Уровень выходного сигнала не зависит от емкости нагрузки. Использование элемента ИЛИ-НЕ вместо И-НЕ привело к уменьшению в 3 раза размеров ключевых транзисторов, уменьшению задержек. 1 ил.

W

11

15

to tj

Фив. 2

| Справочник по интегральным микросхемам | |||

| /Под ред | |||

| Б.В.Тарабрина.М.: Энергия, 1980, с | |||

| Способ закалки пил | 1915 |

|

SU140A1 |

| 8СЕСОЮЗМАЯ i | 0 |

|

SU373864A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-04-23—Публикация

1987-06-15—Подача