Изобретение относится к вычислительной технике, в частности к микропрограммным устройствам управления, и может быть использовано для построения программируемых устройств управления.

Цель изобретения - сокращение объема оборудования.

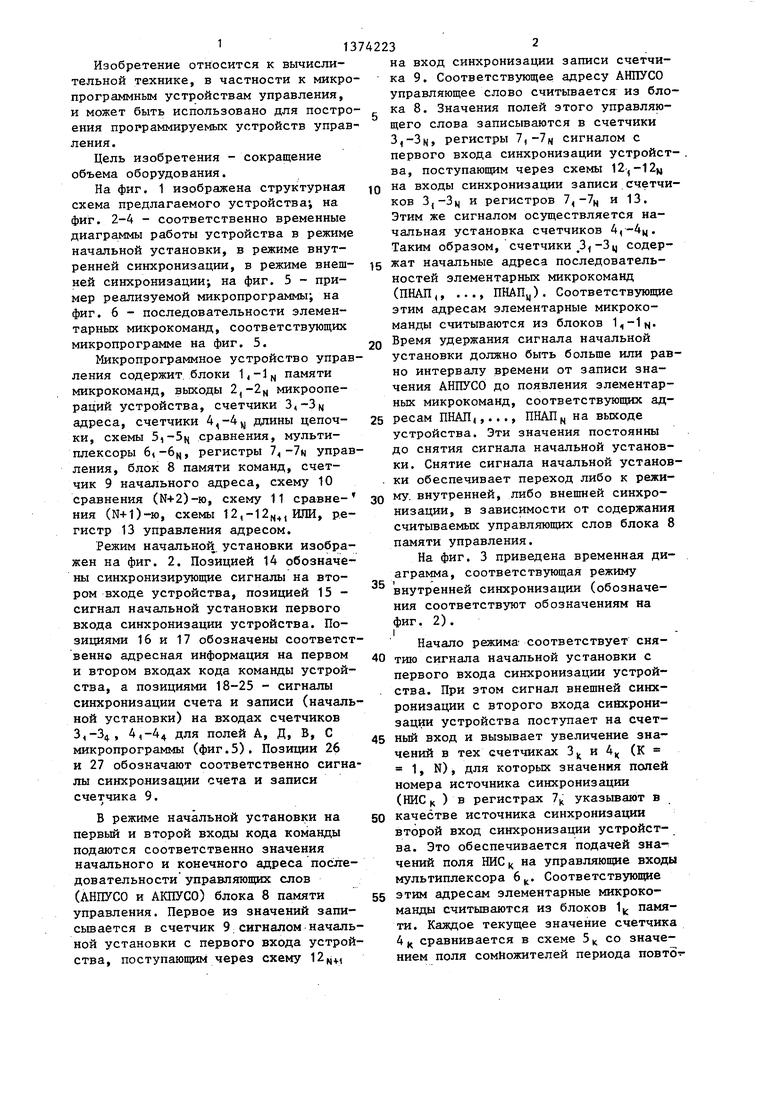

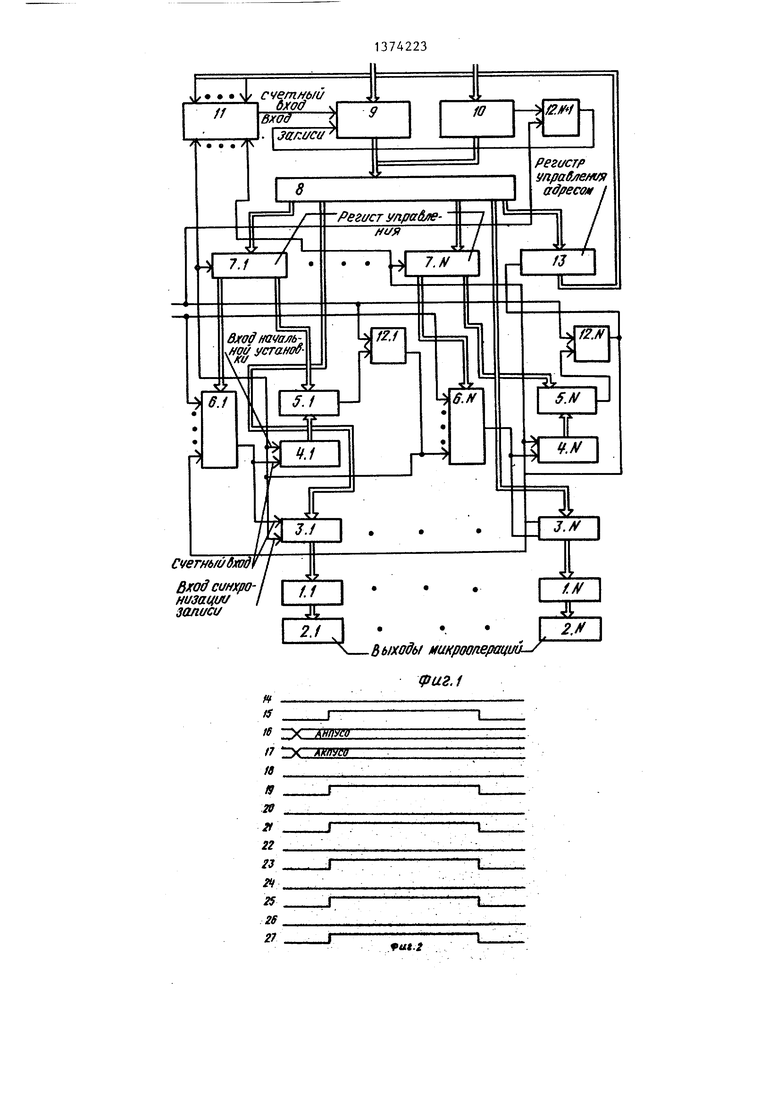

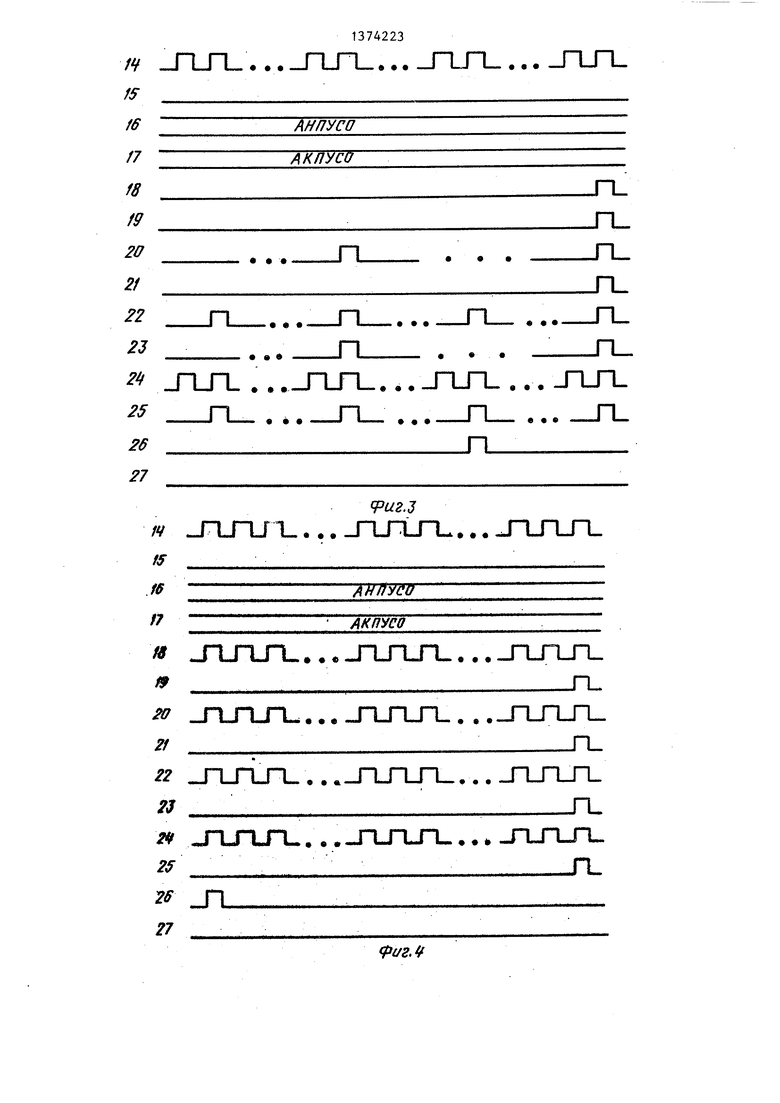

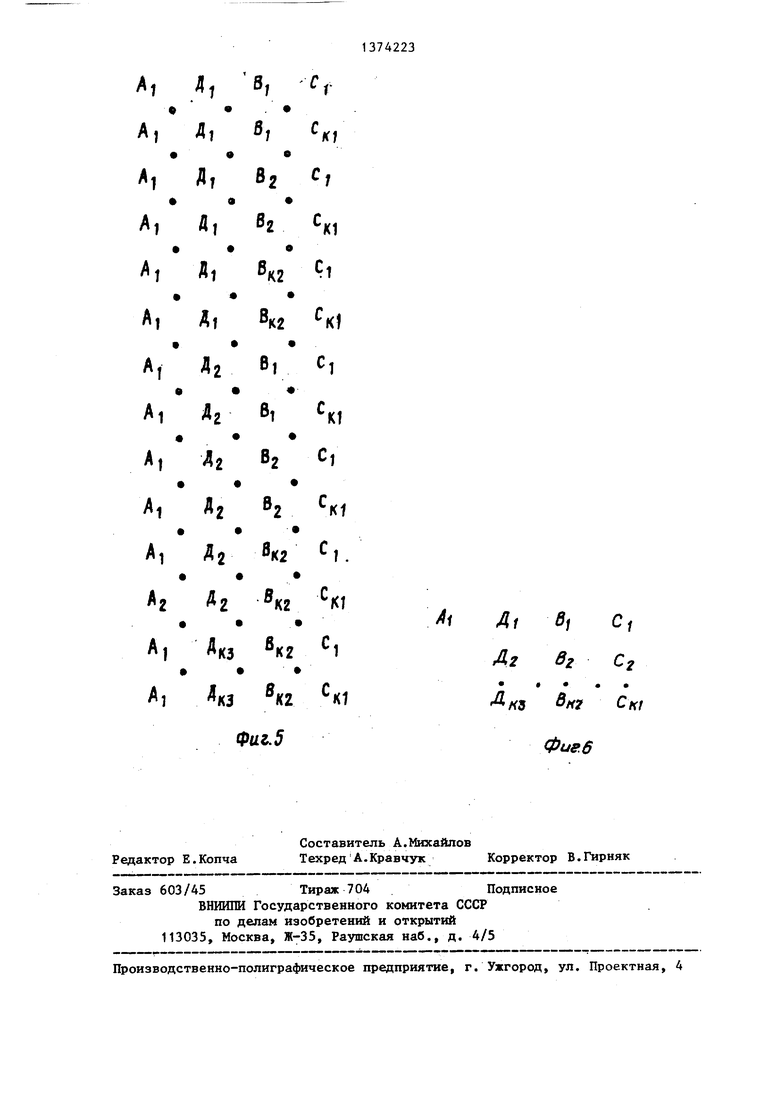

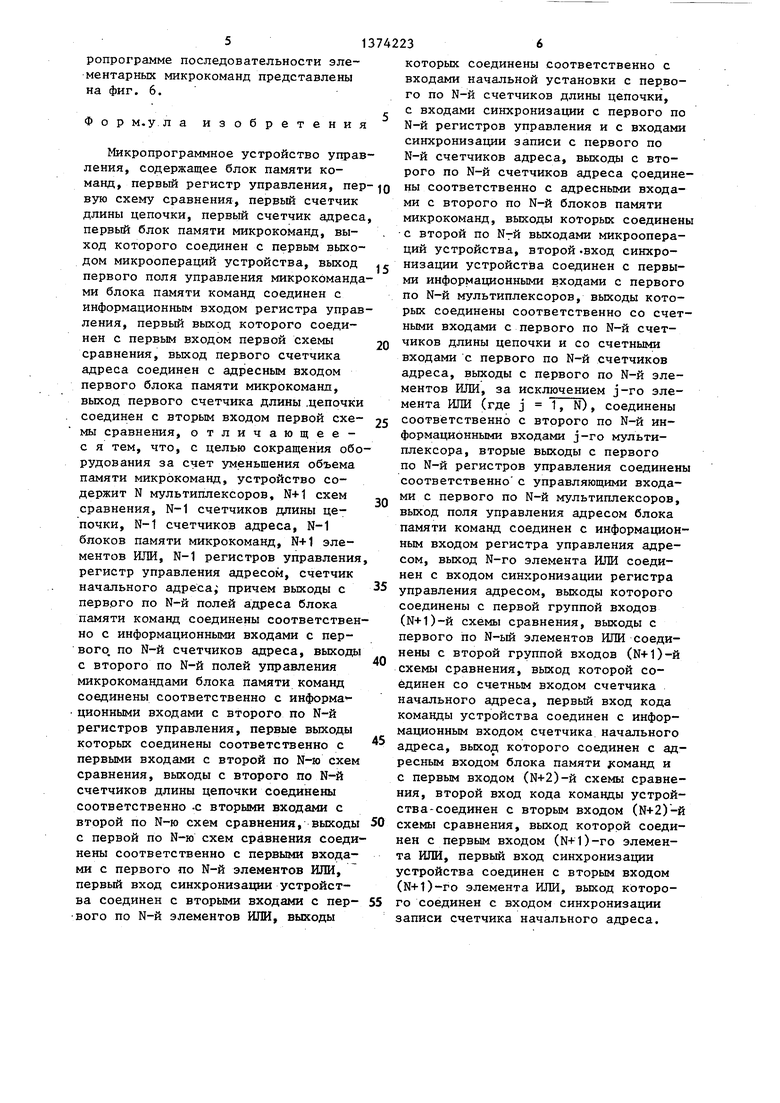

На фиг. 1 изображена структурная схема предлагаемого устройства; на фиг. 2-4 - соответственно временные диаграммы работы устройства в режиме начальной установки, в режиме внутренней синхронизации, в режиме внешней синхронизации; на фиг. 5 - пример реализуемой микропрограммы; на фиг. 6 - последовательности элементарных микрокоманд, соответствующих микропрограмме на фиг. 5.

Микропрограммное устройство управления содержит, блоки памяти микрокоманд, выходы 2,-2 микроопераций устройства, счетчики 3,-3 адреса, счетчики 4,-4, длины цепочки, схемы 5i-5n сравнения, мультиплексоры 6,-6, регистры (д управления, блок 8 памяти команд, счетчик 9 начального адреса, схему 10 сравнения (N+2)-ro, схему 11 сравне- ния (N+l)-ro, схемы 12,-12, ИЛИ, регистр 13 управления адресом.

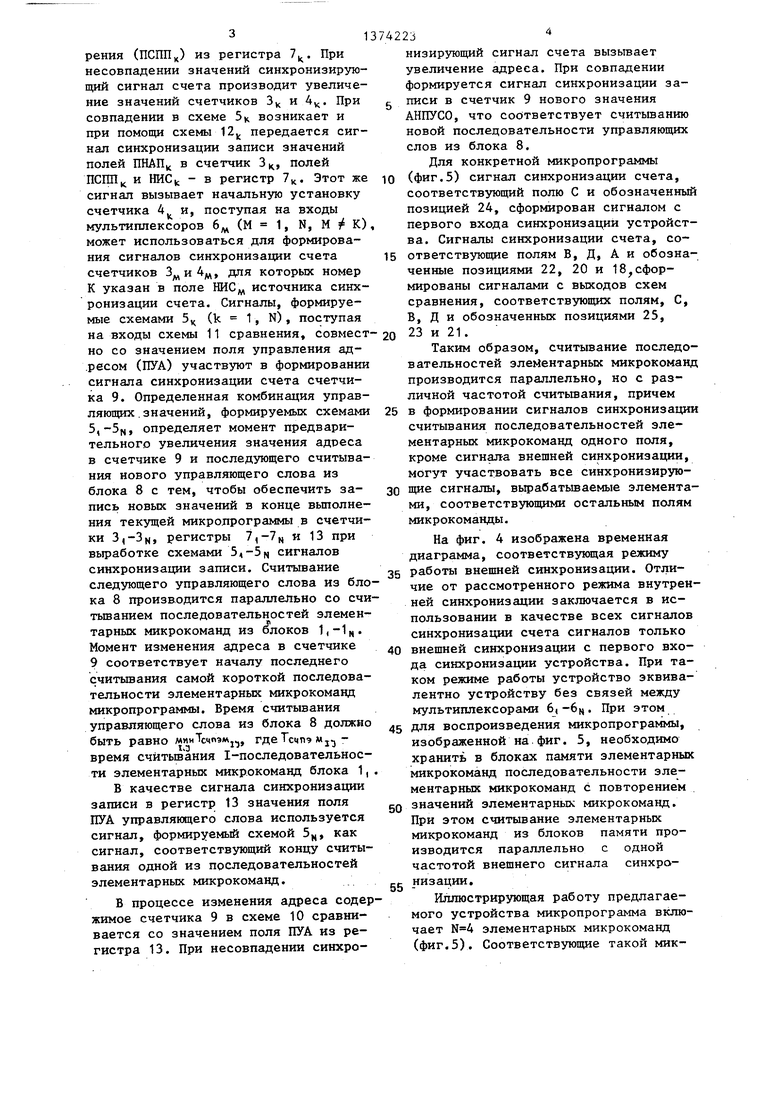

Режим начальной установки изображен на фиг. 2. Позицией 14 обозначены синхронизирующие сигналы на втором входе устройства, позицией 15 - сигнал начальной установки первого входа синхронизации устройства. Позициями 16 и 17 обозначены соответст веннв адресная информация на первом и втором входах кода команды устройства, а позициями 18-25 - сигналы синхронизации счета и записи (начальной установки) на входах счетчиков 3,-3q., 4,-44 для полей А, Д, В, С микропрограммы (фиг.5). Позиции 26 и 27 обозначают соответственно сигналы синхронизации счета и записи счетчика 9.

В режиме начальной установки на первый и второй входы кода команды подаются соответственно значения начального и конечного адреса nocjre- довательности управляющих слов (АНПУСО и АКПУСО) блока 8 памяти управления. Первое из значений запи- сьюается в счетчик 9;сигналом началь ной установки с первого входа устройства, поступающим через схему 2

0

0

0

5

0

5

5

на вход синхронизации записи счетчика 9. Соответствующее адресу АНПУСО управляющее слово считывается из блока 8. Значения полей этого управляющего слова записываются в счетчики 3,-3|,(, регистры 7,-7fj сигналом с первого входа синхронизации устройства, поступающим через схемы 12,-12 на входы синхронизации записи.счетчиков 3,-Зц и регистров 7,-7ц и 13. Этим же сигналом осуществляется начальная установка счетчиков 4,-4ц. Таким образом, счетчики р,-3у содержат начальные адреса последовательностей элементарных микрокоманд (ПНАП,, ..., ПНАПу). Соответствующие этим адресам элементарные микрокоманды считываются из блоков 1,-1i. Время удержания сигнала начальной установки должно быть больше или равно интервалу времени от записи значения АНПУСО до появления элементарных микрокоманд, соответствующих ад5 ресам ПНАП4,..., ПНАП на выходе устройства. Эти значения постоянны до снятия сигнала начальной установки. Снятие сигнала начальной установ- . ки обеспечивает переход либо к режи0 му- внутренней, либо внешней синхронизации, в зависимости от содержания считываемых управляюш пс слов блока 8 памяти управления.

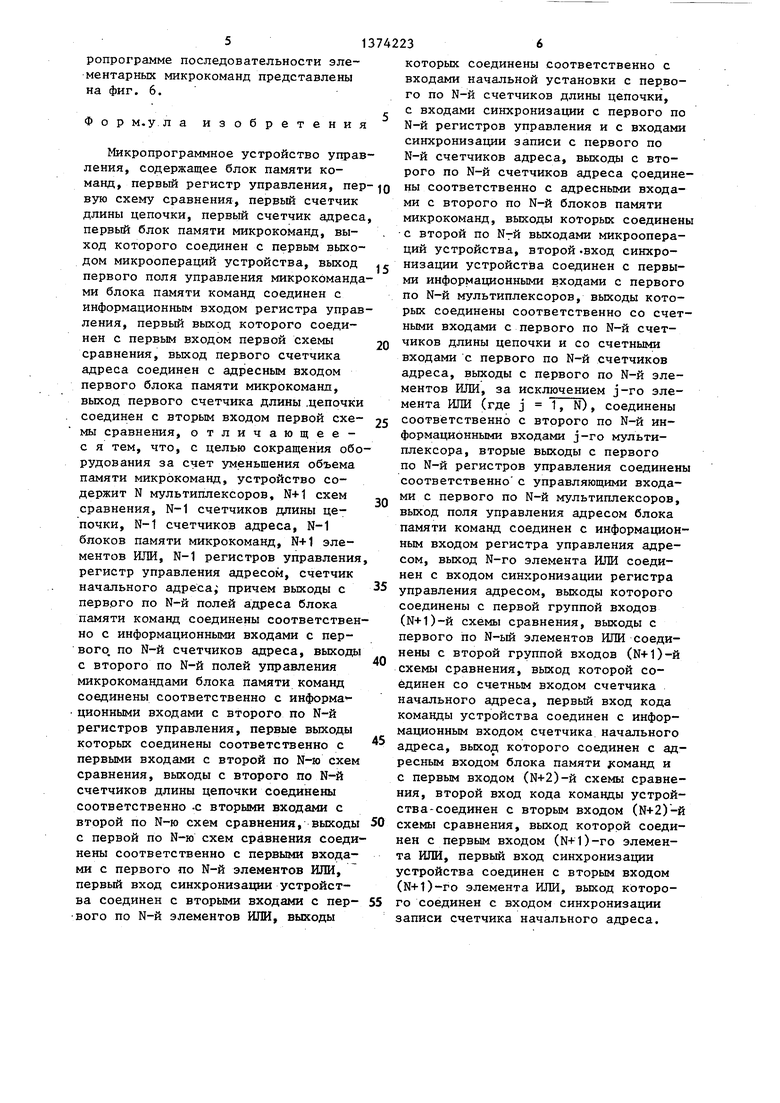

На фиг. 3 приведена временная диаграмма, соответствующая режиму внутренней синхронизации (обозначения соответствуют обозначениям на

фиг. 2). I

Начало режима- соответствует снятию сигнала начальной установки с первого входа синхронизации устройства. При этом сигнал внешней синхронизации с второго входа синхронизации устройства поступает на счетный вход и вызывает увеличение значений в тех счетчиках 3 и 4 (К 1, N), для которых значения полей номера источника синхронизации (НИСц ) в регистрах 7 указьюают в качестве источника синхронизации второй вход синхронизации устройства. Это обеспечивается подачей зна чений поля НИС на управляюш 1е входы мультиплексора 6. Соответствующие этим адресам элементарные микрокоманды считываются из блоков 1, памяти. Каждое текущее значение счетчика 4 сравнивается в схеме 5 ) со значением поля сомножителей периода повто-г31

рения (ПСГШ) из регистра 7. При несовпадении значений синхронизирующий сигнал счета производит увеличение значений счетчиков 3( и 4. При совпадении в схеме 5к возникает и при помощи схемы 12 передается сигнал синхронизации записи значений полей ПНАП в счетчик 3 ц, полей ПСПП и НИС - в регистр 7. Этот же сигнал вызывает начальную установку счетчика 4 и, поступая на входы мультиплексоров 6 (М 1, N, М 5 К) может использоваться для формирования сигналов синхронизации счета счетчиков (ц, для которых номер К указан в поле НИС источника синхронизации счета. Сигналы, формируемые схемами 5ц (k 1, N), поступая на входы схемы 11 сравнения, совместно со значением поля управления ад- .ресом (ПУЛ) участвуют в формировании сигнала синхронизации счета счетчика 9. Определенная комбинация управляющих .значений, формируемых схемами 5,-5ц, определяет момент предварительного увеличения значения адреса в счетчике 9 и последующего считывания нового управляющего слова из блока 8 с тем, чтобы обеспечить запись новых значений в конце вьшолне- ния текущей микропрограммы в счетчики 3,-3«, регистры 7,-7 и 13 при выработке схемами 5,-5|ц сигналов синхронизации записи. Считывание следующего управляющего слова из блока 8 производится параллельно со счи тьшанием последовательностей элементарных микрокоманд из блоков 1,-1. Момент изменения адреса в счетчике 9 соответствует началу последнего считывания самой короткой последовательности элементарных микрокоманд микропрограммы. Время считывания управляющего слова из блока 8 должно быть равно ААинТсчпэм, гдеТсчпэ Mj.,- время счйтьшания 1-последовательнос- ти элементарных микрокоманд блока 1,

В качестве сигнала синхронизации записи в регистр 13 значения поля ПУА управляющего слова используется сигнал, формируемый схемой 5,,, как сигнал, соответствующий концу считывания одной из последовательностей элементарных микрокоманд.

В процессе изменения адреса содержимое счетчика 9 в схеме 10 сравнивается со значением поля ПУА из регистра 13. При несовпадении синхро23

низирующий сигнал счета вызьгеает увеличение адреса. При совпадении формируется сигнал синхронизации записи в счетчик 9 нового значения АНПУСО, что соответствует считыванию новой последовательности управляю1дих слов из блока 8.

Для конкретной микропрограммы

(фиг.5) сигнал синхронизации счета, соответствующий полю С и обозначенный позицией 24, сформирован сигналом с первого входа синхронизации устройства. Сигналы синхронизации счета, соответствующие полям В, Д, А и обозначенные позициями 22, 20 и 18,сформированы сигналами с выходов схем сравнения, соответствующих полям. С, В, Д и обозначенных позициями 25,

23 и 21.

Таким образом, считывание последовательностей элементарных микрокоманд производится параллельно, но с различной частотой считывания, причем

в формировании сигналов синхронизации считывания последовательностей элементарных микрокоманд одного поля, кроме сигнала внешней синхронизации, могут участвовать все синхронизирующие сигналы, вырабатываемые элементами, соответствующими остальным полям микрокоманды.

На фиг. 4 изображена временная диаграмма, соответствующая режиму

работы внешней синхронизации. Отличие от рассмотренного режима внутренней синхронизации заключается в использовании в качестве всех сигналов синхронизации счета сигналов только

внешней синхронизации с первого входа синхронизации устройства. При таком режиме работы устройство эквивалентно устройству без связей между мультиплексорами 6,-6ц. При этом

для воспроизведения микропрограммы, изображенной на фиг. 5, необходимо хранить в блоках памяти элементарных микрокоманд последовательности элементарных микрокоманд с повторением значений элементарных микрокоманд. При этом считывание элементарных микрокоманд из блоков памяти производится параллельно с одной частотой внешнего сигнала синхронизации.

Иллюстрирующая работу предлагаемого устройства микропрограмма включает элементарных микрокоманд (фиг.5). Соответствующие такой мик

-

ропрограмме последовательности элементарных микрокоманд представлены на фиг. 6.

Фор м.у л а изобретения

Микропрограммное устройство управления, содержащее блок памяти кокоторых соединены соответственно с входами начальной установки с первого по N-й счетчиков длины цепочки, с входами синхронизации с первого по N-й регистров управления и с входами синхронизации записи с первого по N-й счетчиков адреса, выходы с второго по N-й счетчиков адреса соедине

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультимикропрограммная система управления | 1985 |

|

SU1291981A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Мультимикропрограммное устройство управления с контролем | 1985 |

|

SU1272333A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130865A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1997 |

|

RU2111528C1 |

| МОДУЛЬ МУЛЬТИМИКРОПРОГРАММНОЙ СИСТЕМЫ | 1997 |

|

RU2116665C1 |

| Мультимикропрограммное устройство управления | 1985 |

|

SU1282121A1 |

| Микропрограммное устройство управления с контролем | 1986 |

|

SU1305679A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1381506A1 |

Изобретение относится к вычисли- .тельной технике, в частности к микропрограммным устройствам управления, и может быть использовано для построения программируемых устройств управления. Цель изобретения - сокращение объема оборудования за счет уменьшения объема памяти микрокоманд. Устройство содержит блоки памяти микрО команд, счетчики адреса, счетчики длины цепочки, схемы сравнения, мультиплексоры, регистры,управления, блок памяти команд, счетчик начального адреса, две схемы сравнения, элементы ИЛИ, регистр управления адресом. Указанная цель достигается с помощью указанной совокупности признаков. 6 ил.

манд, первый регистр управления, ны соответственно с адресными входа- вую схему сравнения, первый счетчик длины цепочки, первый счетчик адреса, первый блок памяти микрокоманд, выход которого соединен с первым выходом микроопераций устройства, выход |г первого поля управления микрокомандами блока памяти команд соединен с информационным входом регистра управми с второго по N-й блоков памяти микрокоманд, выходы которых соединены с второй по Nrй выходами микроопераций устройства, второй -вход синхронизации устройст1ва соединен с первыми информационньп и входами с первого по N-й мультиплексоров, выходы которых соединены соответственно со счетными входами с первого по N-й счетления, первый выход которого соединен с первым входом первой схемы сравнения, выход первого счетчика адреса соединен с адресным входом первого блока памяти микрокоманд, выход первого счетчика длины .цепочки соединен с вторым входом первой схемы сравнения, отличающее- с я тем, что, с целью сокращения оборудования за счет уменьшения объема памяти микрокоманд, устройство содержит N мультиплексоров, N+1 схем сравнения, N-1 счетчиков длины цепочки, N-1 счетчиков адреса, N-1 блоков памяти микрокоманд, N+1 элементов ИЛИ, N-1 регистров управления регистр управления адресом, счетчик начального адреса; причем выходы с первого по N-й полей адреса блока памяти команд соединены соответственно с информационными входами с первого, по N-й счетчиков адреса, выходы с второго по N-й полей управления микрокомандами блока памяти команд соединены соответственно с информа - ционными входами с второго по N-й регистров управления, первые выходы которых соединены соответственно с первыми входами с второй по N-ю схем сравнения, выходы с второго по N-й счетчиков длины цепочки соединены соответственно -с вторыми входами с второй по N-ю схем сравнения, выходы с первой по N-ю схем сравнения соединены соответственно с первыми входами с первого по N-й элементов ИЛИ, первый вход синхронизации устройства соединен с вторыми входами с первого по N-й элементов ИЛИ, выходы

ны соответственно с адресными входа-

ми с второго по N-й блоков памяти микрокоманд, выходы которых соединены с второй по Nrй выходами микроопераций устройства, второй -вход синхронизации устройст1ва соединен с первыми информационньп и входами с первого по N-й мультиплексоров, выходы которых соединены соответственно со счетными входами с первого по N-й счетчиков длины цепочки и со счетными входами с первого по N-й счетчиков адреса, выходы с первого по N-й элементов ИЛИ, за исключением j-ro элемента ИЛИ (где j 1, N), соединены

соответственно с второго по N-й информационными входами j-ro мультиплексора, вторые выходы с первого по N-й регистров управления соединены соответственно с управляющими входами с первого по N-й мультиплексоров, выход поля управления адресом блока памяти команд соединен с информационным входом регистра управления адресом, выход N-ro элемента ИЛИ соединен с входом синхронизации регистра управления адресом, выходы которого соединены с первой группой входов (N+1)-й схемы сравнения, выходы с первого по N-ый элементов ИЛИ соединены с второй группой входов (N+1)-й схемы сравнения, выход которой соединен со счетным входом счетчика начального адреса, первый вход кода команды устройства соединен с информационным входом счетчика начального адреса, выход которого соединен с адресным входом блока памяти coмaнд и с первым входом (N+2)-й схемы сравнения, второй вход кода команды устрой- ства-соединен с вторым входом (N+2)-й

схемы сравнения, выход которой соединен с первым входом (N+1)-ro элемента ИЛИ, первый вход синхронизации устройства соединен с вторым входом (N+1)-ro элемента ИЛИ, выход которого соединен с входом синхронизации записи счетчика начального адреса.

CverHbfu6xod

Входсинхронизащп/

Зйписи

У АШаг

Х

fa

19 20 21 22 23

25 26 21

.Выходы минроопераци фиг. 1

uti

14 JlJ...riJn... .,,.

JXTL ...Jnjn...,. jnJT.

J I L-

26П

27

j /V -HJnj... jnjlLJn-.... jnjlJl

/y . . .

/4Я/7У(7Д

АКПУСО

«r Jljrn,. J1J1J1«... J lJn-rU П

-JOJOJO.... J1J1J, ..JlJlJ -

TL.

ife/г.

А, Л, а, c. А, Д, fl, с,,

о

1 Дт в2

AI fli 2 С

о

t Д) бк2 1

А| At 8к2 Kf А/ Дг BI t

0

AI Дг fit CM

AI Д2 82 C

AI Д2 2 C

AI Да вк2 C|.

AZ AZ K2 Kl

Vf Ai 61 c,

AI Дкз K2 1

z 02

w Ctff

Az 82 с

AI Дкз V

Фиг.5

Фие.6

Фие.6

| Устройство микропрограммного управления | 1980 |

|

SU942020A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления | 1977 |

|

SU732871A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-02-15—Публикация

1986-08-12—Подача