со

со

11

Изобретение относится к вычислительной технике и может быть использовано при создании в интегральном исполнении оперативных запоминающих устройств со встроенной коррекцией ошибок методом мажоритарного декодирования.

Целью изобретения является повьшге ние быстродействия и упрощение уст- ройства.

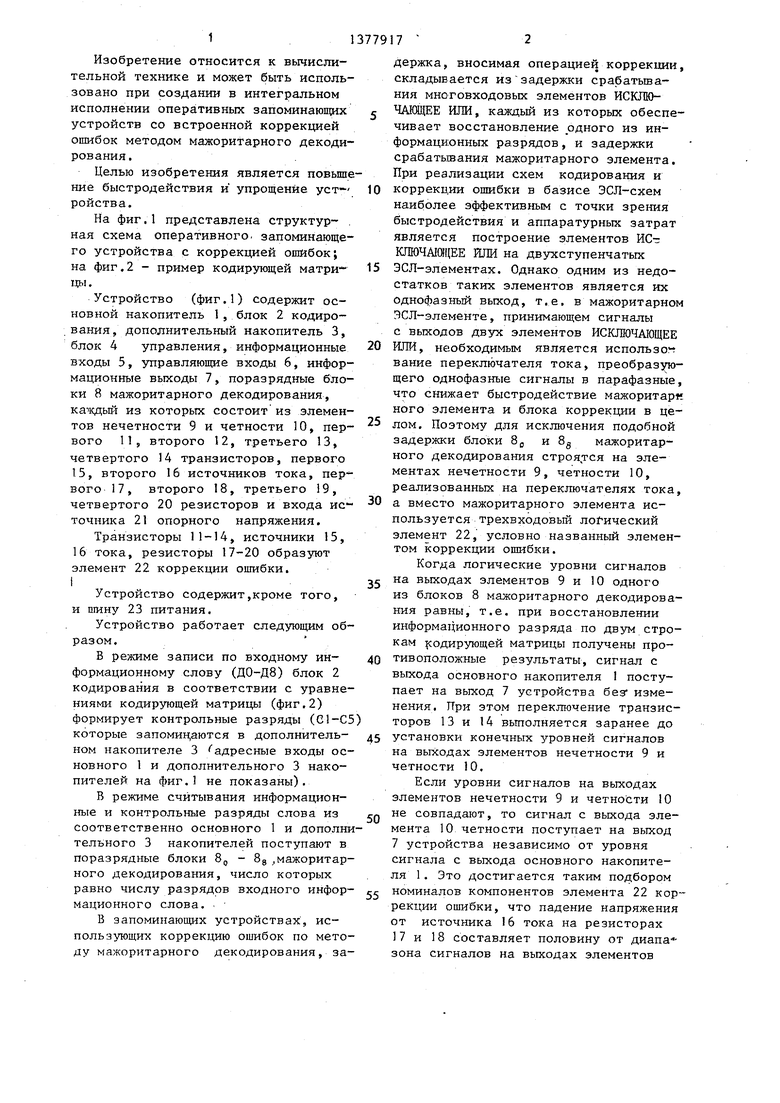

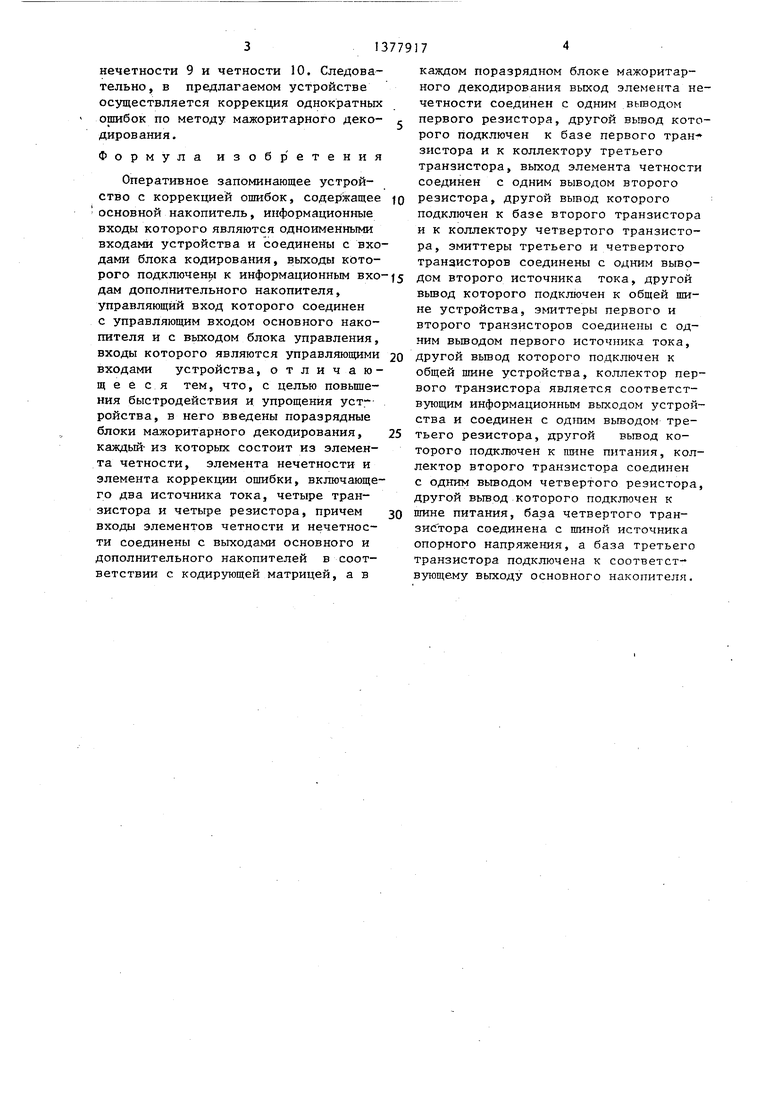

На фиг.1 представлена структур- . ная схема оперативного, запоминающего устройства с коррекцией ошибок; на фиг.2 - пример кодирующей матри - цы.

Устройство (фиг.1) содержит основной накопитель 1, блок 2 кодирования , дополнительный накопитель 3, блок 4 управления, информационные входы 5, управляющие входы 6, информационные выходы 7, поразрядные блоки 8 мажоритарного декодирования, из которых состоит из элементов нечетности 9 и четности 10, первого 11, второго 12, третьего 13, четвертого 14 транзисторов, первого 1.5, второго 16 источников тока, пер- вого 17, второго 18, третьего 19, четвертого 20 резисторов и входа ис- точника 21 опорного напряжения.

Транзисторы 11-14, источники 15, 16 тока, резисторы 17-20 образзпот элемент 22 коррекции ошибки.

I

Устройство содержит,кроме того,

и шину 23 питания.

Устройство работает следующим образом.

В режиме записи по входному ин- формационному слову (ДО-ДВ) блок 2 кодирования в соответствии с уравнениями кодирующей матрицы (фиг.2) формирует контрольные разряды (С1-С5 которые запомин,аются в дополнитель- ном накопителе 3 адресные входы основного 1 и дополнительного 3 накопителей на фиг.1 не показаны).

В режиме считывания информационные и контрольные разряды слова из соответственно основного 1 и дополнительного 3 накопителей поступают в поразрядные блоки 8, - 8g мажоритарного декодирования, число которых равно числу разрядов входного инфор- мационного слова. .

В запоминающих устройствах, использующих коррекцию ошибок по методу мажоритарного декодирования, за17 2

держка, вносимая операцией коррекции складывается из задержки срабатьюа- ния многовходовых элементов ИСКЛЮ- ЧАЩЕЕ ИЛИ, каждый из которых обеспечивает восстановление одного из информационных разрядов, и задержки срабатьшания мажоритарного элемента. При реализации схем кодирования и коррекции ошибки в базисе ЭСЛ-схем наиболее эффективным с точки зрения быстродействия и аппаратурных затрат является построение элементов ИСт КЛЮЧАРЦЕЕ ИЛИ на двухступенчатых ЭСЛ-элементах. Однако одним из недостатков таких элементов является их однофазный выход, т.е. в мажоритарном ЭСЛ-элементе, принимающем сигналы с выходов двух элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, необходимым является использо вание переключателя тока, преобразующего однофазные сигналы в парафазные что снижает быстродействие мажоритарк ного элемента и блока коррекции в целом. Поэтому для исключения подобной задержки блоки 8g и 8g мажоритарного декодирования строятся на элементах нечетности 9, четности 10, реализованных на переключателях тока а вместо мажоритарного элемента используется трехвходовый логический элемент 22, условно названный элементом коррекции ошибки.

Когда логические уровни сигналов на выходах элементов 9 и 10 одного из блоков 8 мажоритарного декодирования равны, т.е. при восстановлении информационного разряда по двум строкам кодирующей матрицы получены противоположные результаты, сигнал с выхода основного накопителя 1 поступает на выход 7 устройства без изменения. При этом переключение транзисторов 13 и 14 вьтолняется заранее до установки конечных уровней сигналов на выходах элементов нечетности 9 и четности 10.

Если уровни сигналов на выходах элементов нечетности 9 и четности 10 не совпадают, то сигнал с выхода элемента 10 четности поступает на выход 7 устройства независимо от уровня сигнала с выхода основного накопителя 1. Это достигается таким подбором номиналов компонентов элемента 22 коррекции ошибки, что падение напряжения от источника 16 тока на резисторах 17 и 18 составляет половину от диапа зона сигналов на выходах элементов

нечетности 9 и четности 10. Следовательно, в предлагаемом устройстве осуществляется коррекция однократных ошибок по методу мажоритарного деко- дирования.

Формула изобр етения

Оперативное запоминающее устройство с коррекцией ошибок, содержащее основной накопитель, информационные входы которого являются одноименными входами устройства и соединены с входами блока кодирования, выходы которого подключены к информационным вхо дам дополнительного накопителя, управляющий вход которого соединен с управляющим входом основного накопителя и с выходом блока управления, входы которого являются управляющими входами устройства, отличающееся тем, что, с целью повьше- ния быстродействия и упрощения устройства, в него введены поразрядные блоки мажоритарного декодирования, каждый- из которых состоит из элемента четности, элемента нечетности и элемента коррекции ошибки, включающего два источника тока, четыре транзистора и четыре резистора, причем входы элементов четности и нечетности соединены с выходами основного и дополнительного накопителей в соответствии с кодирующей матрицей, а в

каждом поразрядном блоке мажоритарного декодирования выход элемента нечетности соединен с одним вьшодом первого резистора, другой вывод которого подключен к базе первого тран зистора и к коллектору третьего транзистора, выход элемента четности соединен с одним выводом второго резистора, другой вывод которого подключен к базе второго транзистора и к коллектору четвертого транзистора, эмиттеры третьего и четвертого транзисторов соединены с одним выводом второго источника тока, другой вьшод которого подключен к общей шине устройства, эмиттеры первого и второго транзисторов соединены с одним вьшодом первого источника тока, другой вьшод которого подключен к общей шине устройства, коллектор первого транзистора является соответствующим информационным выходом устройства и соединен с вьгоодом третьего резистора, другой вывод которого подключен к шине питания, коллектор второго транзистора соединен с одним вьгаодом четвертого резистора, другой вьшод которого подключен к шине питания, база четвертого транзистора соединена с шиной источника опорного напряжения, а база третьего транзистора подключена к соответствующему выходу основного накопителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство с коррекцией ошибок по методу мажоритарного декодирования | 1986 |

|

SU1410105A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1368923A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1251188A1 |

| Запоминающее устройство с самоконтролем | 1987 |

|

SU1501171A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1987 |

|

SU1481863A1 |

| Запоминающее устройство с коррекцией ошибок | 1985 |

|

SU1290419A1 |

| Мажоритарный элемент | 1986 |

|

SU1378049A1 |

| Модульное запоминающее устройство с коррекцией ошибок | 1985 |

|

SU1320848A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1167659A1 |

| Запоминающее устройство с обнаружением и исправлением ошибок | 1980 |

|

SU898509A1 |

Изобретение относится к вычислительной технике и может быть использовано при создании в интегральном исполнении оперативнъ1х -запоминающих устройств со встроенной Sy55.j;-at: .;.. 4,v- коррекцией ошибок методом мажоритарного декодирования. Целью изобрете- ния является повышение быстродействия и упрощение устройства. Устройство содержит основной и дополнительный накопители, блок кодирования, блок управления и поразрядные блоки мажоритарного декодирования, каждый из которых состоит из элемента чет- ности .элемента нечетности и элемента коррекции ошибки, включающего четыре транзистора, два источника тока и четыре резистора. В устройстве устранена задержка.преобразования однофазного сигнала в п рафазный на входе мажоритарного элемента путем построения поразрядных блоков декодирования на элементах четности, нечетности и коррекции ошибки. 2 ил. с О)

Фиг. f

| Электроника,1983, № 18, с | |||

| Устройство для охлаждения водою паров жидкостей, кипящих выше воды, в применении к разделению смесей жидкостей при перегонке с дефлегматором | 1915 |

|

SU59A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Запоминающее устройство с коррекцией однократных ошибок | 1982 |

|

SU1073799A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-02-28—Публикация

1986-09-22—Подача