со

00

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ РЕГИСТРАТОР ПЕРЕХОДНЫХ ПРОЦЕССОВ | 1990 |

|

RU2029310C1 |

| Устройство для регистрации информации | 1989 |

|

SU1698895A1 |

| Устройство для регистрации информации | 1985 |

|

SU1304170A1 |

| Многоканальное устройство для регистрации аналоговых и цифровых сигналов | 1988 |

|

SU1564649A1 |

| УСТРОЙСТВО ДЛЯ СИНТЕЗА РЕЧЕВЫХ СИГНАЛОВ | 1991 |

|

RU2020608C1 |

| Устройство для отображения однократных электрических сигналов | 1983 |

|

SU1141445A1 |

| Передающее устройство адаптивной телеизмерительной системы | 1989 |

|

SU1679517A1 |

| Устройство для анализа формы непериодических импульсных и частотных сигналов | 1982 |

|

SU1075196A1 |

| Устройство сбора данных для цифрового анализатора сигналов | 1990 |

|

SU1751683A1 |

| Цифровой регистратор | 1984 |

|

SU1164549A1 |

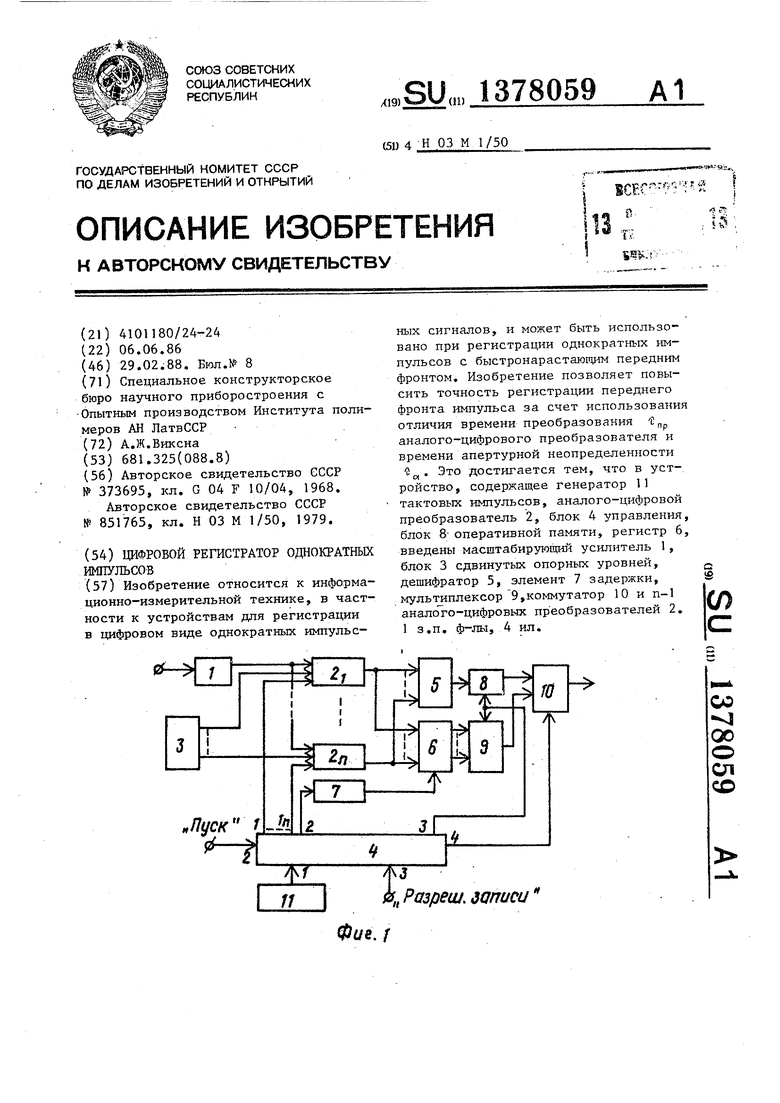

Изобретение относится к информационно-измерительной технике, в частности к устройствам для регистрации в цифровом виде однократных импульсных сигналов, и может быть использовано при регистрации однократных импульсов с быстронарастающим передним фронтом. Изобретение позволяет повысить точность регистрации переднего фронта импульса за счет использования отличия времени преобразования аналого-цифрового преобразователя и времени апертурной неопределенности Од. Это достигается тем, что в устройство, содержащее генератор 11 тактовых импульсов, аналого-цифровой преобразователь 2, блок 4 управления, блок 8- оперативной памяти, регистр 6, введены масштабирлпощий усилитель 1, блок 3 сдвинутых опорных уровней, дешифратор 5, элемент 7 задержки, мультиплексор 9,коммутатор 10 и п-1 аналого-цифровых преобразователей 2. 1 з.п. ф-лы, 4 ил. « (О

п

Фуе. /

ел со

AJ

4 Разреш. 3Gm/cu

Изобретение относится к информационно-измерительной технике, в частности к устройствам для регистрации в цифровом виде однократнь1Х импульсных сигналов, может найти применение при исследованиях в машиностроении, сейсморазведке, химии, радиотехнике и физике.

Целью изобретения является повышение точности регистрации переднего фронта импульса.

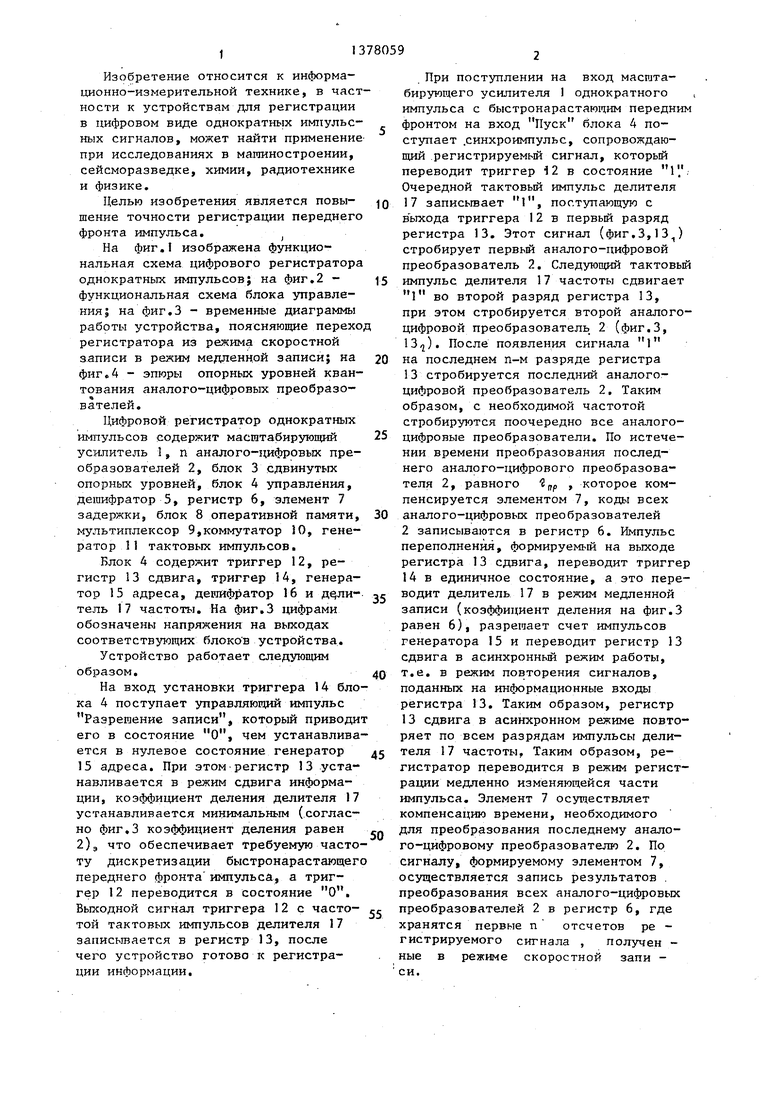

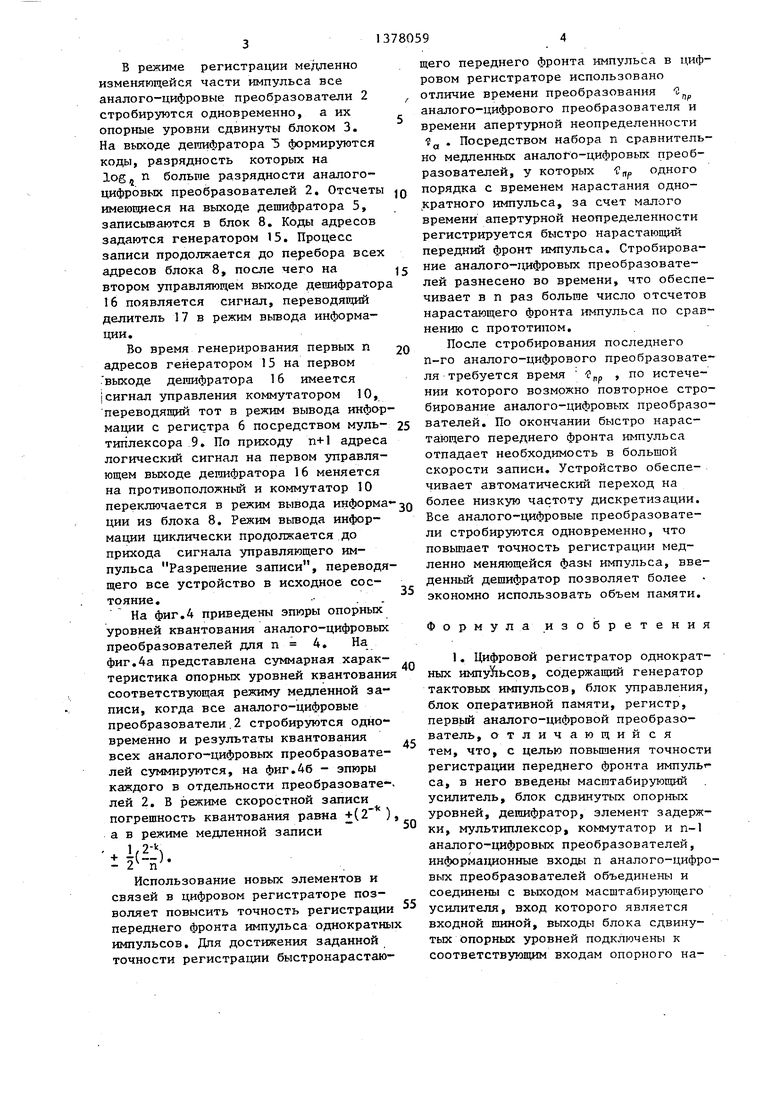

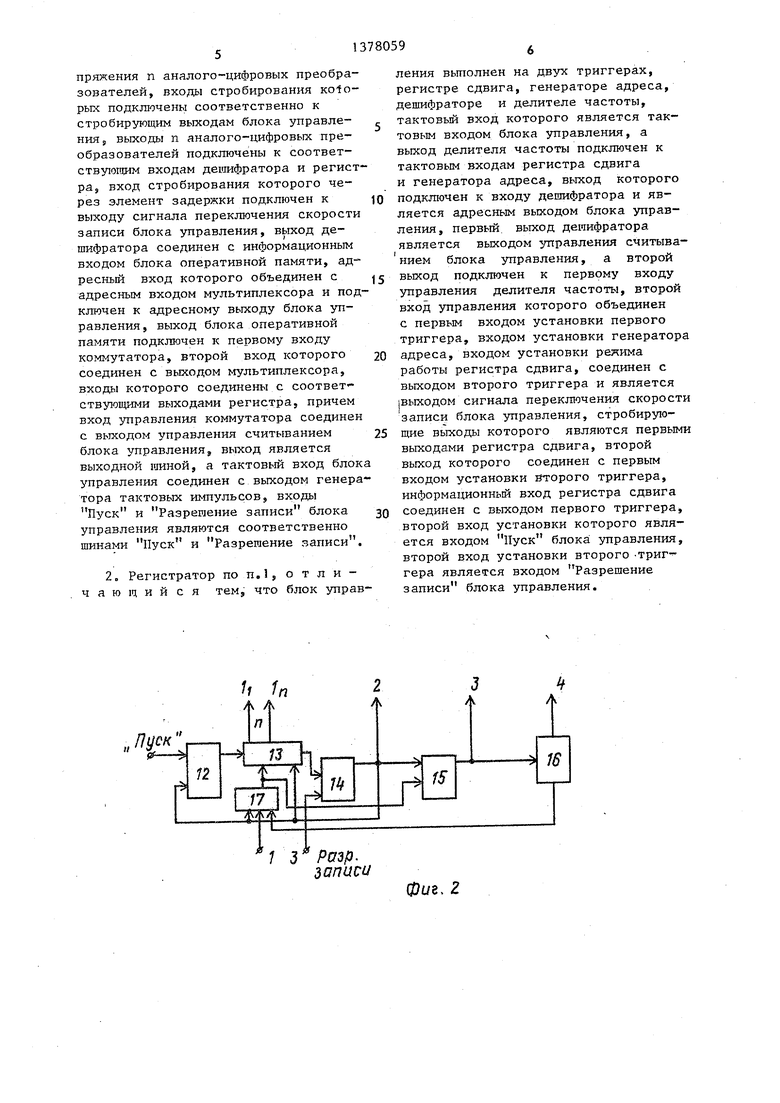

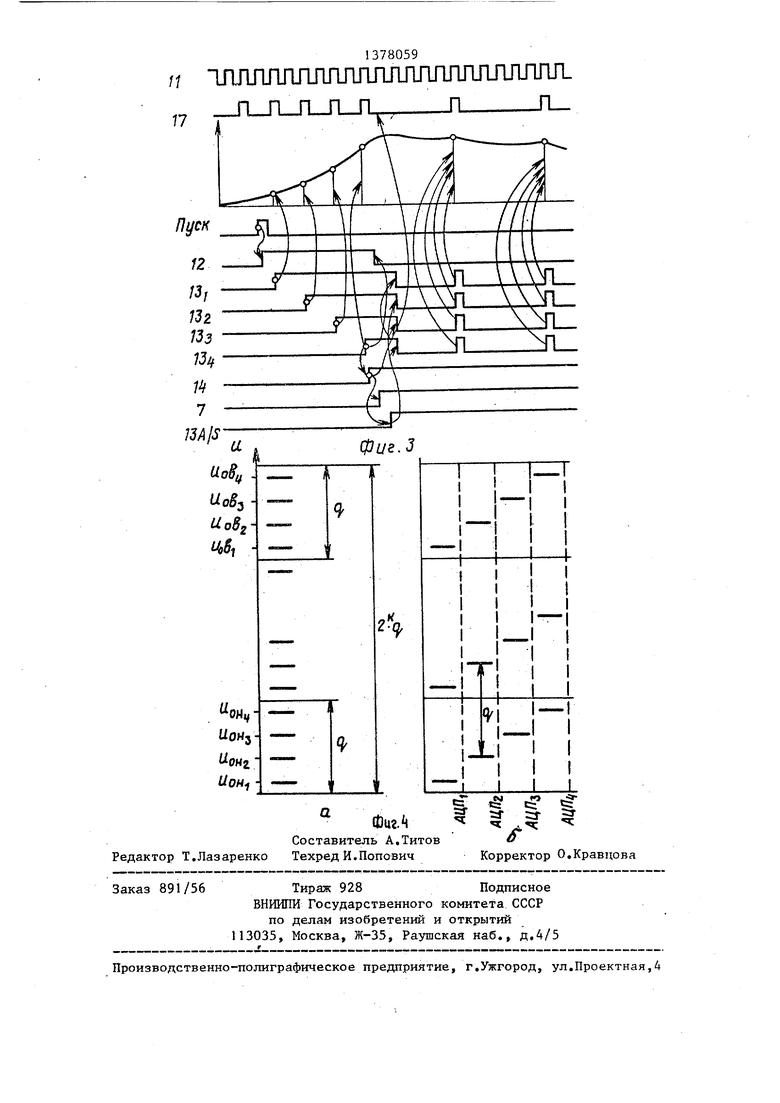

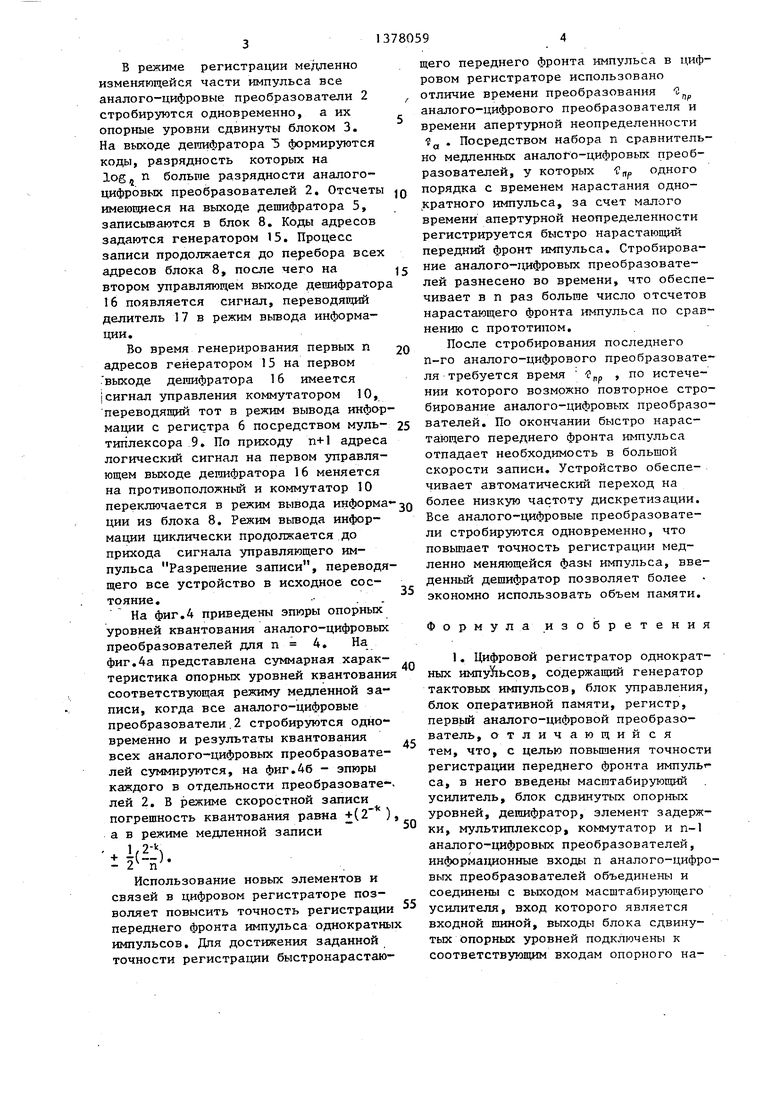

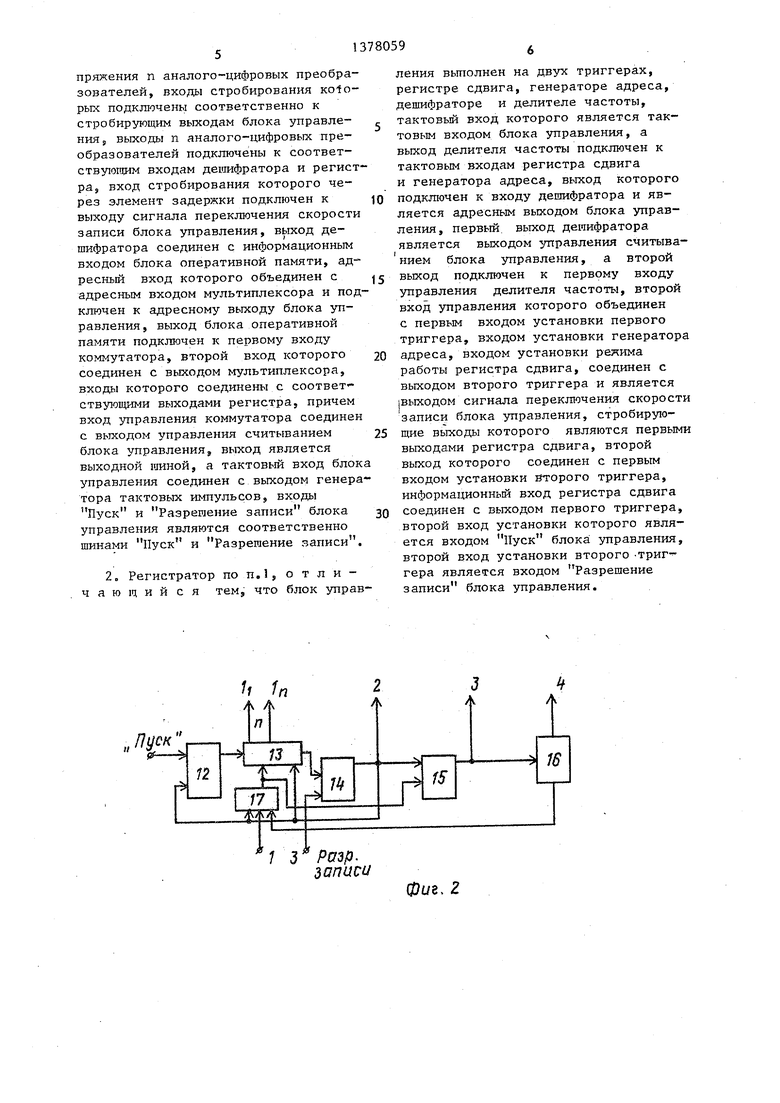

На фиг.1 изображена функциональная схема цифрового регистратора однократных импульсов; на фиг.2 - функциональная схема блока управления; на фиг.3 - временные диаграммы работы устройства, поясняющие перехо регистратора из режима скоростной записи в режим медленной записи; на фиг,4 - эпюры опорных уровней квантования аналого-цифровых преобразователей.

Цифровой регистратор однократных импульсов содержит масштабирующий усилитель 1, п аналого-цифровых преобразователей 2, блок 3 сдвинутых опорных уровней, блок 4 управления, дешифратор 5, регистр 6, элемент 7 задержки, блок 8 оперативной памяти, мультиплексор 9,коммутатор 10, генератор 1 1 тактовых импульсов.

Блок 4 содержит триггер 12, регистр 13 сдвига, триггер 14, генератор 15 адреса, деиифратор 16 и тель 17 частоты. На фиг.З цифрами обозначены напряжения на выходах соответствующих блоко в устройства.

Устройство работает следующим образом.

На вход установки триггера 14 блока 4 поступает управляющий импульс PaapepjeHHe записи, который приводи его в состояние О, чем устанавливается в нулевое состояние генератор 15 адреса. При этом регистр 13 устанавливается в режим сдвига информации, коэффициент деления делителя 17 устанавливается минимальным (согласно фиг.З коэффициент деления равен 2),, что обеспечивает требуемую частоту дискретизации быстронарастающег переднего фронта импульса, а триггер 12 переводится в состояние О. Вькодной сигнал триггера I2 с частотой тактовых импульсов делителя 17 эаписьгоается в регистр 13, после чего устройство готово к ре,гистра- ции информации.

10

15

20

5

0

5

0

0

5

При поступлении на вход масглта- бирующего усилителя 1 однократного i импульса с быстронарастающим передним фронтом на вход Пуск блока 4 поступает .синхроимпульс, сопровождающий регистрируемый сигнал, который переводит триггер 12 в состояние .. Очередной тактовьм импульс делителя 17 записьгоает 1, поступающую с в ыхода триггера 12 в первый разряд регистра 13. Этот сигнал (фиг.3,13) стробирует первьй аналого-цифровой преобразователь 2. Следующий тактовый импульс делителя 17 частоты сдвигает 1 во второй разряд регистра 13, при этом стробируется второй аналого- цифровой преобразователь. 2 (фиг.З, 13). После появления сигнала 1 на последнем п-м разряде регистра

13стробируется последний аналого- цифровой преобразователь 2. Таким образом, с необходимой частотой стробируются поочередно все аналого- цифровые преобразователи. По истечении времени преобразования последнего аналого-цифрового преобразователя 2, равного , которое компенсируется элементом 7, коды всех аналого-цифровых преобразователей

2 записываются в регистр 6. Импульс переполнения, формируе Ф.1й на выходе регистра 13 сдвига, переводит триггер

14в единичное состояние, а это переводит делитель 17 в режим медленной записи (коэффициент деления на фиг.З равен 6), разрешает счет импульсов генератора 15 и переводит регистр 13 сдвига в асинхронньй режим работы, т.е. в режим повторения сигналов, поданных на информационные входы регистра 13. Таким образом, регистр 13 сдвига в асинхронном режиме повторяет по всем разрядам импульсы делителя 17 частоты. Таким образом, регистратор переводится в режим регистрации медленно изменяющейся части импульса. Элемент 7 осуществляет компенсацию времени, необходимого для преобразования последнему аналого-цифровому преобразователю 2. По сигналу, формируемому элементом 7, осуществляется запись результатов . преобразования всех аналого-цифровых преобразователей 2 в регистр 6, где хранятся первые п отсчетов ре - гистрируемого сигнала , получен - ные в режиме скоростной запи - си.

В режиме регистрации медленно изменяющейся части импульса все аналого-цифровые преобразователи 2 стробируются одновременно, а их опорные уровни сдвинуты блоком 3. На выходе дешифратора 5 формируются коды, разрядность которых на logjj п больме разрядности аналого- цифровых преобразователей 2, Отсчеты имеющиеся на выходе дешифратора 5, записьгоаются в блок 8, Коды адресов задаются генератором 15. Процесс записи продолжается до перебора всех адресов блока 8, после чего на втором управляющем выходе дешифратор 16 появляется сигнал, переводящий делитель 17 в режим вывода информации,

Во время генерирования первых п адресов генератором 15 на первом . выходе дешифратора 16 имеется I сигнал управления коммутатором 10, переводящий тот в режим вывода информации с регистра 6 посредством муль- типлексора 9, По приходу n+l адреса логический сигнал на первом управляющем выходе дешифратора 16 меняется на противоположньй и коммутатор 10 переключается в режим вывода информа ции из блока 8. Режим вьгоода информации циклически продолжается до прихода сигнала управляющего импульса Разрешение записи, переводящего все устройство в исходное состояние,.- , .

На фиг,4 приведены эпюры опорных уровней квантования аналого-цифровых преобразователей для п 4, На фиг,4а представлена суммарная характеристика опорных уровней квантовани соответствующая режиму медленной записи, когда все аналого-цифровые преобразователи.2 стробируются одновременно и результаты квантования всех аналого-цифровых преобразователей суммируются, на фиг,46 - эпюры каждого в отдельности преобразователей 2, В режиме скоростной записи

погрешность квантования равиа +(2 ) а в режиме медленной записи

k ) - 2

Использование новых элементов и связей в цифровом регистраторе позволяет повысить точность регистрации переднего фронта импу;пьса однократны импульсов. Для достижения заданной точности регистрации быстронарастаю-

5

0 5 о

0

0

5

щего переднего фронта импульса в цифровом регистраторе использовано отличие времени преобразования 3 аналого-цифрового преобразователя и времени апертзфной неопределенности Ид . Посредством набора п сравнительно медленных аналого-цифровых преобразователей, у которых Рпр одного порядка с временем нарастания однократного импульса, за счет малого времени апертурной неопределенности регистрируется быстро нарастающий передний фронт импульса, Стробирова- ние аналого-цифровых преобразователей разнесено во времени, что обеспечивает в п раз больше число отсчетов нарастающего фронта импульса по сравнению с прототипом.

После стробирования последнего п-го аналого-цифрового преобразователя требуется время ,р , по истечении которого возможно повторное стро- бирование аналого-цифровых преобразователей. По окончании быстро нарастающего переднего фронта импульса отпадает необходимость в большой скорости записи. Устройство обеспечивает автоматический переход на более низкую частоту дискретизации. Все аналого-цифровые преобразователи стробируются одновременно, что повышает точность регистрации медленно меняющейся фазы импульса, введенный дешифратор позволяет более экономно использовать объем памяти.

Формула изобретения

1, Цифровой регистратор однократных импуЬьсов, содержащий генератор тактовых импульсов, блок управления, блок оперативной памяти, регистр, первьй аналого-цифровой преобразователь, отличающийся тем, что, с целью повышения точности регистрации переднего фронта импуль - са, в него введены масштабирующий усилитель, блок сдвинутых опорных уровней, дешифратор, элемент задержки, мультиплексор, коммутатор и п-1 аналого-цифровых преобразователей, информационные входы п аналого-цифровых преобразователей объединены и соединены с выходом масштабирующего усилителя, вход которого является входной шиной, выходы блока сдвинутых Опорных уровней подключены к соответствующим входам опорного напряжения n аналого-цифровых преобразователей, входы стробирования которых подключены соответственно к стробирующим выходам блока управления 5 выходы n аналого-цифровых преобразователей подключе ны к соответ- СТВУ101ЦИМ входам дегчифратора и регистра, вход стробирования которого через элемент задержки подключен к выходу сигнала переключения скорости записи блока управления, выход дешифратора соединен с информационным входом блока оперативной памяти, адресный вход которого объединен с адресным входом мультиплексора и подключен к адресному выходу блока управления, выход блока оперативной памяти подключен к первому входу коммутатора, второй вход которого соединен с выходом мультиплексора, входы которого соединены с соответ ствующими выходами регистра, причем вход управления коммутатора соединен с выходом управления считыванием блока управления, выход является выходной миной, а тактовый вход блок управления соединен с выходом генера тора тактовых импульсов, входы Пуск и Разренение записи блока управления являются соответственно шинами Пуск и Разрегаение записи.

2„ Регистратор по п.1, о т л и чающийся тем, что блок управ- записи блока управления.

запаси

ления вьшолнен на двух триггерах, регистре сдвига, генераторе адреса, дешифраторе и делителе частоты, тактовьш вход которого является тактовым входом блока управления, а выход делителя частоты подключен к тактовым входам регистра сдвига и генератора адреса, выход которого подключен к входу дешифратора и является адресньм выходом блока управления, первый выход дешифратора является вькодом управления считыванием блока управления, а второй выход подключен к первому входу управления делителя частоты, второй вход управления которого объединен с первым входом установки первого триггера, входом установки генератора адреса, входом установки режима работы регистра сдвига, соединен с выходом второго триггера и является 1выходом сигнала переключения скорости записи блока управления, стробирую- щие выходы которого являются первыми выходами регистра сдвига, второй выход которого соединен с первым входом установки Второго триггера, информационный вход регистра сдвига соединен с выходом первого триггера, второй вход установки которого является входом Пуск блока; управления, второй вход установки второго -триг- гера является входом Разрешение

фиг, г

1378059

/f 1ляплш1дл;ш11гитпя

.-JbJlJlJl-n ПП

Фие.З

| ВСЕСОЮЗНАЯ п;.т:н.но-1[хш!^гнАя | 0 |

|

SU373695A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Цифровой регистратор однократныхиМпульСОВ | 1979 |

|

SU851765A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-02-28—Публикация

1986-06-06—Подача