00

00 :л

:о

113

Изобретение относится к цифровой вычислительной технике и может быть использовано при проектировании самоконтролируемых больших интегральных схем (ВИС) для цифровых вычислительных машин и систем.

Цель изобретения - повышение оперативности контроля путем обеспечения проверки выводов за один цикл, а также расширение области применения за счет обеспечения возможности совмещения контроля выводов БИС с контролем правильности функционирования.

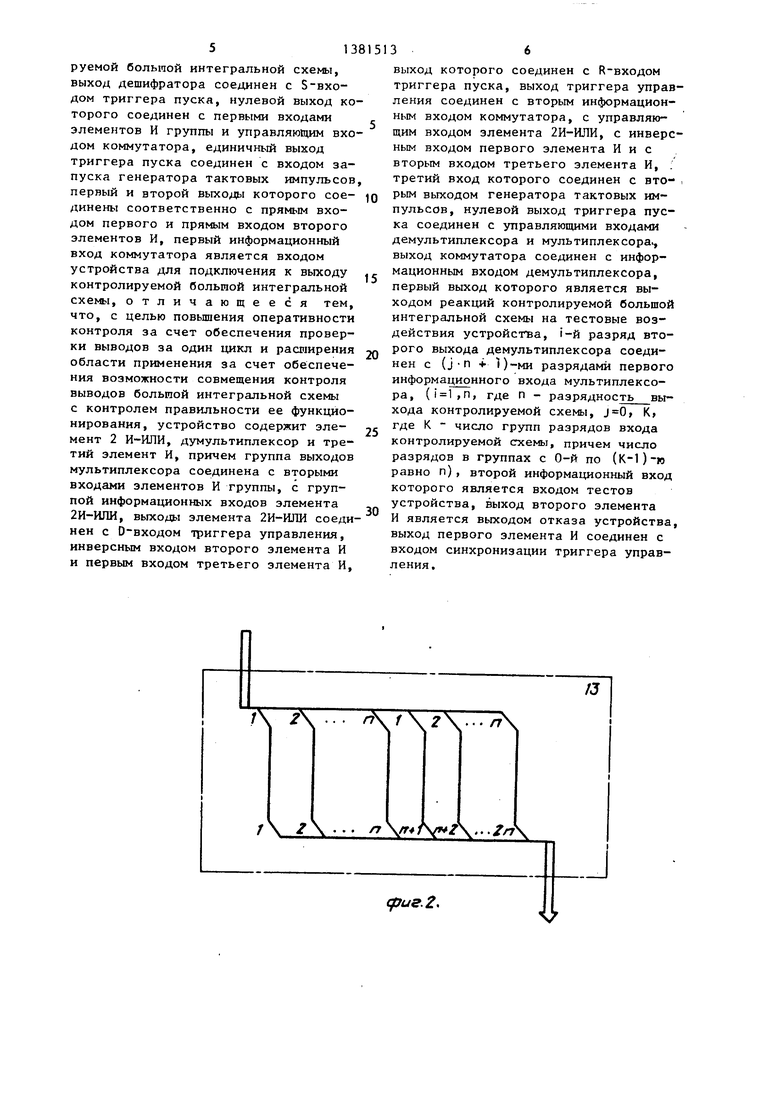

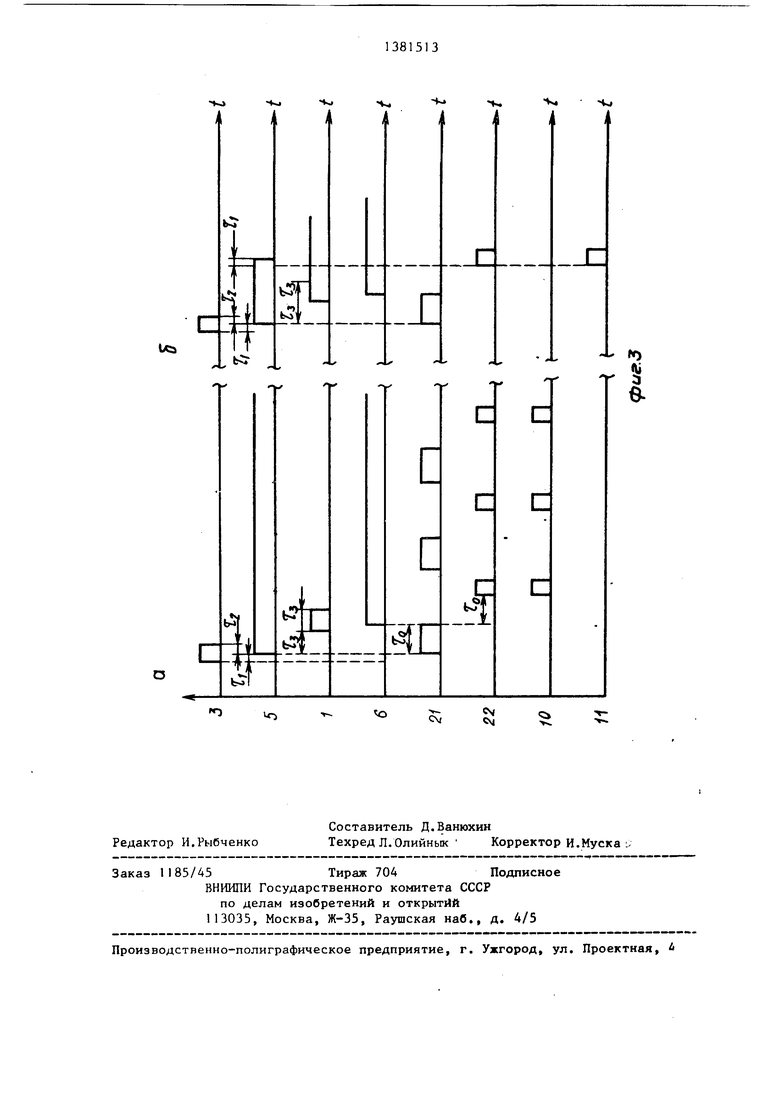

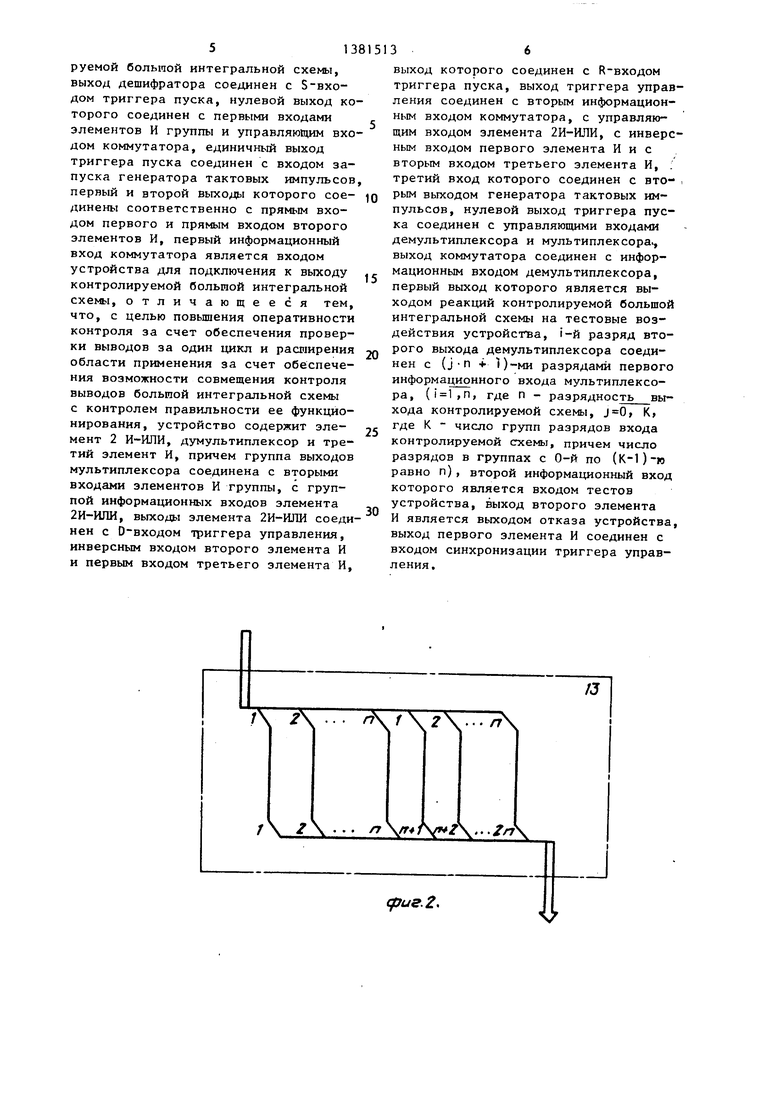

На фиг.1 представлена функциональная схема устройства; на фиг.2 - схема подключения второго выхода демуль- типлексора к первому входу мультиплексора; на фиг.З - временная диа- грамма работы устройства.

Устройство для контроля выводов БИС (фиг.1) сод ержит элемент 2И- ИЛИ 1, коммутатор 2, дешифратор 3, генератор 4 тактовых импульсов, триг геры пуска 5 и управления 6, демуль- типлексор 7, мультиплексор 8, группу 9 элементов И, первый 10, второй 11 и третий 12 элементы И, информационный вход 13 мультиплексора, информационные вход 14 и выход 15 устройства, выход 16 коммутатора 2, выход 17 триггера 5 пуска, выход 18 отказа, тестовые вход 19 и выход 20 реакций контролируемой БИС на тестовые воздействия устройства, выход 21 мультиплексора 8, первый 22 и второй 23 выходы генератора 4.

Элемент 2И-Ш1И 1 предназначен для формирования обобщенного сигнала отка- за в соответствии с логической функ- цией

h

Z X Л у, + X ,Л у ,

где X «(О, 1) - значение управляющег

сигнала;

у.е(0,1) - значение сигнала i-r разряда информацион ного входа;

,п - номер разряда информационного входа. При нулевом (единичном) значении управляющего сигнала, если на его информационный вход поступает код, содержащий хотя бы одну единицу (один нуль), то на его выходе фор- мируется нулевой сигнал.

Коммутатор 2 предназначен для коммутации рабочей информации с входа 14 устройства (контрольного кода

0

5 5

0

5

0 5

0

132

с выхода триггера 6) на выводы модуля при (нулевом, единичном) состоянии триггера 5 пуска. Дешифратор 3 крда начала контроля предназначен для формирования сигнала управления триггером 5 пуска. Генератор 4 тактовых импульсов предназначен для формирования последовательности тактовых импульсов, синхронизирующих работу устройства. Триггер 5 пуска предназначен для формирования сигнала управления запуском генератора 4 тактовых импульсов. Триггер 6 управления предназначен для формирования контрольного кода и управления работой устройства.

Демультиплексор 7 служит для коммутации выходных сигналов устройства. При единичном сигнале на его управляющем входе сигналы, поступающие на его информационный вход, коммутируются на его первый выход, являющийся выходом 20 устройства, а при нулевом управляющем сигнале сигналы, поступающие на его информационный вход, коммутируются на его второй выход. Мультиплексор 8 предназначен для соединения входов модуля i БИС с выходой демультиплексора при нулевом управляющем сигнале, с тестовым входом 19 устройства при единичном управляющем сигнале. Группа 9 элементов И предназначена для отключения модуля от выводов при их контроле.

Элемент И 10 служит для управления записью информации в триггер 6 управления. Элемент И 11 служит для формирования сигнала отказа. Элемент И 12 предназначен /.щя формирования сигнала выключения триггера 5 пуска.

Устройство работает следующим образом.

В исходном состоянии триггеры 5 пуска и 6 управления обнулены, на выходе 17 присутствует единичный сиг- нал (цепи установки исходного состояния, общий для схемы модуля БИС и для предлагаемого устройства, условно не показаны). При этом демульти- плексор 7 коммутирует выход 16 коммутатора 2 на выход 20 устройства, а мультиплексор 8 соединяет вход 19 устройства с информационным входом группы, 9 элементов И.

Для организа1р1и контроля выводов модуля БИС на вход 19 устройства пог: дают код начала контроля, который через мультиплексор 8 и группу 9 элементов И поступает на вход дешифратора 3 кода начала контроля, который формирует на своем выходе единичный сигнал. По этому сигналу триггер 5 пуска устанавливается в единичное состояние. Единичный сигнал с его прямого выхода поступает на вход генератора 4, а нулевой сигнал с инверсного выхода поступает на управляющие входы коммутатора 2, группы 9 элементов И, мультиплексора 8 и демультиплексора 7.

Демультиплексор 7 перекоммутирует выход 16 коммутатора 2 на первый информационный вход мультиплексора, а мультиплексор 8 соединяет информационный вход группы 9 элементов И с вторым выходом демультиплексора. Таким образом, выво;. модуля, соответствующие его выходам, оказываются соединенными с его выводами, соответствующим его входам.

Нулевой контрольный код.формируемый триггером 6 управления, через коммутатор 2, демультиплексор 7 и мультиплексор 8, проходя через выводы модуля, поступает на информационный вход элемента 2И-ИЛИ I. Если в коде, поступающем на информационный вход элемента 2И-ИЛИ 1 присутствует хотя бы одна единица (что соответствует наличию хотя бы одной неисправности типа константа 1 или обрыв), то на его выходе присутствует нуль и последовательность тактовых импульсов, формируемых генератором 4 на втором выходе 23, через элемент И И поступает на выход 18 отказа. Если неисправность константа 1 отсутствует, то на выходе элемента 2И-ИЛИ 1 через время задержки, определенное цепью прохож.11ения контрольного кода и срабатывания элемента 2И-ИЛИ 1 ( j), появляется единица и по заднему фронту первого тактового импульса сформированного на. первом выходе 22 генератора 4, триггер 6 переходит в единичное состояние. На информационный вход элемента 2И-ИЛИ поступает единичный код (все разряды единичные На выходе элемента 2И-ИЛИ 1 через время задержки формируется единица, что соответствует отсутствию неисправностей типа константа О или короткое замыкание. Первый импульс, сформированный на выходе 23 генератора 4, проходит через элемент И 12, и триггер 5 пуска переходит в нулевое состояние. Единичный сигнал с

0

5

0

5

0

5.

0

5

0

5

его нулевого выхода переводит модуль в рабочее состояние (открывает группу 9 элементов И и переключает коммутатор 2), а также, поступая на управляющие входы демультиплексора 7 и мультиплексора 8, осуществляет перекоммутацию, благодаря которой выводе модуля оказываются соединенными с тестовыми входом 19 и выходом 20 реакции устройства.

Далее можно начать контроль правильности функ1Ц онирования модуля БИС, например, тестированием, пода-- вая на вход 19 устройства контрольные тесты, а с выхода 20 устройства снимая реакцию схемы модуля БИС на эти тесты. Код начала контроля выводов модуля БИС может размещаться как первый тест в тестовой последовательности, используемой для контроля правильности функционирования модуля БИС, и контроль выводов модуля может использоваться в качестве подконтро- ля более общего контроля правильности функционирования. Такая организация проведения контроля выводов модуля БИС позволяет исключить затраты времеР1и на контроль правильности функционирования модуля с неисправными выводами, а также на подключение модуля БИС к различным устройствам контроля. Если же присутствует хотя бы одна неисправность типа константа О, то на информационный вход элемента 2И-ИЛИ 1 поступает код, содержащий хотя бы один нуль. На выходе элемента 2И-ИЛИ I -через время задержки i, формируется нулевой сигнал, и последовательность импульсов, формируемых на втором выходе 23 генератора 4, поступает через элемент . И 11 на выход 18 отказа устройства.

Таким образом осуществляется контроль выводов модуля перед началом контроля правильности его функционирования.

Формула изобретения

Устройство для контроля выводов больших интегральных схем, содержащее коммутатор, дешифратор, генератор тактовых импульсов, триггеры пуска и управления, группу элементов И, первый и второй элементы И, причем выходы элементов И группы соединены с группой информационных входов дешифратора и образуют выход устройства для подключения к входу контроля-,

5138

руемой большой интегральной схемы, выход дешифратора соединен с S-входом триггера пуска, нулевой выход которого соединен с первыми входами элементов И группы и управляющим входом коммутатора, единичный выход триггера пуска соединен с входом запуска генератора тактовых импульсов первый и второй выходы которого сое- динены соответственно с прямым входом первого и прямым входом второго элементов И, первый информационный вход коммутатора является входом устройства для подключения к выходу контролируемой большой интегральной схемы, отличающееся тем, что, с целью повьшения оперативности контроля за счет обеспечения проверки выводов за один цикл и расширения области применения за счет обеспечения возможности совмещения контроля выводов большой интегральной схемы с контролем правильности ее функционирования, устройство содержит элемент 2 И-ИЛИ, думультиплексор и третий элемент И, причем группа выходов мультиплексора соединена с вторыми входами элементов И группы, с группой информационных входов элемента 2И-ИПИ, выходы элемента 2И-ИЛИ соединен с D-ВХОДОМ триггера управления, инверсным входом второго элемента И и первым входом третьего элемента И,

5

0

5

0

36

выход которого соединен с R-входом триггера пуска, выход триггера управления соединен с вторьм информационным входом коммутатора, с управляющим входом элемента 2И-ИЛИ, с инверсным входом первого элемента И и с вторым входом третьего элемента И, . третий вход которого соединен с вто- рым выходом генератора тактовых импульсов, нулевой выход триггера пуска соединен с управляющими входами демультиплексора и мультиплексора., выход коммутатора соединен с информационным входом демультиплексора, первый выход которого является выходом реакций контролируемой большой интегральной схемы на тестовые воздействия устройства, i-й разряд второго выхода демультиплексора соединен с (j п 1)-ми разрядами первого информационного входа мультиплексора, (, где п - разрядность вы- хода контролируемой схемы, К где К - число групп разрядов входа контролируемой схемы, причем число разрядов в группах с 0-й по (К-1)-ю равно п), второй информационный вход которого является входом тестов устройства, выход второго элемента И является выходом отказа устройства, выход первого элемента И соединен с входом синхронизации триггера управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультиплексор с контролем | 1985 |

|

SU1471194A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Микропрограммное устройство управления модуля распределенной параллельной вычислительной системы | 1985 |

|

SU1252775A1 |

| Модульное устройство для программного управления и контроля | 1988 |

|

SU1647519A1 |

| Устройство для контроля БИС | 1984 |

|

SU1264181A1 |

| Устройство для формирования маршрута сообщения в однородной вычислительной системе | 1988 |

|

SU1501080A1 |

| Устройство для управления,контроля и диагностирования | 1985 |

|

SU1297063A1 |

| Программируемый управляющий модуль | 1989 |

|

SU1649506A1 |

| Адаптивный модуль микропрограммного устройства управления | 1984 |

|

SU1273926A1 |

| Мультимикропрограммное устройство управления с контролем | 1985 |

|

SU1272333A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано при проектировании самоконтролируемых больших интегральных схем (БИС) для цифровых вычислительных машин и систем. Цель изобретения - повыгаение оперативности контроля путем обеспечения проверки выводов за один цикл и расширение области применения устройства за счет обеспечения возможности совмещения контроля выводов БИС с контролем правильности ее функционирования. Устройство для контроля выводов БИС содержит элемент 2И-ИЛИ 1, коммутатор 2, дешифратор 3, генератор тактовых импульсов 4, триггеры пуска 5 и управления 6, группу 9 элементов И, первый 10, второй II и третий 12 элементы И, демультиплексор выводов 7, мультиплексор 8. 3 ил. (Л

Г /7

/ / . . . /7 уг Л

..J

(риг.2

7

| Микропрограммное устройство управления | 1981 |

|

SU1015383A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля БИС | 1984 |

|

SU1264181A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-03-15—Публикация

1986-06-17—Подача