(54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В ДВОИЧНОДЕСЯТИЧНЫЙ И ДВОИЧНО-ДЕСЯТИЧНОГО В ДВОИЧНЫЙ

выход разрешения коррекции соединен с управляющим входом блока коррекции, выход разре1иения передачи блока управления соединен с управляющим входом первого элемента И-ИЛИ, первый вход которого соединен с информационным входом преобразователя, второй .вход- с выходом первого разряда первого сдвигового регистра, а выход первого элемента И-ИЛИ соединен с первым входом сумматора, второй вход которого соединен с выходом блока коррекции, а выход сумматора соединен с входом второго сдвигового регистра, выходы четвертого и пятого разрядов первого сдвигового регистра соединены с.входами блока коррекции, дополнительно введены два элемента И и блок приема информации, первый вход которого соединен с информационным входом преобразователя, второй вход - с выходом первого элемента И, третий вход блока приема информации соединен через одноразрядный регистр сдвига с выходом второго элемента И, четвертый и пятый входы соединены с выходами первого и третьего разрядов второго сдвигового регистра соответственно, пятый вход блока приема информации соединен с первым входом первого элемента И, второй вход которого соединен с тактовым входом преобразователя, а третий вход первого элемента И соединен с выходом разрешения регенерации блока управления, выход разрешения приема блока управления соединен с первым входом второго элемента И, второй вход которого соединен с информационным входом преобразователя, первый вход второго элемента ИИЛИ соединен с выходом второго разряда второго сдвигового регистра, второй вход - с выходом первого разряда первого сдвигового регистра, третий вход соединен с выходом разрешения выдачи блока управления, выходы разрешения приема которого соединены с управляющими входами блока приема информации, выход которого соединен с входом первого сдвигового регистра, выход второго элемента И-ИЛИ является выходом преобразователя, кроме того, в нем блок приема информации содержит три элемента И и элемент ИЛИ, первый, ..второй и третий входы которого соединены с выходами соответствующих элементов И, а выход элемента ИЛИ является выходом блока приема информации, первый вход первого элемента И является первым входом блока приема информации, второй и третий входы которого соединены с четвертым и пятым входом элемента ИЛИ соответственно, первые входы второго и третьего элементов И являются четвертым и пятым входами блока приема информации соответственно, управляющие входы которого соединены со втог рыми входами первого, второго и третьего элементов И. Кроме того в нем блок коррекции содержит два D-триггепа, четыре элемента И, три элемента И,Л, распределитель импульсов и преобразователь параллельного кода в последовательный, первый и второй входы которого соединены с выходами первого и второго элементов ИЛИ, управляющие входы соединены с выходами распределитрля импульсов, вход которого соединен с выходом третьегб элемента ИЛИ и синхровходами D-триггеров, D-входы которых являются информационными входами блока коррекции, первый вход первого элемента И соединен с прямым выходом первого D-триггера, первые входы второго и третьего элементов И соединены с инверсным выходом второго D-триггера, первый вход четвертого элемента И соединен с прямым выходом второго D-триггера, остальные вхо, ды элементов И и первые входы второго и третьего элементов ИЛИ являются информационными входами блока коррекции, первый и второй входы первого элемента ИЛИ соединены с выходами первого и третьего элементов И, выход второго элемента

И соединен с третьим входом преобразователя параллельного кода в последовательный, выход которого является выходом блока коррекции, выход четвертого элемента И соединен, с вторым входом второго элемента ИЛИ, второй вход третьего элемента ИЛИ соединен с выходом старщего разряда распределителя импульсов.

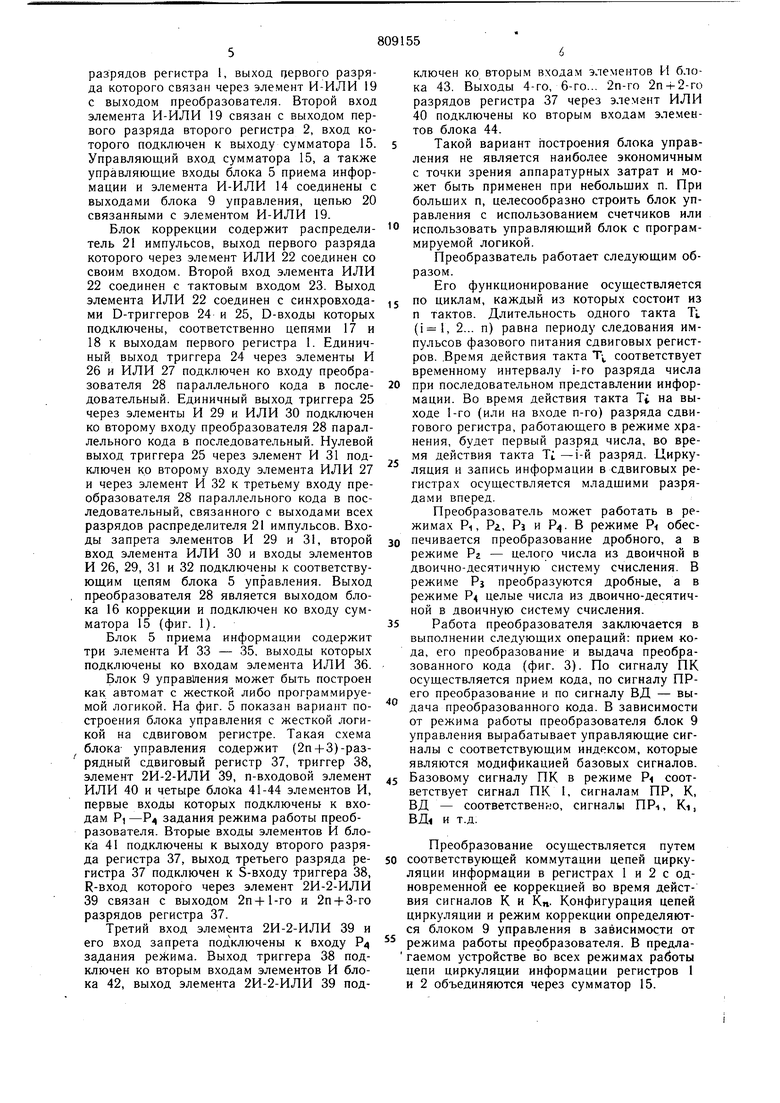

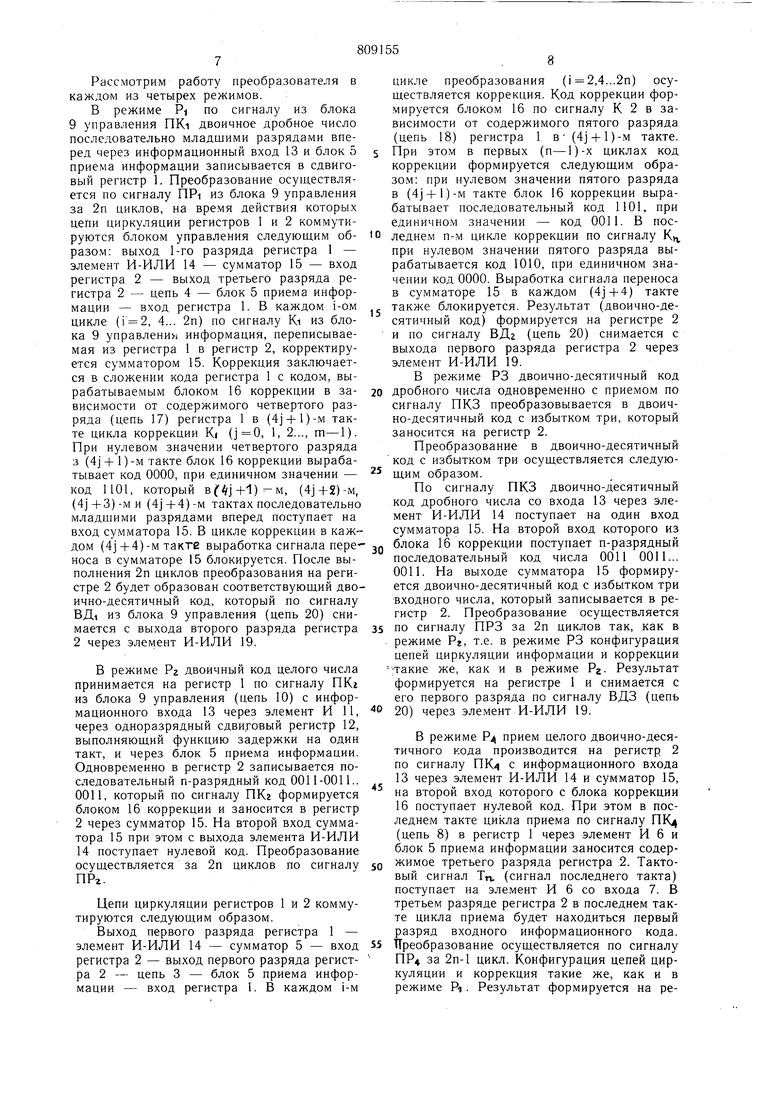

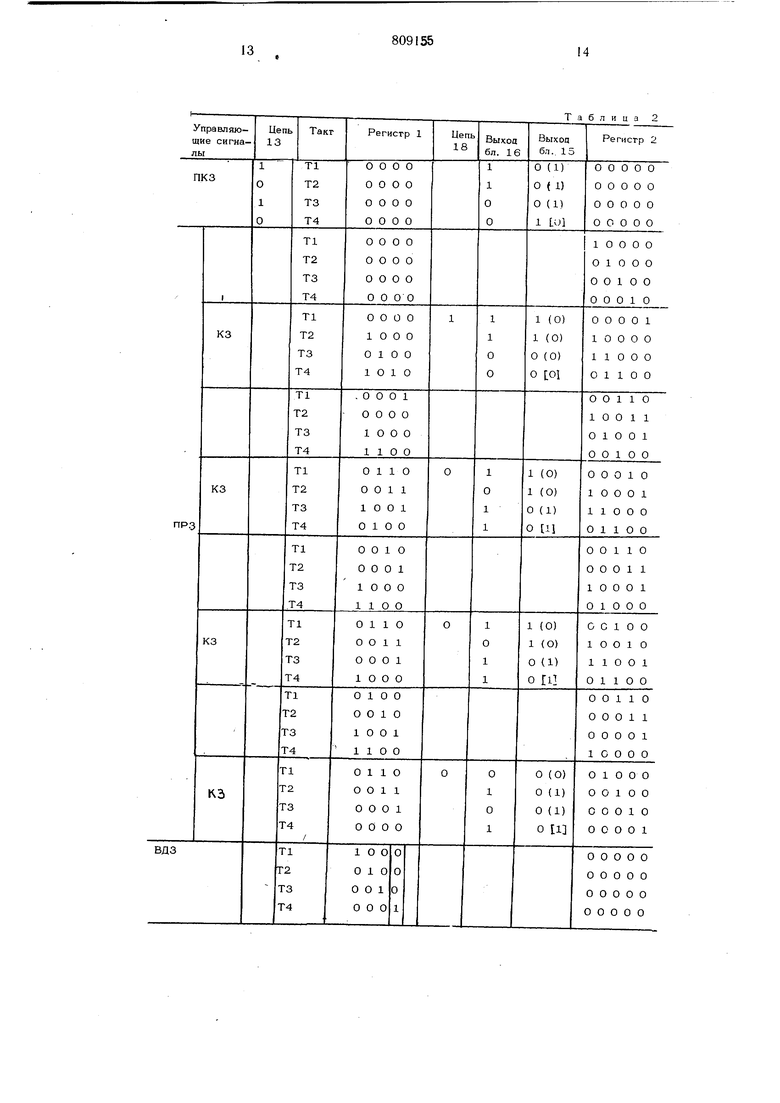

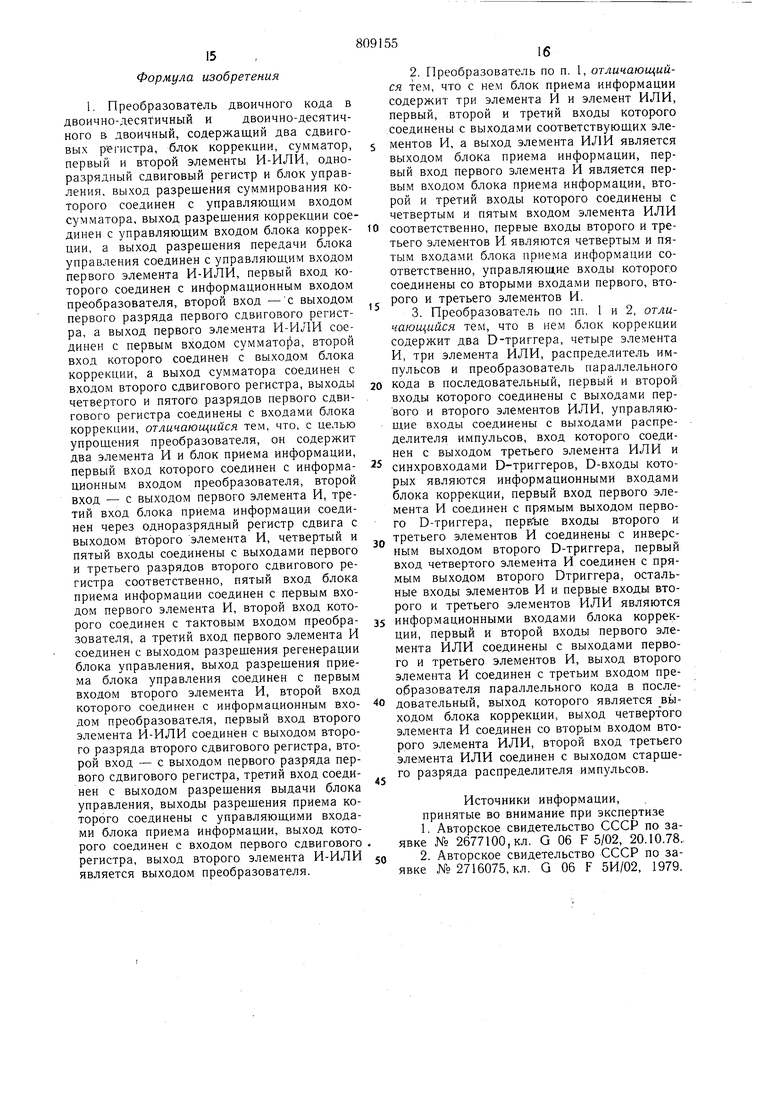

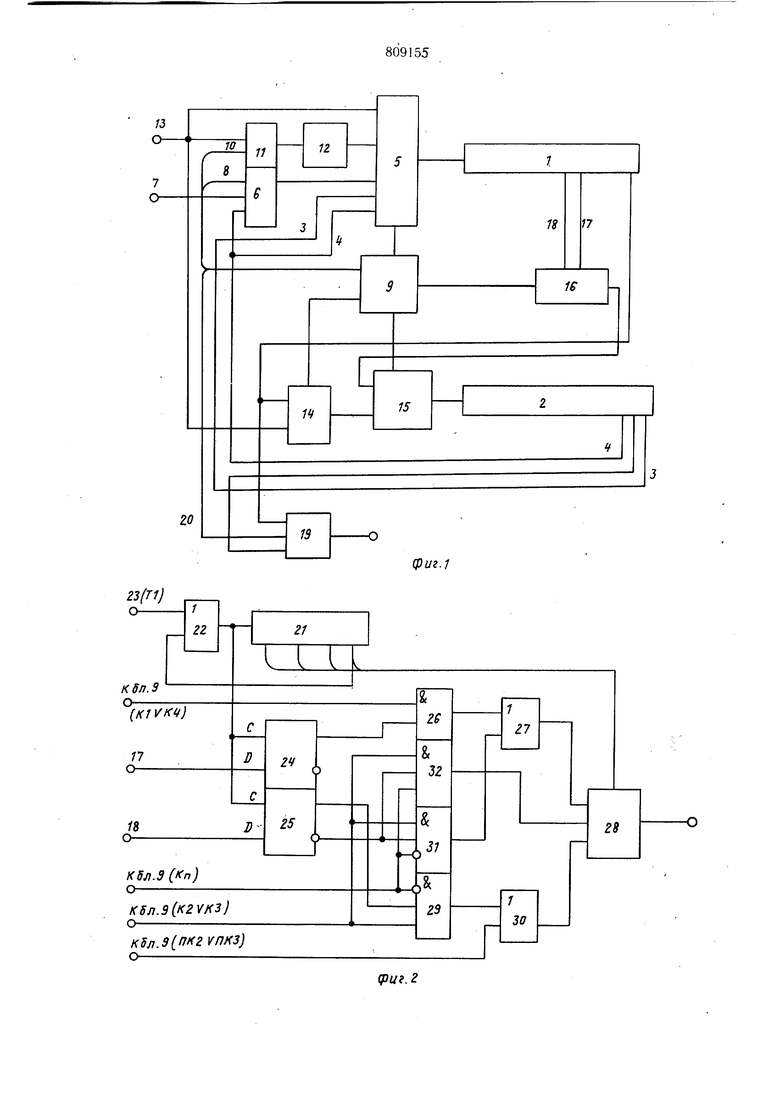

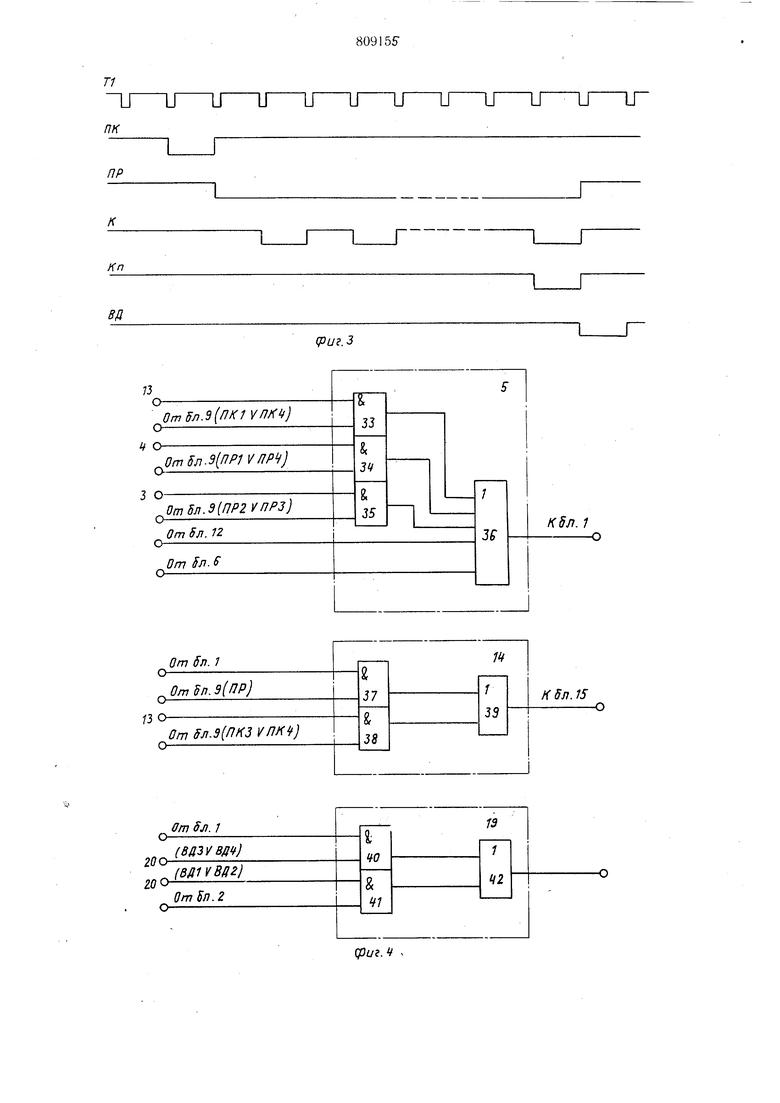

На фиг. 1 изображена структурная схема преобразователя; на фиг. 2 - блок-схема блока коррекции; на фиг. 3 - временная

0 диаграмма базовых сигналов преобразователя; на фиг. 4 - схема блока приема информации; на фиг. 5 - вариант построения блока управления.

Преобразователь содержит первый 1 и второй 2 сдвиговые регистры, причем разрядность первого регистра равна п(п 4т, где п - число десятичных разрядов преобразователя), разрядность второго регистра - (n-fl). Выходы первого разряда цепью 3 и третьего разряда цепью 4 второго сдвигового регистра 2 через первый блок 5 приема информации соединены со входом первого сдвигового регистра 1. Выход третьего разряда регистра 2 соединен со входом первого элемента И 6, выход которого соединен с блоком 5 приема информации. Два других

5 входа элемента И 6 подключены к тактовому входу 7 преобразователя и цепью 8 к блоку 9 управления, выход которого цепью 10 связан со вторым элементом И 11, выход которого через одноразрядный сдвиговый регистр 12 соединен с блоком 5 приема информации. Второй вход элемента И 11 подключен к входу блока 5 приема информации, к информационному входу 13 преобразователя и через эле.мент И-ИЛИ 14 к первому входу сумматора 15, второй вход которого подключен к выходу блока 16 коррекции, связанного с блоком 9 управления. Два входа блока 16 коррекции цепями 17 и 18 связаны с выходами четвертого и пятого

разрядов регистра 1, выход rjepeoro разряда которого связан через элемент И-ИЛИ 19 с выходом преобразователя. Второй вход элемента И-ИЛИ 19 связан с выходом первого разряда второго регистра 2, вход которого подключен к выходу сумматора 15. Управляющий вход сумматора 15, а также управляющие входы блока 5 приема информации и элемента И-ИЛИ 14 соединены с выходами блока 9 управления, цепью 20 связанными с элементом И-ИЛИ 19.

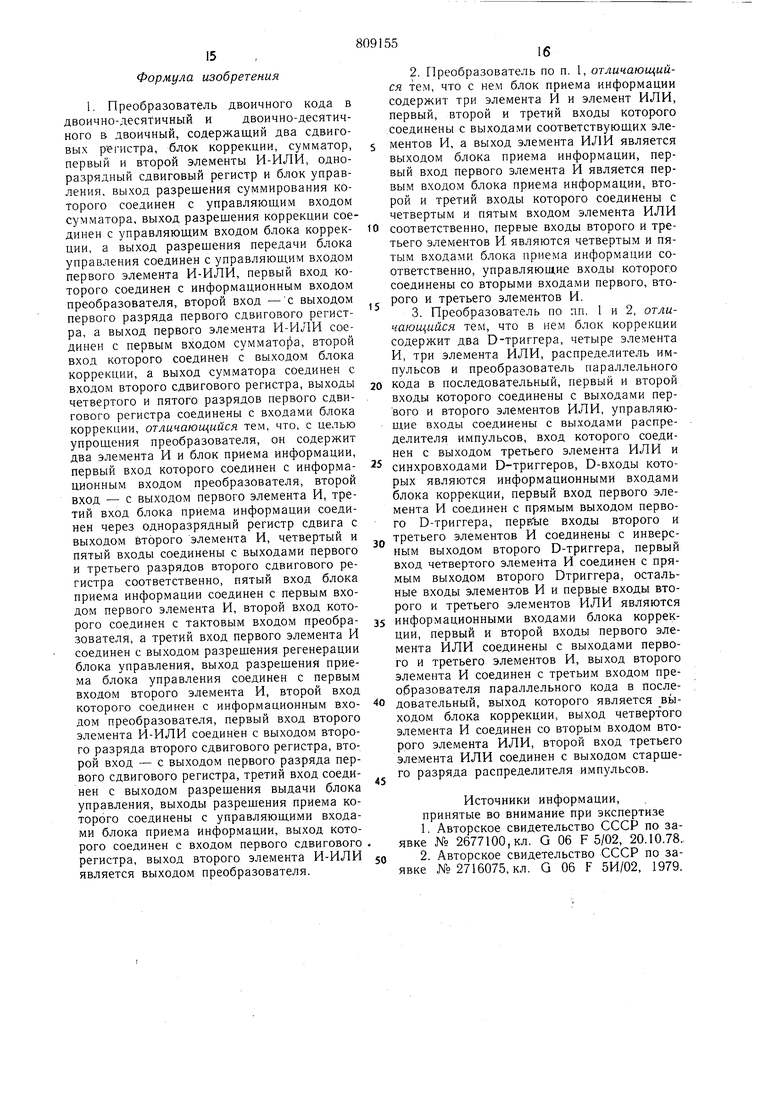

Блок коррекции содержит распределитель 21 импульсов, выход первого разряда которого через элемент ИЛИ 22 соединен со своим входом. Второй вход элемента ИЛИ 22 соединен с тактовым входом 23. Выход элемента ИЛИ 22 соединен с синхровходами D-триггеров 24 и 25, D-входы которых подключены, соответственно цепями 17 и 18 к выходам первого регистра 1. Единичный выход триггера 24 через элементы И 26 и ИЛИ 27 подключен ко входу преобразователя 28 параллельного кода в последовательный. Единичный выход триггера 25 через элементы И 29 и ИЛИ 30 подключен ко второму входу преобразователя 28 параллельного кода в последовательный. Нулевой выход триггера 25 через элемент И 31 подключен ко второму входу элемента ИЛИ 27 и через элемент И 32 к третьему входу преобразователя 28 параллельного кода в последовательный, связанного с выходами всех разрядов распределителя 21 импульсов. Входы запрета элементов И 29 и 31, второй вход элемента ИЛИ 30 и входы элементов И 26, 29, 31 и 32 подключены к соответствующим цепям блока 5 управления. Выход преобразователя 28 является выходом блока 16 коррекции и подключен ко входу сумматора 15 (фиг. 1).

Блок 5 приема информации содержит три элемента И 33 - 35, выходы которых подключены ко входам элемента ИЛИ 36.

Блок 9 управления может быть построен как автомат с жесткой либо программируемой логикой. На фиг. 5 показан вариант построения блока управления с жесткой логикой на сдвиговом регистре. Такая схема блока- управления содержит (2п + 3)-разрядный сдвиговый регистр 37, триггер 38, элемент 2И-2-ИЛИ 39, п-входовой элемент ИЛИ 40 и четыре блока 41-44 элементов И, первые входы которых подключены к входам PI -Р задания режима работы преобразователя. Вторые входы элементов И блока 41 подключены к выходу второго разряда регистра 37, выход третьего разряда регистра 37 подключен к S-входу триггера 38, R-вход которого через элемент 2И-2-ИЛИ 39 связан с выходом 2пЧ-1-го и 2п-|-3-го разрядов регистра 37.

Третий вход элемента 2И-2-ИЛИ 39 и его вход запрета подключены к входу Р задания режима. Выход триггера 38 подключен ко вторым входам элементов И блока 42, выход элемента 2И-2-ИЛИ 39 подключен ко вторым входам элементов И блока 43. Выходы 4-го, 6-го... 2п-го 2п + 2-го разрядов регистра 37 через элемент ИЛИ 40 подключены ко вторым входам элементов блока 44.

5Такой вариант построения блока управления не является наиболее экономичным с точки зрения аппаратурных затрат и может быть применен при небольщих п. При больщих п, целесообразно строить блок управления с использованием счетчиков или

использовать управляющий блок с программируемой логикой.

Преобразватель работает следующим образом.

Его функционирование осуществляется

5 по циклам, каждый из которых состоит из п тактов. Длительность одного такта TL (, 2... п) равна периоду следования импульсов фазового питания сдвиговых регистров. .Время действия такта Т соответствует временному интервалу i-ro разряда числа

0 при последовательном представлении информации. Во время действия такта Ti на выходе 1-го (или на входе п-го) разряда сдвигового регистра, работающего в режиме хранения, будет первый разряд числа, во время действия такта Ti -i-й разряд. Циркуляция и запись информации в сдвиговых регистрах осуществляется младщими разрядами вперед.

Преобразователь может работать в режимах Pi, Рг, РЗ и Р. В режиме Р обеспечивается преобразование дробного, а в режиме Рг - целого числа из двоичной в двоично-десятичную систему счисления. В режиме PJ преобразуются дробные, а в режиме Р4 целые числа из двоично-десятичной в двоичную систему счисления.

5 Работа преобразователя заключается в выполнении следующих операций: прием кода, его преобразование и выдача преобразованного кода (фиг. 3). По сигналу ПК осуществляется прием кода, по сигналу ПРего преобразование и по сигналу ВД - выдача преобразованного кода. В зависимости от режима работы преобразователя блок 9 управления вырабатывает управляющие сигналы с соответствующим индексом, которые являются модификацией базовых сигналов.

5 Базовому сигналу ПК в режиме Р соответствует сигнал ПК 1, сигналам ПР, К, ВД - соответственгю, сигналы ПР-), Ki, ERi и т.д.

Преобразование осуществляется путем 0 соответствующей коммутации цепей циркуляции информации в регистрах 1 и 2 с одновременной ее коррекцией во время действия сигналов К и Кп- Конфигурация цепей циркуляции и режим коррекции определяются блоком 9 управления в зависимости от режима работы преобразователя. В предлагаемом устройстве во всех режимах работы цепи циркуляции информации регистров 1 и 2 объединяются через сумматор 15.

Рассмотрим работу преобразователя в каждом из четырех режимов.

В режиме PI по сигналу из блока 9 управления FlKi двоичное дробное число последовательно младшими разрядами вперед через информационный вход 13 и блок 5 приема информации записывается в сдвиговый регистр 1. Преобразование осуществляется по сигналу nPi из блока 9 управления за 2п циклов, на время действия которых цепи циркуляции регистров 1 и 2 коммутируются блоком управления следующим образом: выход 1-го разряда регистра 1 - элемент И-ИЛИ 14 - сумматор 15 - вход регистра 2 - выход третьего разряда регистра 2 - цепь 4 - блок 5 приема информации - вход регистра 1. В каждом i-ом цикле (i 2, 4... 2п) по сигналу Ki из блока 9 управление информация, переписываемая из регистра 1 в регистр 2, корректируется сумматором 15. Коррекция заключается в сложении кода регистра 1 с кодом, вырабатываемым блоком 16 коррекции в зависимости от содержимого четвертого разряда (цепь 17) регистра 1 в (4j-f 1)-м такте цикла коррекции Ki (, 1, 2..., m-1). При нулевом значении четвертого разряда 3 (4J + 1)-м такте блок 16 коррекции вырабатывает код 0000, при единичном значении - код 1101, который Bf4j+1)M, (4j+2)-M, (4j+3)-MH (4j + 4)-M тактах последовательно младшими разрядами вперед поступает на вход сумматора 15. В цикле коррекции в каждом (4J+4)-м такте выработка сигнала переноса в сумматоре 15 блокируется. После выполнения 2п циклов преобразования на регистре 2 будет образован соответствующий двоично-десятичный код, который по сигналу ВДн из блока 9 управления (цепь 20) снимается с выхода второго разряда регистра 2 через элемент И-ИЛИ 19.

В режиме Рг двоичный код целого числа принимается на регистр 1 по сигналу ПКг из блока 9 управления (цепь 10) с информационного входа 13 через элемент И 11, через одноразрядный сдвиговый регистр 12, выполняющий функцию задержки на один такт, и через блок 5 приема информации. Одновременно в регистр 2 записывается последовательный п-разрядный код 0011-0011.. ООП, который по сигналу ПКг формируется блоком 16 коррекции и заносится в регистр 2 через сумматор 15. На второй вход сумматора 15 при этом с выхода элемента И-ИЛИ 14 поступает нулевой код. Преобразование осуществляется за 2п циклов по сигналу ПРг.

Цепи циркуляции регистров 1 и 2 коммутируются следующим образом.

Выход первого разряда регистра 1 - элемент И-ИЛИ 14 - сумматор 5 - вход регистра 2 - выход первого разряда регистра 2 - цепь 3 - блок 5 приема информации - вход регистра 1. В каждом i-м

цикле преобразования (i 2,4...2n) осуществляется коррекция. Код коррекции формируется блоком 16 по сигналу К 2 в зависимости от содержимого пятого разряда (цепь 18) регистра 1 в (4j + l)-M такте. При этом в первых (п-1)-х циклах код коррекции формируется следующим образом: при нулевом значении пятого разряда в (4j + l.)-M такте блок 16 коррекции вырабатывает последовательный код 1101, при единичном значении - код ООП. В последнем п-м цикле коррекции по сигналу К при нулевом значении пятого разряда вырабатывается код 1010, при единичном значении код 0000. Выработка сигнала переноса в сумматоре 15 в каждом (4j-f4) такте также блокируется. Результат (двоично-десятичный код) формируется на регистре 2 и по сигналу ВДг (цепь 20) снимается с выхода первого разряда регистра 2 через элемент И-ИЛИ 19.

В режиме РЗ двоично-десятичный код дробного числа одновременно с приемом по сигналу ПКЗ преобразовывается в двоично-десятичный код с избытком три, который заносится на регистр 2.

Преобразование в двоично-десятичный код с избытком три осуществляется следующим образом.

По сигналу ПКЗ двоично-десятичный код дробного числа со входа 13 через элемент И-ИЛИ 14 поступает на один вход сумматора 15. На второй вход которого из блока 16 коррекции поступает п-разрядный последовательный код числа ООП ООП... ООП. На выходе сумматора 15 формируется двоично-десятичный код с избытком три входного числа, который записывается в регистр 2. Преобразование осуществляется по сигналу ПРЗ за 2п циклов так, как в режиме Рг, т.е. в режиме РЗ конфигурация цепей циркуляции информации и коррекции гтакие же, как и в режиме Pg. Результат формируется на регистре 1 и снимается с его первого разряда цо сигналу ВДЗ (цепь 20) через элемент И-ИЛИ 19.

В режиме Р прием целого двоично-десятичного кода производится на регистр 2 по сигналу ПК с информационного входа 13 через элемент И-ИЛИ 14 и сумматор 15, на второй вход которого с блока коррекции 16 поступает нулевой код. При этом в последнем такте цикла приема по сигналу ПК4 (цепь 8) в регистр 1 через элемент И 6 и блок 5 приема информации заносится содержимое третьего разряда регистра 2. Тактовый сигнал Тп, (сигнал последнего такта) поступает на элемент И 6 со входа 7. В третьем разряде регистра 2 в последнем такте цикла приема будет находиться первый разряд входного информационного кода. Преобразование осуществляется по сигналу ПР4 за 2п-1 цикл. Конфигурация цепей циркуляции и коррекция такие же, как и в режиме Рц . Результат формируется на регистре 1 i снимается с выхода его первого разряда через элемент И-ИЛИ 19.

Блок 16 коррекции работает следующим образом.

В четырехразрядный распределитель 21 импульсов в первом такте каждого цикла через элемент ИЛИ 22 заносится единица, которая циркулирует, проходя через элемент ИЛИ 22. Таким образом, на выходе элемента ИЛИ 22 формируются тактовые сигналы Т (4J +1), по которым на D-триггер 24 в (4j + l)-M такте записывается содержимое четвертого разряда регистра 1, на D-триггер 25 - содержимое-пятого разряда регистра 1.

Таким образом логические формулы X условий выработки блоком 16 формирования коррекции соответствующих кодов имеют вид:

Хоом НК2УПКЗУ(КгУКз) KrvC5j, X«oi (KiV K)C4V(KtVK3) КцСБ; X«« (КгУКзЖпСб, где С и GS - состояния триггеров 24 и 25 соответственно.

Условия X вырабатываются элементами И 26, 29, 31 и 32, а также элементами ИЛИ

27и 30. Условие Хоои вырабатывается на выходе элемента ИЛИ 30, условие X-iioi на выходе элемента ИЛИ 27 и условие на выходе элемента И 32. Преобразователь

28преобразовывает унитарный код условий X в соответствующий последовательный код ООП, 1101 или 1010. Тактовые сигналы T(4j + l), T(4j+2), T(4j-f3) и T(4j + 4) ырабатываются на соответствующих выходах распределителя 21 импульсов и поступают на преобразователь 28 для синхронизации кода коррекции.

Входами блока 9 управления является вход тактирующего сигнала Ti, определяющий начало каждого цикла работы преобразователя и входы задания режима работы преобразователя PI, PI, РЗ и Рд. По сигналу начала работы (HP), поступающему на D-вход регистра 37, в первый разряд регистра записывается единица. Каждым сигналом TI в регистре 37 осуществляется сдвиг на один разряд в сторону старщих разрядов. После воздействия первого сигнала TI на выходе второго разряда регистра 37 формируется базовый управляющий сигнал ПК, длительность которого равна одному циклу. В следующем цикле сигналом с третьего разряда регистра 37 осуществляется установка в единичное состояние триггера 38. Сброс триггера 38 осуществляетется через элемент 2И-2 ИЛИ 39 с выхода 2п+1-го разряда в режиме Р и с выхода

2п + 3-го разряда регистра 37 в других режимах. Таким образом, на выходе триггера 38 формируется базовый управляющий сигнал ПР, длительность которого в режиме Р4 равна 2п-1 циклов, в других режимах 2-Л циклов. На выходе элемента 2И2-ИЛИ 39 формируется базовый управляющий сигнал ВД, длительность которого равна одному циклу. С выхода 2n-f2-ro разряда регистра 37 снимается сигнал Кп Выходы 4-го, 6-го, 8-го..., (2п-2)-го, 2п-го,

10 (2п + 2)-го разрядов объединены через элемент ИЛИ 40, на выходе которого формируется базовый управляющий сигнал К. На выходах элементов И блоков 41-44 формируются основные модифицированные управляющие сигналы блока управления

ПК1, ПР1, ВДи и К1 (i l, 2, 3, 4) в зависимости от задания режима работы преобразователя. Так, управляющий сигнал ПК| формируется на основе базового сигнала ПК выхода элемента И блока 41, на

0 вход которого заведена шина Pi. Управляющий сигнал UPi формируется на основе базового управляющего сигнала ПР на выходе элемента И блока 42, на вход которого заведена щина Р. и т.д. Таким образом обеспечивается выработка всех управляю щих сигналов блока управления. В табл. 1

показана работа преобразователя в режиме

Р при преобразовании числа (0,1000)г

(0,0101)40 из двоичной системы счисления

в двоично-десятичную. В табл. 2 показана

Q работа устройства в режиме РЗ при преобразовании числа (O.OlOl)io (0,1000) из двоично-десятичной системы счисления.

В скобках приведено значение переноса, сформированное в i-ом такте и учитываемое

5 в (i + l)-M такте; квадратными скобками выделены переносы, выработка которых блокируется.

Так как в рассмотренном примере регистр 1 четырехразрядный, то в цикле коррекции для выработки необходимого кода коррекции

° анализируется выход первого разряда регистра 2. Это следует из того, что цепи циркуляции информации в регистрах 1 и 2 объединены, и пятым разрядом регистра 1 как бы является первый разряд регистра 2.

5 Предлагаемое устройство является устройством последовательного действия и применение в нем динамических многоразрядных регистров позволяет существенно снизить стоимость, уменьщить габариты и повысить его надежность. Оно позволяет умень0 щить количество э лементов И-ИЛИ, триггеров и упростить блок коррекции.

Таблица 15 Формула изобретения 1. Преобразователь двоичного кода в двоично-десятичный и двоично-десятичного в двоичный, содержащий два сдвиговых регистра, блок коррекции, сумматор, первый и второй элементы И-ИЛИ, одноразрядный сдвиговый регистр и блок управления, выход разрешения суммирования которого соединен с управляющим входом сумматора, выход разрещения коррекции соединен с управляющим входом блока коррекции, а выход разрешения передачи блока управления соединен с управляющим входом первого элемента И-ИЛИ, первый вход которого соединен с информационным входом преобразователя, второй вход -с выходом первого разряда первого сдвигового регистра, а выход первого элемента И-ИЛИ соединен с первым входом суммато{ а, второй вход которого соединен с выходом блока коррекции, а выход сумматора соединен с входом второго сдвигового регистра, выходы четвертого и пятого разрядов первого сдвигового регистра соединены с входами блока коррекции, отличающийся тем, что, с целью упрощения преобразователя, он содержит два элемента И и блок приема информации, первый вход которого соединен с информационным входом преобразователя, второй вход - с выходом первого элемента И, третий вход блока приема информации соединен через одноразрядный регистр сдвига с выходом второго элемента И, четвертый и пятый входы соединены с выходами первого и третьего разрядов второго сдвигового регистра соответственно, пятый вход блока приема информации соединен с первым входом первого элемента И, второй вход которого соединен с тактовым входом преобразователя, а третий вход первого элемента И соединен с выходом разрещения регенерации блока управления, выход разрещения приема блока управления соединен с первым входом второго элемента И, второй вход которого соединен с информационным входом преобразователя, первый вход второго элемента И-ИЛИ соединён с выходом второго разряда второго сдвигового регистра, второй вход - с выходом первого разряда первого сдвигового регистра, третий вход соединен с выходом разрещения выдачи блока управления, выходы разрешения приема которого соединены с управляющими входами блока приема информации, выход которого соединен с входом первого сдвигового регистра, выход второго элемента И-ИЛИ является выходом преобразователя. 2.Преобразователь по п. 1, отличающийся тем, что с нем блок приема информации содержит три элемента И и элемент ИЛИ, первый, второй и третий входы которого соединены с выходами соответствующих элементов И, а выход элемента ИЛИ является выходом блока приема информации, первый вход первого элемента И является первым входом блока приема информации, второй и третий входы которого соединены с четвертым и пятым входом элемента ИЛИ соответственно, первые входы второго и третьего элементов И являются четвертым и пятым входами блока приема информации соответственно, управляющие входы которого соединены со вторыми входами первого, второго и третьего элементов И. 3.Преобразователь по пп. 1 и 2, отличающийся тем, что в нем блок коррекции содержит два D-триггера, четыре элемента И, три элемента ИЛИ, распределитель импульсов и преобразователь параллельного кода в последовательный, первый и второй входы которого соединены с выходами первого и второго элементов ИЛИ, управляющие входы соединены с выходами распределителя импульсов, вход которого соединен с выходом третьего элемента ИЛИ и синхровходами D-триггеров, D-входы которых являются информационными входами блока коррекции, первый вход первого элемента И соединен с прямым выходом первого D-триггера, nepBl ie входы второго и третьего элементов И соединены с инверсным выходом второго D-триггера, первый вход четвертого элемента И соединен с прямым выходом второго Dтpиггepa, остальные входы элементов И и первые входы второго и третьего элементов ИЛИ являются информационными входами блока коррекции, первый и второй входы первого элемента ИЛИ соединены с выходами первого и третьего элементов И, выход второго элемента И соединен с третьим входом преобразователя параллельного кода в последовательный, выход которого является вьь ходом блока коррекции, выход четвертого элемента И соединен со вторым входом второго элемента ИЛИ, второй вход третьего элемента ИЛИ соединен с выходом старшего разряда распределителя импульсов. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР по заявке № 2677100, кл. G 06 F 5/02, 20.10.78. 2. Авторское свидетельство СССР по заявке №2716075, кл. G 06 F 5И/02, 1979.

(руг. 7

23(Т1)

21

I I

KSn.3 О

(КГ VKtf)

17

гу О-

О

2f

& J2

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода вдВОичНО-дЕСяТичНый и дВОичНО-дЕСяТичНОгОВ дВОичНый | 1979 |

|

SU849197A1 |

| Преобразователь двоичного кода в двоично-десятичный и двоично-десятичного в двоичный | 1979 |

|

SU860051A1 |

| Преобразователь двоичного кодаВ дВОичНО-дЕСяТичНый | 1978 |

|

SU809150A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1042010A1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1982 |

|

SU1048469A1 |

| Устройство для преобразования двоичныхчиСЕл B дВОичНО-дЕСяТичНыЕ | 1979 |

|

SU809153A1 |

| Преобразователь двоичного кода в р-ичный позиционный код | 1983 |

|

SU1163479A1 |

| Преобразователь двоичных кодов в двоично-десятичные | 1984 |

|

SU1200428A1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1975 |

|

SU708344A1 |

| Устройство для преобразования избыточного двоичного кода в код со смешанным основанием | 1975 |

|

SU618737A1 |

25

/8

-5&

28

j;

KSJI.S (Кп) О

К5Л.9()

О

.9(nK2VnK3}

О

Е(

о

2Э

От5л.Э(ПК1УПК1{)

О

ч оОтЬл.З(ПР1УЛР)

О 3 О

От5л.Э{ПР2УПРЗ)

От 5л. 12

От 5л. S

& J

g, J5

7 JfiкЬл. 1

Авторы

Даты

1981-02-28—Публикация

1979-05-11—Подача