(Л

со

00

со

4 tsD

фиг. 7

Изобретение относится к вычислительной технике и может быть использовано при проектировании программируемых постоянных запоминающих устройств (ППЗУ).

Цель изобретения - повышение достоверности контроля устройства до его программирования.

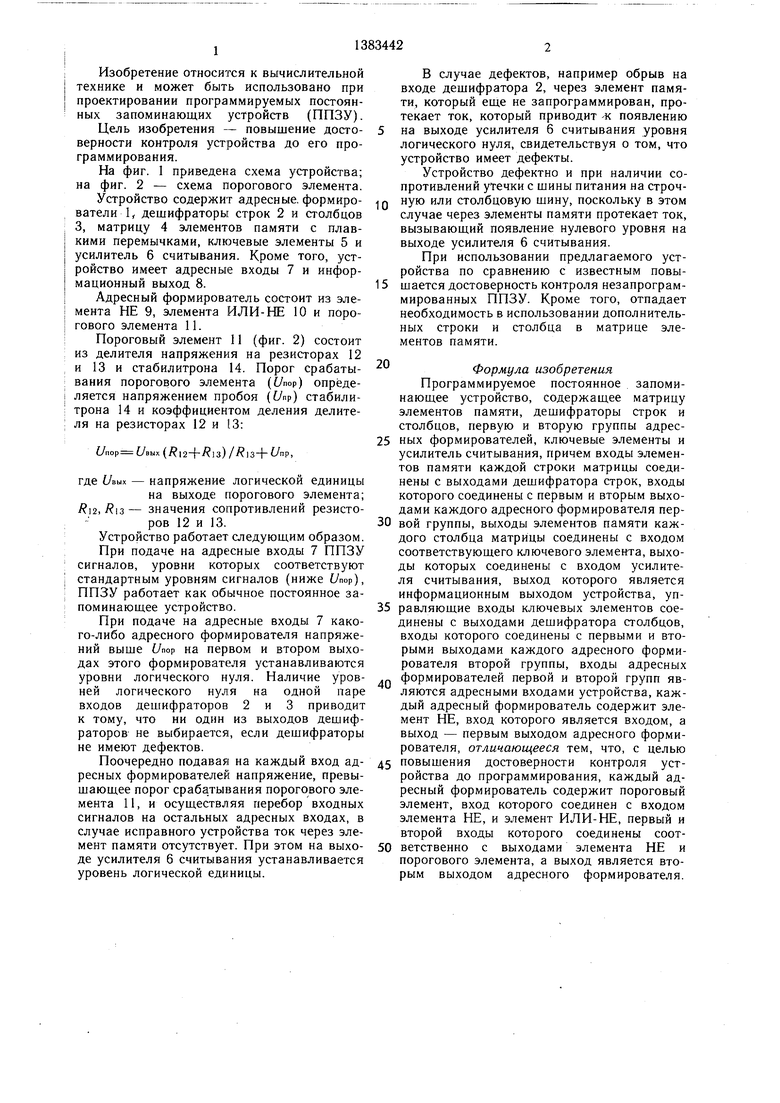

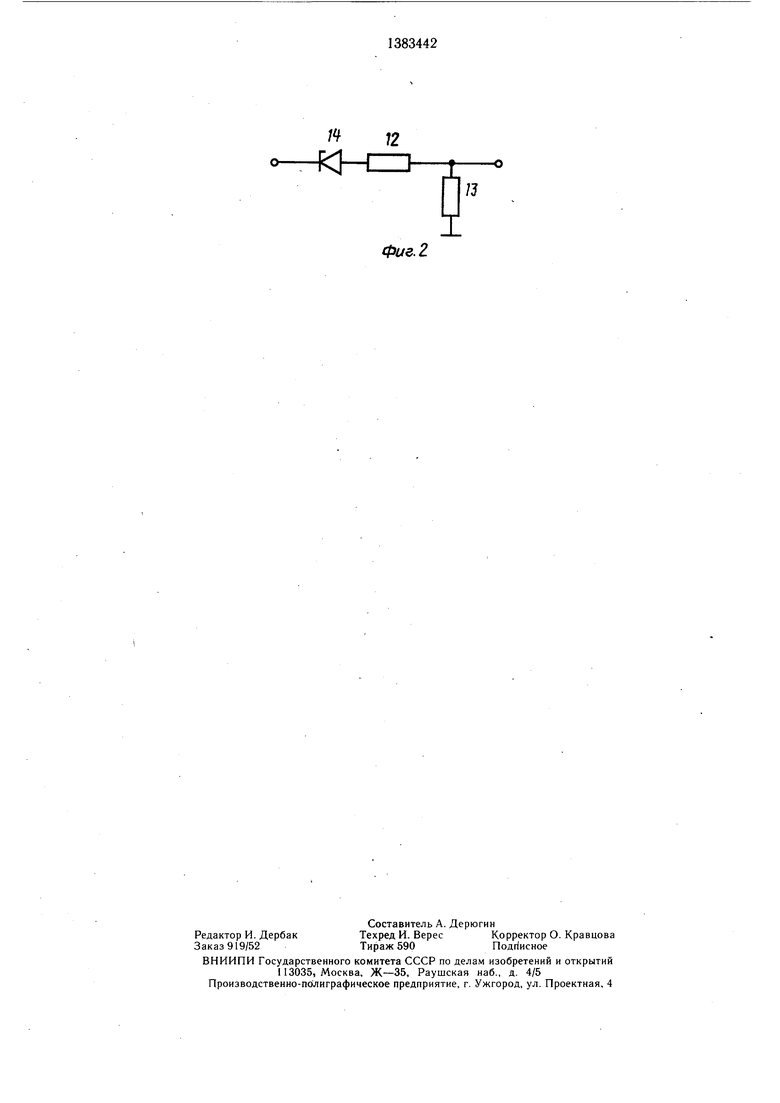

На фиг. 1 приведена схема устройства; на фиг. 2 - схема порогового элемента.

Устройство содержит адресные, формирователи 1, дешифраторы строк 2 и столбцов 3, матрицу 4 элементов памяти с плавкими перемычками, ключевые элементы 5 и усилитель 6 считывания. Кроме того, устройство имеет адресные входы 7 и информационный выход 8.

Адресный формирователь состоит из элемента НЕ 9, элемента ИЛ И-НЕ 10 и порогового элемента 11.

Пороговый элемент 11 (фиг. 2) состоит из делителя напряжения на резисторах 12 и 13 и стабилитрона 14. Порог срабатывания порогового элемента (t/nop) определяется напряжением пробоя (f/np) стабилитрона 14 и коэффициентом деления делителя на резисторах 12 и 1,3:

f/nop {yBb,x(,)// 13+0 np,

где t/вых - напряжение логической единицы на выходе порогового элемента; , Ri3 - значения сопротивлений резисторов 12 и 13.

Устройство работает следующим образом.

При подаче на адресные входы 7 ППЗУ сигналов, уровни которых соответствуют стандартным уровням сигналов (ниже L nop), ППЗУ работает как обычное постоянное запоминающее устройство.

При подаче на адресные входы 7 какого-либо адресного формирователя напряжений выше Unop на первом и втором выходах этого формирователя устанавливаются уровни логического нуля. Наличие уровней логического нуля на одной паре входов дешифраторов 2 и 3 приводит к тому, что ни один из выходов дешифраторов не выбирается, если дешифраторы не имеют дефектов.

Поочередно подавая на каждый вход адресных формирователей напряжение, превышающее порог срабатывания порогового элемента 11, и осуществляя перебор входных сигналов на остальных адресных входах, в случае исправного устройства ток через элемент памяти отсутствует. При этом на выходе усилителя 6 считывания устанавливается уровень логической единицы.

В случае дефектов, например обрыв на входе дешифратора 2, через элемент памяти, который еще не запрограммирован, протекает ток, который приводит -к появлению

на выходе усилителя 6 считывания уровня логического нуля, свидетельствуя о том, что устройство имеет дефекты.

Устройство дефектно и при наличии сопротивлений утечки с шины питания на строчную или столбцовую шину, ПОСКОЛЬКУ в этом случае через элементы памяти протекает ток, вызывающий появление нулевого уровня на выходе усилителя 6 считывания.

При использовании предлагаемого устройства по сравнению с известным повы5 шается достоверность контроля незапрограммированных ППЗУ. Кроме того, отпадает необходимость в использовании дополнительных строки и столбца в матрице элементов памяти.

Формула изобретения

Программируемое постоянное запоминающее устройство, содержащее матрицу элементов памяти, дешифраторы строк и столбцов, первую и вторую группы адрес5 ных формирователей, ключевые элементы и усилитель считывания, причем входы элементов памяти каждой строки матрицы соединены с выходами дешифратора строк, входы которого соединены с первым и вторым выходами каждого адресного формирователя пер0 вой группы, выходы элементов памяти каждого столбца матрицы соединены с входом соответствуюшего ключевого элемента, выходы которых соединены с входом усилителя считывания, выход которого является информационным выходом устройства, уп5 равляющие входы ключевых элементов соединены с выходами дешифратора столбцов, входы которого соединены с первыми и вторыми выходами каждого адресного формирователя второй группы, входы адресных

„ формирователей первой и второй групп являются адресными входами устройства, каждый адресный формирователь содержит элемент НЕ, вход которого является входом, а выход - первым выходом адресного формирователя, отличающееся тем, что, с целью

5 повышения достоверности контроля устройства до программирования, каждый адресный формирователь содержит пороговый элемент, вход которого соединен с входом элемента НЕ, и элемент ИЛ И-НЕ, первый и второй входы которого соединены соот0 ветственно с выходами элемента НЕ и порогового элемента, а выход является вторым выходом адресного формирователя.

П72

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| Репрограммируемое постоянное запоминающее устройство | 1989 |

|

SU1695384A1 |

| Постоянное запоминающее устройство | 1985 |

|

SU1288756A1 |

| Полупроводниковое запоминающее устройство | 1983 |

|

SU1142861A1 |

| Запоминающее устройство | 1986 |

|

SU1417036A1 |

| НАКОПИТЕЛЬ ИНФОРМАЦИИ И ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1987 |

|

SU1494785A1 |

| Перепрограммируемое постоянное запоминающее устройство | 1980 |

|

SU900316A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Резервированное запоминающее устройство с самоконтролем | 1982 |

|

SU1070609A1 |

| Постоянное запоминающее устройство с перезаписью информации | 1983 |

|

SU1278978A1 |

Изобретение относится к вычислительной технике и может быть использовано при проектировании программируемых постоянных запоминающих устройств. Целью изобретения является повышение достоверности контроля устройства до его программирования. Для достижения этой цели в состав каждого из адресных формирователей I устройства вводятся пороговый элемент 11 и элемент ИЛ И-НЕ 10. При подаче на один из адресных входов 7 напряжения выше порогового на первом и втором выходах адресного формирователя 1 устанавливаются низкие уровни. При этом ни один из выходов дешифраторов строк 2 или столбцов 3 не будет выбранным, если устройство не имеет дефектов. На выходе устройства в этом случае будет единичный уровень. В случае дефектов, например обрыва на входе дешифратора, соответствующий выход дешифратора будет выбранным, и на выходе устройства установится нулевой уровень. 2 ил.

Фиг. 2

| Микросхема бКО | |||

| Телефонная трансляция с местной цепью для уничтожения обратного действия микрофона | 1924 |

|

SU348A1 |

| Микросхема бКО | |||

| Телефонная трансляция с местной цепью для уничтожения обратного действия микрофона | 1924 |

|

SU348A1 |

Авторы

Даты

1988-03-23—Публикация

1986-06-17—Подача