СО 00

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам.

Цель изобретения - повышение надежности устройства.

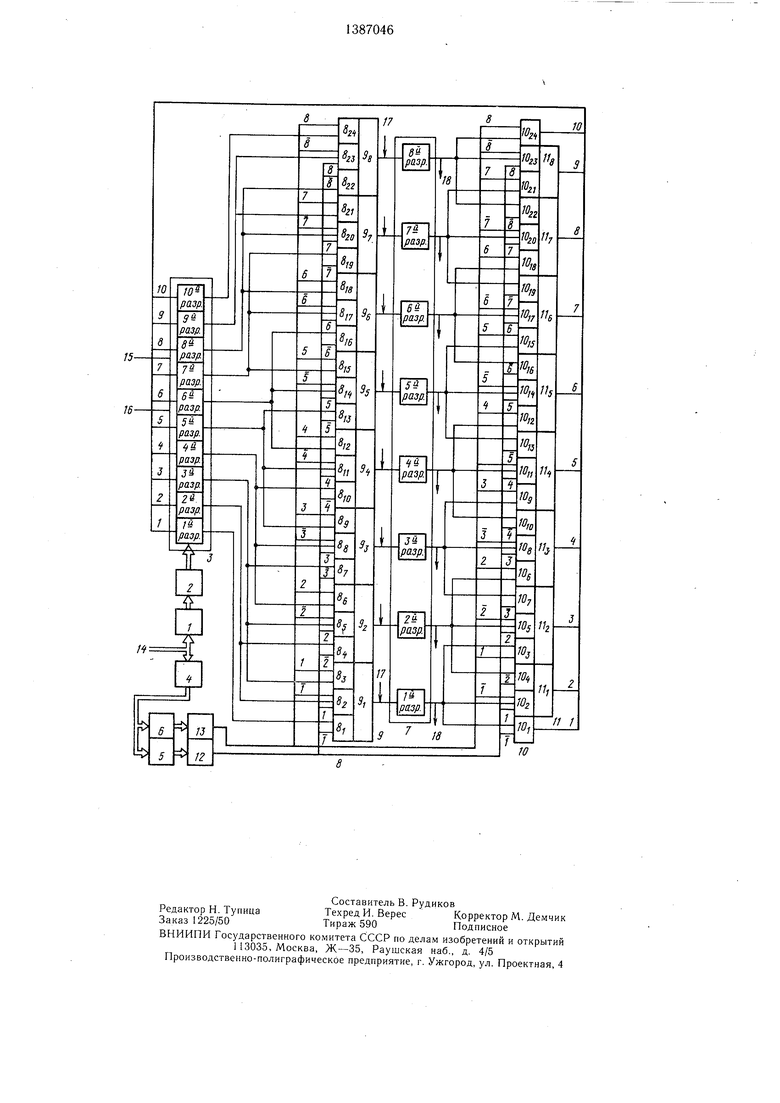

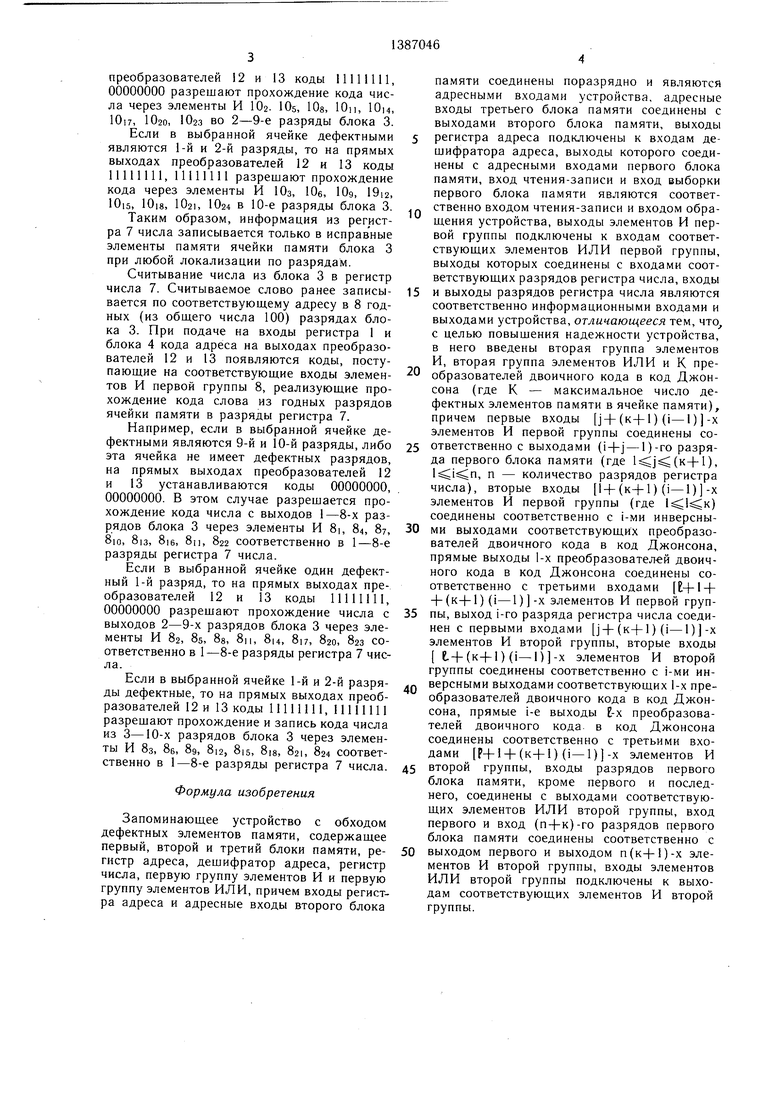

На чертеже изображена структурная схема запоминающего устройства с обходом дефектных элементов памяти.

Устройство содержит регистр 1 адреса, дещифратор 2 адреса, первый блок 3 памяти, имеющий (n-j-к)-разрядный накопитель (где п - число разрядов хранимых слов; к - максимально допустимое число дефектных элементов памяти в каждой ячейке памяти), второй блок 4 памяти, выполненный, например, в виде блока постоянной памяти и предназначенный для хранения адресов ячеек памяти, имеющих дефектные элементы памяти (разряды), второй блок

памяти, выполненный, например, в виде первого 5 и второго 6 блоков постоянной памяти, причем в блоке 5 хранятся номера разрядов с первым дефектом, в блоке 6 - с вторым дефектом (для случая, когда ). Устройство также содержит п-разрядный регистр 7 числа, первую группу 8 элементов И 81-824 (для случая, когда ), первую группу 9 элементов ИЛИ 9i-Эв, группу 10 элементов И lOi -1024, вторую группу 11 элементов ИЛИ lli - lie, первый 12 и второй 13 преобразователи двоичного кода в код Джонсона.

Устройство имеет адресные входы 14.

вход 15 записи-чтения, вход 16 обращения,

информационные входы 17 и выходы 18.

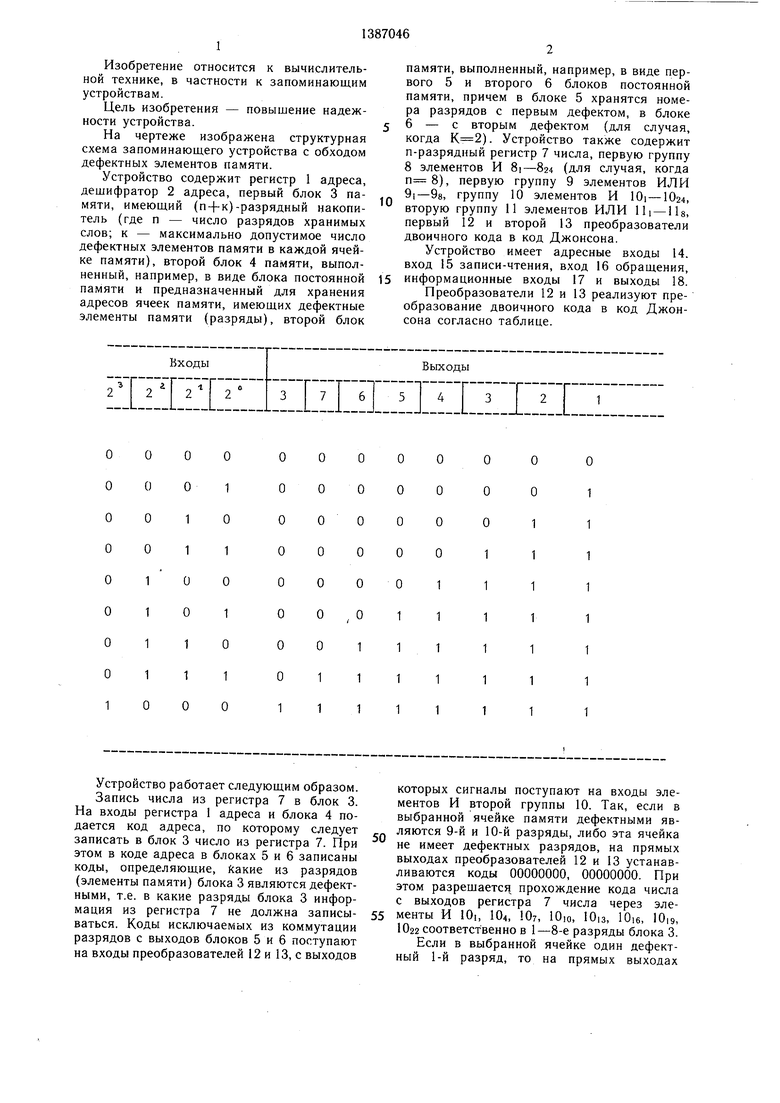

Преобразователи 12 и 13 реализуют преобразование двоичного кода в код Джонсона согласно таблице.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с обходом дефектных элементов памяти | 1986 |

|

SU1387047A1 |

| Устройство для управления обращением к памяти | 1985 |

|

SU1262494A1 |

| Запоминающее устройство с параллельным произвольным доступом к строкам и окнам данных | 1987 |

|

SU1499355A1 |

| ДАТЧИК СЛУЧАЙНЫХ ЧИСЕЛ С РАВНОМЕРНЫМ РАСПРЕДЕЛЕНИЕМ ПОВЫШЕННОЙ ТОЧНОСТИ | 1995 |

|

RU2103726C1 |

| Анализатор длительности выбросов и провалов напряжения | 1988 |

|

SU1674156A1 |

| Запоминающее устройство с частичным резервированием | 1986 |

|

SU1434503A1 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

| Функциональный преобразователь нескольких переменных | 1986 |

|

SU1387022A1 |

| Запоминающее устройство | 1985 |

|

SU1259336A2 |

| Ассоциативное оперативное запоминающее устройство | 1986 |

|

SU1363307A1 |

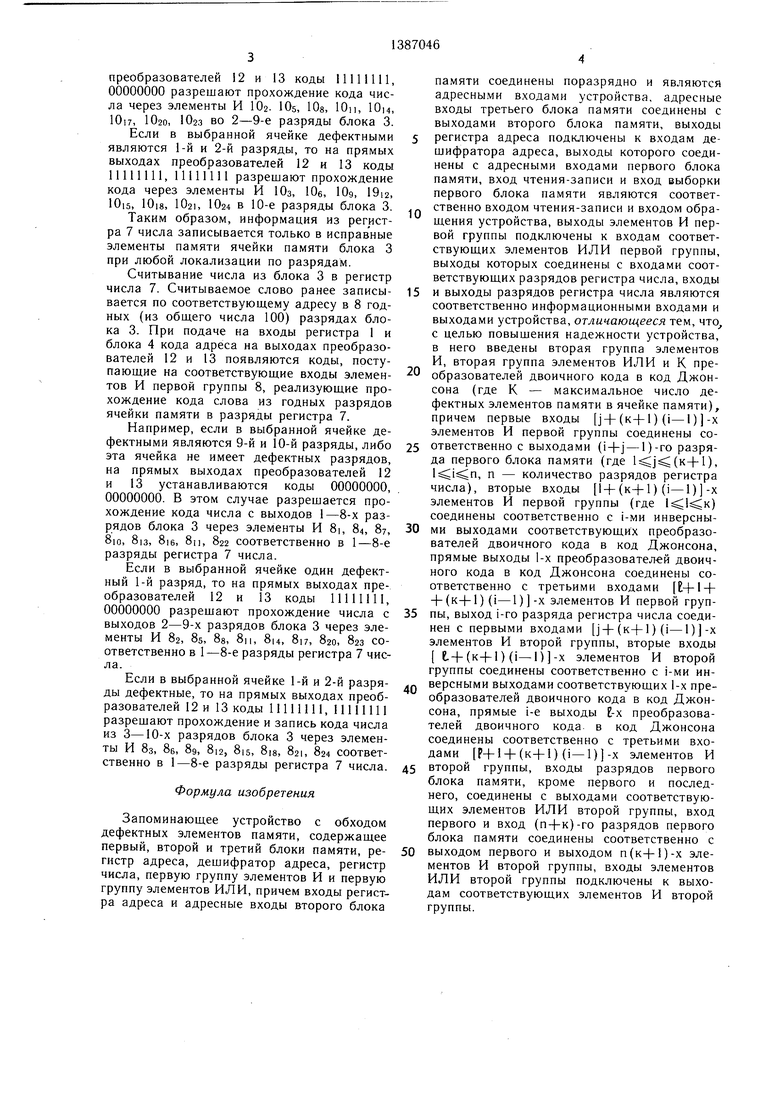

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам (ЗУ). Цель изобретения - повышение надежности устройства. Изобретение позволяет использовать ЗУ с дефектными элементами памяти, которые могут быть распределены во всех разрядах слов ячеек памяти блока памяти, при этом схема соединений не зависит от локализации дефектов. Устройство содержит блок памяти с избыточным количеством разрядов, три блока памяти, в которых хранятся коды адресов ячеек памяти и элементов памяти с дефектами, группы элементов И, элементов ИЛИ и преобразователи двоичного кода в код Джонсона, управляющие коммутацией разрядов блока памяти с избыточным количеством разрядов и регистра числа. Устройство также содержит регистр адреса и дешифратор адреса. 1 ил. 1 табл.

Устройство работает следующим образом.

Запись числа из регистра 7 в блок 3. На входы регистра 1 адреса и блока 4 подается код адреса, по которому следует записать в блок 3 число из регистра 7. При этом в коде адреса в блоках 5 и 6 записаны коды, определяющие, йакие из разрядов (элементы памяти) блока 3 являются дефектными, т.е. в какие разряды блока 3 информация из регистра 7 не должна записываться. Коды исключаемых из коммутации разрядов с выходов блоков 5 и 6 поступают на входы преобразователей 12 и 13, с выходов

0

5

которых сигналы поступают на входы элементов И второй группы 10. Так, если в выбранной ячейке памяти дефектными являются 9-й и 10-й разряды, либо эта ячейка не имеет дефектных разрядов, на прямых выходах преобразователей 12 и 13 устанавливаются коды 00000000, 00000000. При этом разрещается прохождение кода числа с выходов регистра 7 числа через элементы И 10|, 104, 107, lOio, 10|з, 10i6, 10|9, 1022 соответственно в 1-8-е разряды блока 3. Если в выбранной ячейке один дефектный 1-й разряд, то на прямых выходах

преобразователей 12 и 13 коды 11111111, 00000000 разрешают прохождение кода числа через элементы И 102- lOs, lOg, lOn, Юм, 10i7, 1020, Юзз во 2-9-е разряды блока 3.

Если в выбранной ячейке дефектными являются 1-й и 2-й разряды, то на прямых выходах преобразователей 12 и 13 коды 11111111, 11111111 разрешают прохождение кода через элементы И Юз, Юе, Юэ, 19i2, 10i5, 10i8, 1021, 1024 в Ю-е разряды блока 3.

Таким образом, информация из регистра 7 числа записывается только в исправные элементы памяти ячейки памяти блока 3 при любой локализации по разрядам.

Считывание числа из блока 3 в регистр числа 7. Считываемое слово ранее записывается по соответствуюш.ему адресу в 8 годных (из общего числа 100) разрядах блока 3. При подаче на входы регистра 1 и блока 4 кода адреса на выходах преобразователей 12 и 13 появляются коды, поступающие на соответствующие входы элементов И первой группы 8, реализующие прохождение кода слова из годных разрядов ячейки памяти в разряды регистра 7.

Например, если в выбранной ячейке дефектными являются 9-й и 10-й разряды, либо эта ячейка не имеет дефектных разрядов, на прямых выходах преобразователей 12 и 13 устанавливаются коды 00000000, 00000000. В этом случае разрешается прохождение кода числа с выходов 1-8-х разрядов блока 3 через элементы И 8i, 84, 87, 810, 8|з, 8i6, 811, 822 соответственно в 1-8-е разряды регистра 7 числа.

Если в выбранной ячейке один дефектный 1-й разряд, то на прямых выходах преобразователей 12 и 13 коды 11111111, 00000000 разрещают прохождение числа с выходов 2-9-х разрядов блока 3 через элементы И 82, 85, 88, 8||, 8|4, 8i7, 820, 823 соответственно в 1-8-е разряды регистра 7 числа.

Если в выбранной ячейке 1-й и 2-й разряды дефектные, то на прямых выходах преобразователей 12 и 13 коды 11111111, 11111111 разрещают прохождение и запись кода числа из 3-10-х разрядов блока 3 через элементы И 8з, 8б, 89, 8i2, 8i5, 8i8, 821, 824 соответственно в 1-8-е разряды регистра 7 числа.

Формула изобретения

Запоминающее устройство с обходом дефектных элементов памяти, содержащее первый, второй и третий блоки памяти, регистр адреса, дешифратор адреса, регистр числа, первую группу элементов И и первую группу элементов ИЛИ, причем входы регист.- ра адреса и адресные входы второго блока

памяти соединены поразрядно и являются адресными входами устройства, адресные входы третьего блока памяти соединены с выходами второго блока памяти, выходы

регистра адреса подключены к входам дешифратора адреса, выходы которого соединены с адресными входами первого блока памяти, вход чтения-записи и вход выборки первого блока памяти являются соответ ственно входом чтения-записи и входом обра0 JI л

щения устройства, выходы элементов И первой группы подключены к входам соответствующих элементов ИЛИ первой группы, выходы которых соединены с входами соответствующих разрядов регистра числа, входы

5 и выходы разрядов регистра числа являются соответственно информационными входами и выходами устройства, отличающееся тем, что с целью повыщения надежности устройства, в него введены вторая группа элементов И, вторая группа элементов ИЛИ и К пре0 образователей двоичного кода в код Джонсона (где К - максимальное число дефектных элементов памяти в ячейке памяти), причем первые входы j +(к+1) (i-1) -х элементов И первой группы соединены со5 ответственно с выходами (i+j-1)-го разряда первого блока памяти (где 1(к+1), , п - количество разрядов регистра числа), вторые входы 1-f-(к-f-l) (i-1)-х элементов И первой группы (где ) соединены соответственно с i-ми инверсны0 ми выходами соответствующих преобразователей двоичного кода в код Джонсона, прямые выходы 1-х преобразователей двоичного кода в код Джонсона соединены соответственно с третьими входами Е-+-1 + -|-(к-|-1)(1-1) -X элементов И первой груп5 пы, выход i-ro разряда регистра числа соединен с первыми входами + (к+1)(1-1)-х элементов И второй группы, вторые входы t4-(K+l)(i-1)-х элементов И второй группы соединены соответственно с i-ми инд версными выходами соответствующих 1-х преобразователей двоичного кода в код Джонсона, прямые i-e выходы 1-х преобразователей двоичного кода в код Джонсона соединены соответственно с третьими входами Р-|-1 +(K-fl) (i-1)-х элементов И

5 второй группы, входы разрядов первого блока памяти, кроме первого и последнего, соединены с выходами соответствующих элементов ИЛИ второй группы, вход первого и вход (п-4-к)-го разрядов первого блока памяти соединены соответственно с

0 выходом первого и выходом п(к+1)-х элементов И второй группы, входы элементов ИЛИ второй группы подключены к выходам соответствующих элементов И второй группы.

| Запоминающее устройство с коррекцией информации | 1980 |

|

SU907587A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Запоминающее устройство с коррекцией информации | 1985 |

|

SU1283861A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-04-07—Публикация

1986-10-09—Подача