1

Изобретение относится к запоминающим устройствам.

Известно запоминающее устройство с коррекцией информации, содержащее регистр числа, регистр адреса, дешифратор, многоразрядный накопитель и -блок коррекции информавди 1}.

Недостатком этого устройства является сложность блока коррекции информации.

Наиболее близким к предлагаемому техническим решением является запоминающее устройство с коррекцией информации, содержащее блок хранения кодов неисправных адресов и регистр адреса, который через дещифратор подключен к многоразрядному накопи-, телю на ферритовых сердечниках, состоящему из основного и дополнительного полей, входы/выходы которых подключены к регистру числа 2.

Недоста тком этого устройства является низкая надежность, обусловленная его сложностью и необходимостью иметь полиоразрядное дополнительное поле накопителя для полНОЙ перекоммутации дефектного слова независимо от количества дефектов в слове.

Цель изобретения - повыщение надежности устройства.

Поставленная цель достигается тем, что в запоминающее устройство с коррекцией информации, содержащее основной накопитель, регистр адреса, дешифратор адреса, регистр .числа и первый дополнительный накопитель, входы которого подключены к входам регистtoра адреса и являются входами устройства, причем входы дешифратора адреса соединены с выходами регистра адреса, а Bbixoj i с адресными входами основного накопителя, .выходы регистра числа подключены к одним

15 из И1{формационных входов основного накопителя, введены второй дополнительный накопитель, группы элементов И и элементы ИЛИ, причем входы второго дополнительного накопителя соединены с выводами .первого

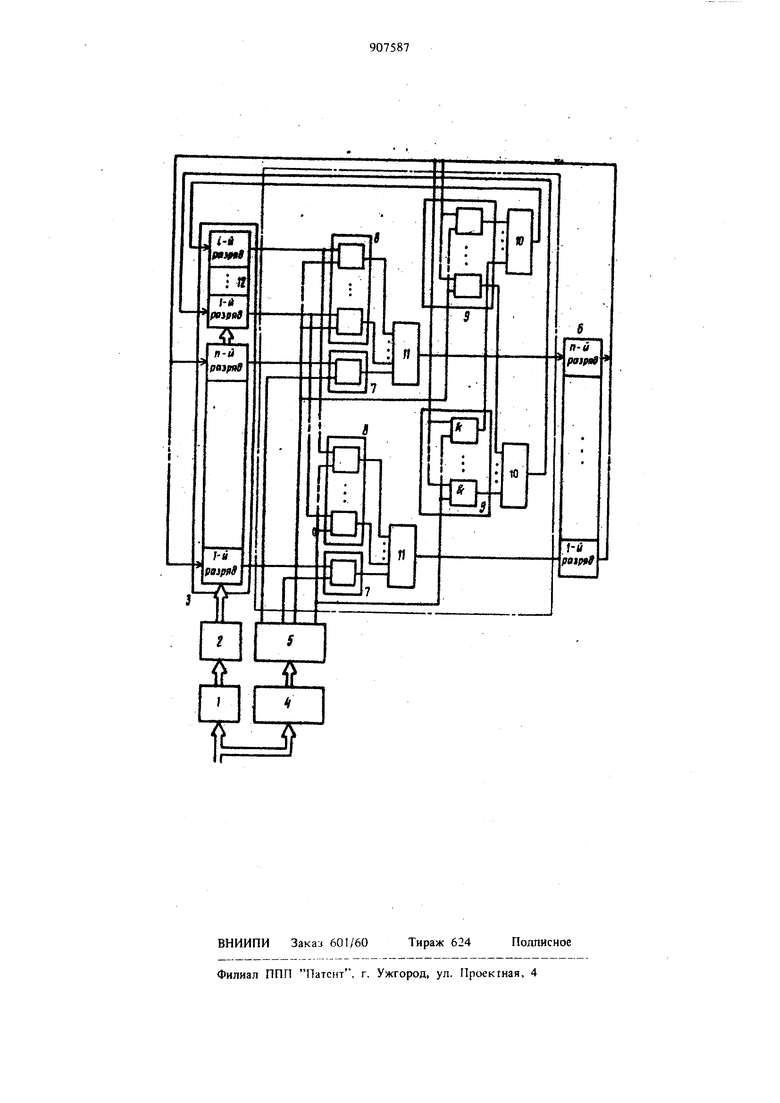

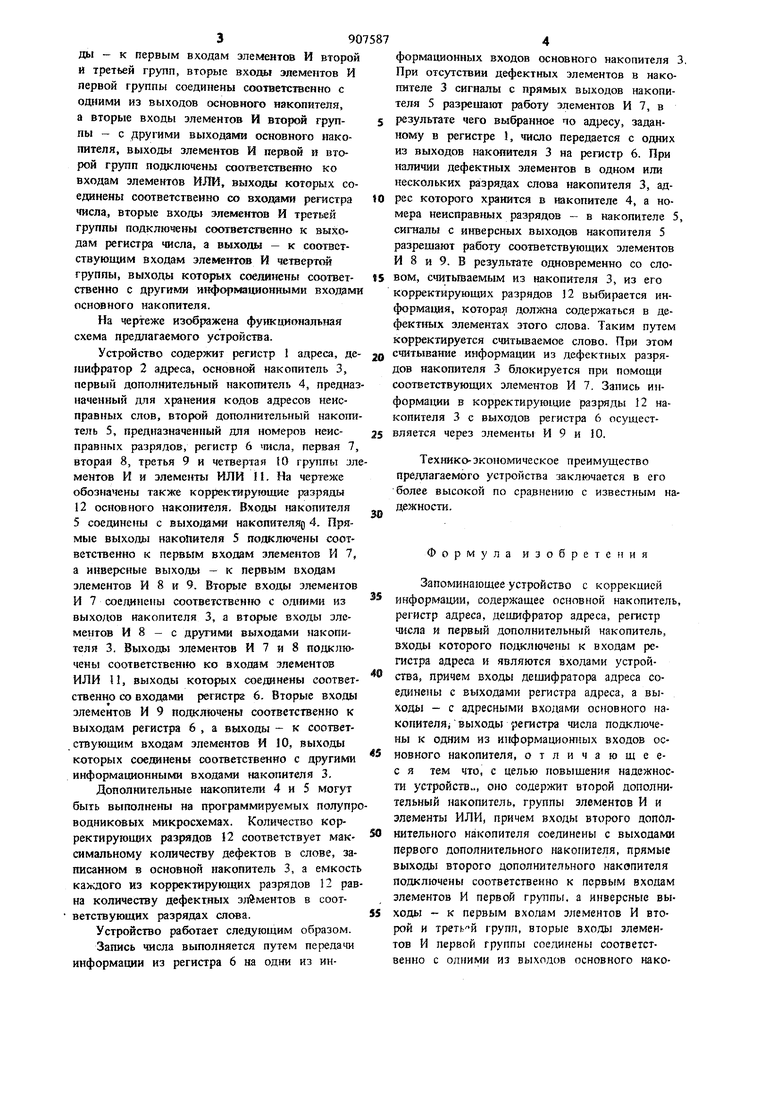

20 дополнительного накопителя, прямые выходы второго дополнительного накопителя подключены соответственно к первым входам элементов И первой группы, а инверсные выхо390ды - к первым входам элементов И второй и третьей грулп, вторые входы элементов И первой группы соединены соответственно с одними из выходов основного накопителя, а вторые входы элементов И второй грунпы - с другими выходами основного накопителя, выходы элементов И первой и второй групп подключены соответствешю ко входам элементов ИЛИ, выходы которых соединены соответственно со входами регистра числа, вторые входь элементов И третьей группы подключены соответственно к выходам регистра числа, а выходы - к соответствующим входам элементов И четвертой группы, выходы KOTOjHjx соединены соответственно с другими информационными входами осисданого накопителя. На чертеже изображена функциональная схема предлагаемого устройства. Устройство содержит регистр адреса, дешифратор 2 адреса, основной накопитель 3, первый дополнительный накопитель 4, предназ наченный для хранения кодов адресов неисправных слов, второй дополнительный накопитель 5, предназначенный для номеров неиснравных разрядов, регистр 6 тсла, первая 7, вторая 8, третья 9 и четвертая 10 группы эле ментов И и элементы ИЛИ 11, На чертеже обозначены также корректирующие разряды 12 основного накопителя. Входы шкопителя 5 соединены с выходами накопителяд 4. Прямые выходы накопителя 5 подаслючены соответственно к первым входам злеме1{тов И 7, а инверсные выходы - к первым входам элементов И 8 и 9. Вторые входы элементов И 7 соединены соответственно с одними из выходов накопителя 3, а вторые входы элементов И 8 - с другил выходами накопителя 3. Выходы элементов И 7 и 8 подключены соответствен ю ко входам элементов ИЛИ П, выходы которых соединены соответственно со входами регистра 6. Вторые входы элементов И 9 пода:лючены соответственно к выходам регистра 6 , а выходы - к соответствующим входам элементов И 10, выходы которых соеданены соответственно с другими информационными входами накопителя 3. Дополнительные накопители 4 и 5 могут быть выполнены на программируемых полупр водниковых микросхемах. Количество корректирующих разрядов 12 соответствует максимальному количеству дефектов в слове, записанном в основной накопитель 3, а емкость каждого из корректирующих разрядов 12 рав на количеству дефектных элементов в соответствующих разрядах слова. Устройство работает следующим образом. Запись числа выполняется путем передачи информации из регистра 6 на одни из информационных входов основного накопителя 3. При отсутствии дефектных элементов в накопителе 3 сигналы с прямых выходов накопителя 5 разрешают работу элементов И 7, в результате чего выбранное по адресу, заданному в регистре 1, число передается с одних из выходов накопителя 3 на регистр 6. При наличии дефектных элементов в одном или нескольких разрядах слова накопителя 3, адрес которого хранится в накопителе 4, а номера неисправных разрядов - в накопителе 5, сигналы с инверсных выходов накопителя 5 разрешают работу соответствующих элементов И В и 9. В результате одновременно со словом, считываемым из накопителя 3, из его корректирующих разрядов 12 выбирается информация, которая должна содержаться в дефектных элементах этого слова. Таким путем корректируется считываемое слово. При этом считывание информации из дефектных разрядов накопителя 3 блокируется при помощи соответствующих элементов И 7. Запись информации в корректирующие разряды 12 накопителя 3 с выходов регистра 6 осуществляется через элементы И 9 и 10. Технико-экономическое преимущество предлагаемого устройства заключается в его более высокой по сравнению с известным надежности. Формула изобретения Запоминающее устройство с коррекцией информации, содержащее основной накопитель, регистр адреса, дещифратор адреса, регистр числа и первый дополнительный накопитель, входы которого подключены к входам регистра адреса и являются входами устройства, причем входы дешифратора адреса соединены с выходами регистра адреса, а выходь - с адресными входами основного накопителя; выходы регистра числа подключены к одним из ипформационных входов основного накопителя, отличающеес я тем что, с целью повыщения надежности устройств.., оно содержит второй дополнительный накопитель, группы элементов И и элементы ИЛИ, причем входы второго дополнительного накопителя соединены с выходами первого дополнительного накопителя, прямые выходы второго дополнительного накопителя подключены соответственно к первым входам элементов И первой группьг. а инверсные выходы - к первым входам элементов И второй и треть й групп, вторые входы элементов И первой группы соединены соответственно с одними из выходов основного накояителя. а вторые входь элементов И второй группы - с другими выходами основного накопителя, выходы элементов И первой и второй групп подключены соответственно ко входам элементов ИЛИ, выходы которых соединены соответственно со входами регистра числа, вторые входы элементов И третьей группы подключены соответственно к выходам регистра числа, а выходы - к соответствующим входам элементов И четвертой группы, выходы которых соединешя соответственно с другими информационными входами основного накопителя.

Источники информации, принятые во внимание при жспертнзе , 1. Авторское свидетельство СССР № 492935,

кл. G 11 С 29/00, 1976.

2. Чахоян Л. М. Емкость дополнительного поля накопителя оперативного запоминаницего устройства с блокировкой неисправных адре сов.- Вопросы радиоэлектроники, сер. ЭВТ, вып. 6, 1969 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1982 |

|

SU1084903A1 |

| Запоминающее устройство с коррекцией информации | 1985 |

|

SU1283861A1 |

| Запоминающее устройство с частичным резервированием | 1986 |

|

SU1434503A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU970480A1 |

| Запоминающее устройство с обходом дефектных элементов памяти | 1986 |

|

SU1387046A1 |

| Запоминающее устройство с блокировкой неисправных ячеек | 1983 |

|

SU1115108A1 |

| Запоминающее устройство с обходом дефектных элементов памяти | 1986 |

|

SU1387047A1 |

| Оперативное запоминающее устройство с коррекцией ошибок | 1987 |

|

SU1539844A1 |

| Постоянное запоминающее устройство | 1977 |

|

SU834768A1 |

| Запоминающее устройство с обнаружением и коррекцией ошибок | 1983 |

|

SU1138836A1 |

Авторы

Даты

1982-02-23—Публикация

1980-06-18—Подача