1

(21)4691641/24; 4692516/24

(22)J7.05.89

(46) 07.05.91. Бюл. № 17 (7) Ленинградский электротехнический институт им. В.И.Ульянова (Ленина)

(72) АоСоКалендарев, В0П.Крюков, И.Ю.Матвеев, Д.В«Пузанков и И.Б Шапиро

(53)681.325(088.8)

(56)Авторское свидетельство СССР 966694, кл0 G 06 F 9/22, 1980.

Авторское свидетельство СССР 1411743, кл. G 06 F 9/22, 11/00, 1987.

(54)МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ С КОНТРОЛЕМ

(57)Изобретение относится к вычислительной технике и может быть использовано для построения микропрограмми- руемых микропроцессорных систем. Целью изобретения является повышение

достоверности функционирования устройства за счет обеспечения возможности самоконтроля„ Поставленная цель достигается тем, что в микропрограммное устройство управления контролем, содержащее блок памяти, регистр микрокоманд, узел формирования адреса, сигнатурный анализатор, схему сравнения, введены регистр эта лонной сигнатуры, с первого по третий элементы И, первый и второй элементы НЕ, первый и второй мультиплексоры о Благодаря введенным аппаратным средствам в устройстве обеспечиваются возможность снятия с выходов устройства значений сформированных сигнатур для последующего анализа; анализ признака ошибки к изменения хода микропрограммы по результатам анализа; возможность использования микропрограммной памяти вместо ПЛМ в качестве преобразователя эталонных сигнатур. 4 ил.

§

|СЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления с контролем переходов | 1987 |

|

SU1411743A1 |

| Микропрограммное устройство управления с самоконтролем | 1987 |

|

SU1427367A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1539782A2 |

| Устройство для диагностики неисправностей цифровых узлов | 1987 |

|

SU1481773A1 |

| Сигнатурный анализатор | 1986 |

|

SU1357961A1 |

| Устройство для контроля хода микропрограмм | 1988 |

|

SU1661772A1 |

| Устройство для контроля и диагностики цифровых блоков | 1986 |

|

SU1388871A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1262500A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1545222A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения мнкропрограм- мируемых микропроцессорных систем.

Целью изобретения является повышение достоверности функционирования устройства за счет обеспечения возможности самоконтроля

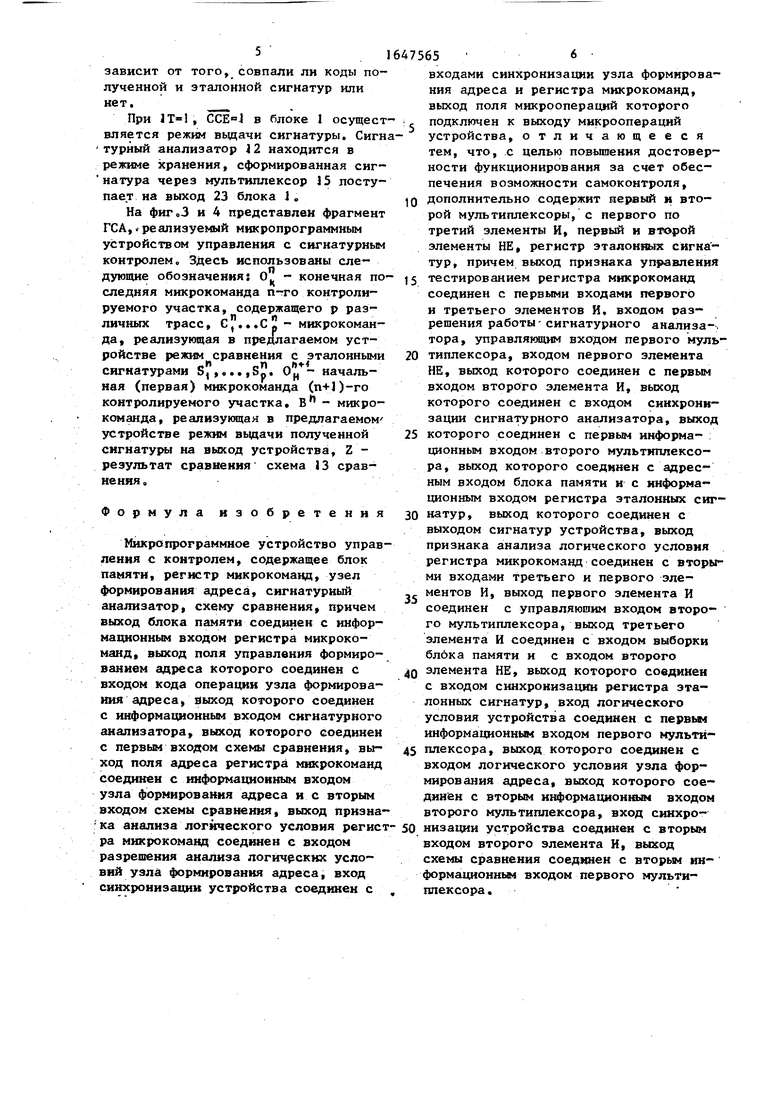

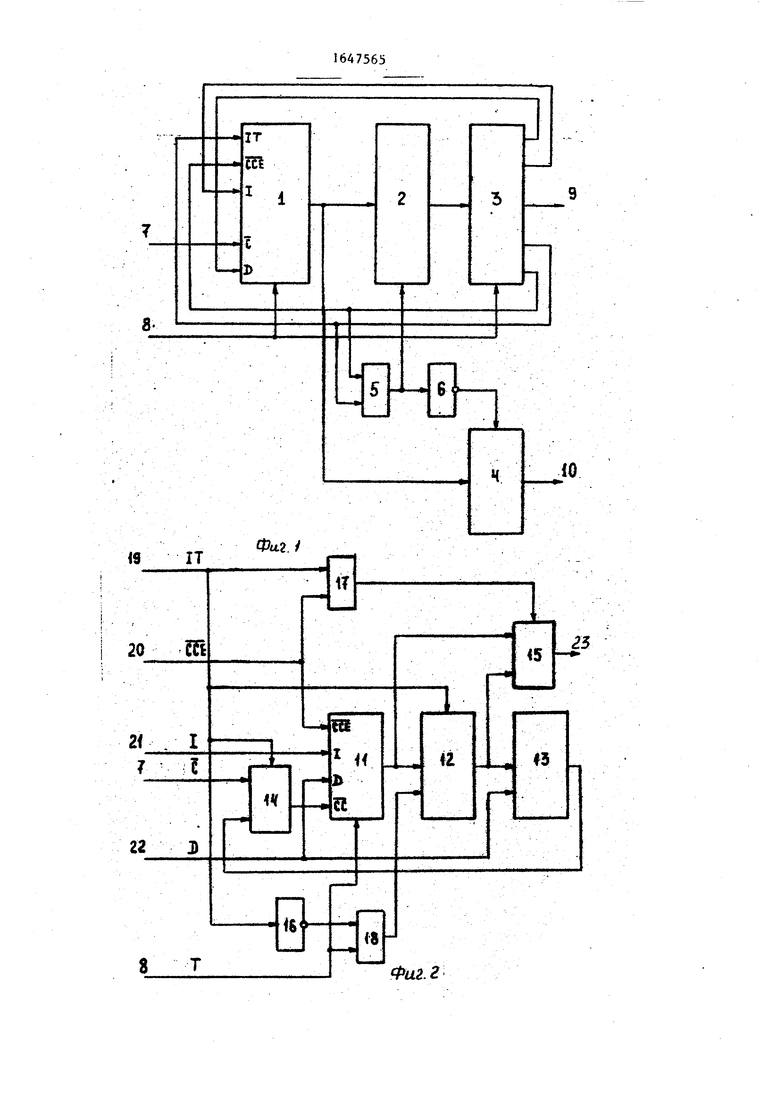

На фиг Л представлена функциональная схема устройства; на фиг.2 - функциональная схема блока формирования адресов; на фиг03 и 4 - примеры фрагментов граф-схем алгоритмов

(ГСА) микропрограмм реализуемых устройством

Микропрограммное устройство управления с сигнатурным контролем (фиг.I) содержит блок 1 формирования адреса, блок 2 памяти, регистр 3 микро команд, регистр 4 эталонной сигнатуры, третий элемент И 5, второй элемент НЕ 6, вход 7 кода условия устройства, вход 8 синхронизации устройства, выход 9 микроопераций регистра 3 микрокоманд, выход 10 сигнатуры регистра 4 эталонной сигнатуры.

& Ј

$

СП

б

СП

3164

Блок формирования адреса (фиг.2) содержит узел II формирования адреса, сигнатурный анализатор 12, схему 13 сравнения, первый и второй мульти- плексоры 14 и 15, первый элемент НЕ 16, первый и второй элементы И 37 и 18, кроме того, на фиг.2 обозначены: выход J9 управления тестированием и выход 20, . признак анализа логи-1 чег.кого условия регистра микрокоманд, вьпсод 2J поля кода инструкции регнст- ji мякрокоманд, выход 22 поля адреса регистра микрокоманд, выход 23 адреса блока формирования адреса.

Фрагменты ГСА (фиг.З, 4) содержат операторные, условные и конечные вершины.

Устройство работает следующим образом.

Условные переходы при могут быть осуществлены по значению признака на входе 7 устройства Его различ- ным значениям соответствуют различные трассы контролируемого участка микро- программы Код, выработанный на выходе блока I формирования адресов, по ступает на адресный вход блока 2 памяти, из которого при наличии сигнала выборки кристалла осуществляется счк- тывание очередной микрокоманды (МК)« Прк запрете считывания из блока 2 памяти на вход разрешения регистра 4 эталонной сигнатуры поступает сигнал, который разрешает запксь кода с выхо да блока 1 в регистр 4 эталонной сигнатуры. Таким образом, в режиме выдачи сигнатуры в регистр 4 записывается значение сигнатуры на заданном контролируемом участке С выхода 10 сигнатура может быть считана для ана лиза пользователем,,

Узел 11 формирования адреса выполняет функцию формирования адресов микрокоманд. Код адреса следующей микрокоманды вырабатывается на выходе узла 11 формирования адреса и через мультиплексор 5 поступает на выход 23 блока 1.

В качестве узла И может быть использована БИС К1804ВУ4.

Сигнатурный анализатор J 2 работает по параллельному принципу действия и содержит поразрядные триггеры и сумаматоры по модулю два, а также сумматоры яо модулю два в цепи обратной связи. Сигнатурный анализатор предназначен для получения сигнатур

о п

5

5

0

5

последовательности адресов, формкруе- мых на выходе узла 41

Работа блока 4 формирования адреса осуществляется следующим образом. При переходе значения сигнала IT из единицы в ноль, сигнатурный анализатор 12 устанавливается в начальное состояние (например, в единичное). По фронту синхроимпульса Г в узле И начинает вырабатываться адрес следующей микрокоманды, который поступает на информационный вход сигнатурного анализатора 12 и на вход мультиплексора 15. В случае синхроимпульс проходит через элемент И J8 на вход синхронизации сигнатур- кого анализатора, который срабатывает по срезу синхроимпульса. Таким образом s при ,, в сигнатурном анализаторе 12 осуществляется свертка кодов адресов МК„ вырабатываемых на выходе узла 14, коды адреса через мультиплексор 15 поступают на выход 23 блока формирования адреса Условные переходы при осуществляются по значению признака на входе 7 блока 1, Их различным.значениям соответствуют различные трассы контролируемого участка микропрограммы, а следовательно, различные сигнатуры контролируемого участка, формируемые в сигнатурном анализаторе 12„ Каждой кз возможных трасс соответствует своя эталонная сигнатура Spo Здесь п - номер контролируемого участка микропрограммы, р - номер трассы контролируемого участка,, При , в блоке I осуществляется режим сравнения полученной сигнатуры с эталонной. В этом случае сигнатурный анализатор 12 переходит в режим хранения полученной на предыдущем такте сигнатуры (поскольку синхроимпульс на его синхровход не проходит). На вход 21 блока J подается код инструкции второго типа, при которой на вход 22 блока подается код эталонной сигнатуры. Значение эталонной сигнатуры поступает да второй вход схемы 13 сравнения и сравнивается с находящимся на первом входе кодом сигнатуры, сформированным в сигнатурном анализаторе 12, Результат сравнения определяет направление ветвления из текущей микрокоманды - код адреса следующей микрокоманды на выходе 23. Таким образом, в режиме сравнения код адреса следующей микрокоманды

зависит от того, совпали ли коды полученной и эталонной сигнатур или нет.

При JT-1, в блоке 1 осуществляется режим выдачи сигнатуры. Сигнтурный анализатор I2 находится в режиме хранения, сформированная сиг- 1 натура через мультиплексор 15 поступает на выход 23 блока J„

На фиг03 и 4 представлен фрагмент ГСА, реализуемый микропрограммным устройством управления с сигнатурным контролем. Здесь использованы следующие обозначения: о - конечная последняя микрокоманда n-го контролируемого участка, содержащего р различных трасс, С,...Ср - микрокоманда, реализующая в предлагаемом устройстве режим сравнения с эталонными

«и п Л

сигнатурами S,,...,Sp. OH - начальная (первая) микрокоманда (п+1)го контролируемого участка. - микрокоманда, реализующая в предлагаемом устройстве режим вьщачи полученной сигнатуры на выход устройства, Z - результат сравнения схема 13 сравнения.

Формула изобретения

Микропрограммное устройство управления с контролем, содержащее блок памяти, регистр микрокоманд, узел формирования адреса, сигнатурный анализатор, схему сравнения, причем выход блока памяти соединен с информационным входом регистра микрокоманд, выход поля управления формированием адреса которого соединен с входом кода операции узла формирования адреса, выход которого соединен с информационным входом сигнатурного анализатора, выход которого соединен с первым входом схемы сравнения, выход поля адреса регистра микрокоманд соединен с информационным входом узла формирования адреса и с вторым входом схемы сравнения, выход приэна ка анализа логического условия регист- 50 низации устройства соединен с вторым ра микрокоманд соединен с входом входом второго элемента И, выход разрешения анализа логических уело- схемы сравнения соединен с вторым ин- вий узла формирования адреса, вход формационным входом первого мульти- синхрониэации устройства соединен с плексора.

5

0

5

0

входами синхронизации узла формирования адреса и регистра микрокоманд, выход поля микроопераций которого подключен к выходу микроопераций устройства, отличающееся тем, что, с целью повышения достоверности функционирования за счет обеспечения возможности самоконтроля, дополнительно содержит первый и второй мультиплексоры, с первого по третий элементы И, первый и второй элементы НЕ, регистр эталонных сигнатур, причем выход признака управления тестированием регистра микрокоманд соединен с первыми входами первого и третьего элементов И, входом разрешения работы-сигнатурного анализатора, управляющим входом первого мультиплексора, входом первого элемента НЕ, выход которого соединен с первым входом второго элемента И, выход которого соединен с входом синхронизации сигнатурного анализатора, выход которого соединен с первым информационным входом второго мультиплексора, выход которого соединен с адресным входом блока памяти и с информационным входом регистра эталонных сигнатур, выход которого соединен с выходом сигнатур устройства, выход признака анализа логического условия регистра микрокоманд соединен с вторыми входами третьего и первого элементов И, выход первого элемента И соединен с управляюшим входом второго мультиплексора, выход третьего элемента И соединен с входом выборки блока памяти и с входом второго элемента НЕ, выход которого соединен с входом синхронизации регистра эталонных сигнатур, вход логического условия устройства соединен с первым информационным входом первого мульти- 5 плексора, выход которого соединен с входом логического условия узла формирования адреса, выход которого соединен с вторым информационным входом второго мультиплексора, вход синхро5

0

IT Ш I

I

D

Фа i

m.

Авторы

Даты

1991-05-07—Публикация

1989-05-17—Подача