Изобретение относится к вычислительной технике и може;т быть исполь- аовано в системах преобразования и Передачи информации.

: Цель изобретения - расширение об- л|асти применения за счет дополнитель Його преобразования двухполярного входного сигнала в цифровое произ Ведение этого сигнала на его прира- 11(ения.

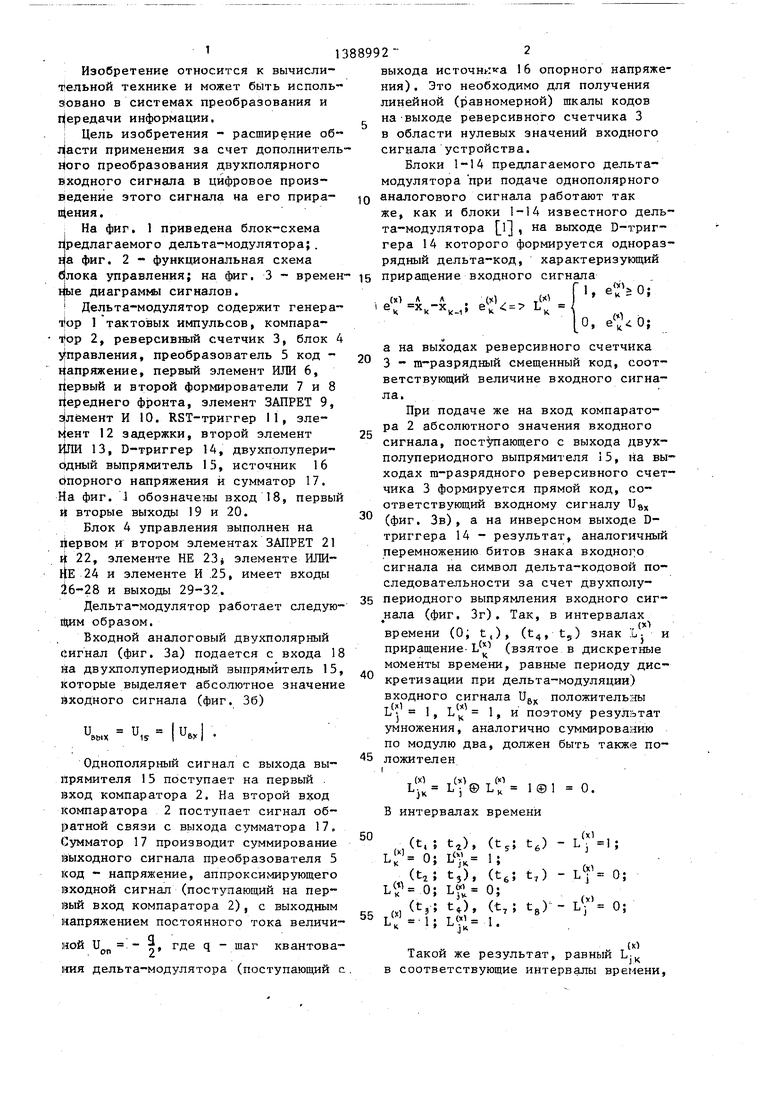

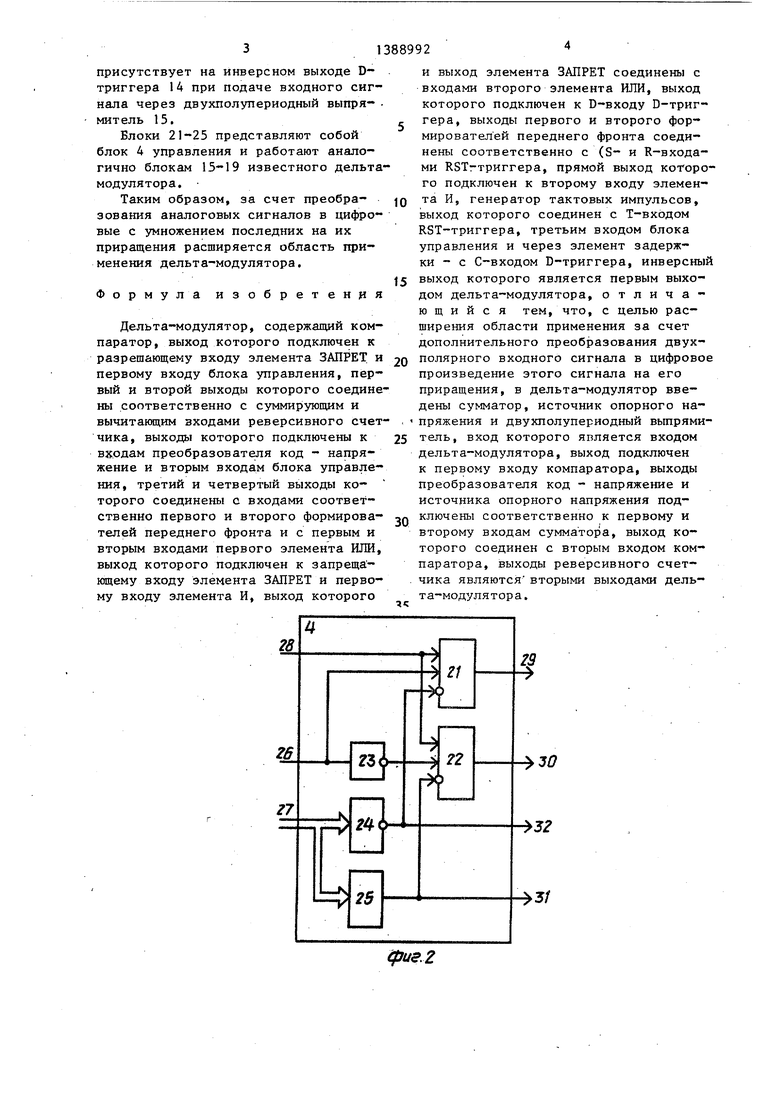

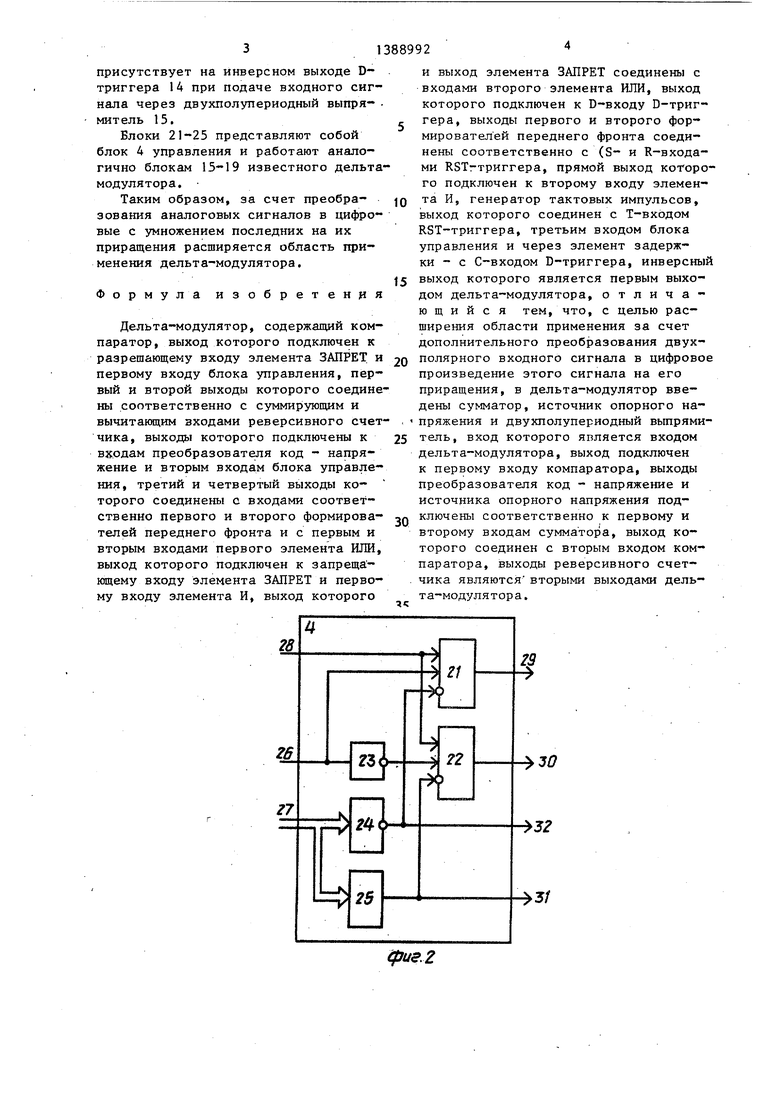

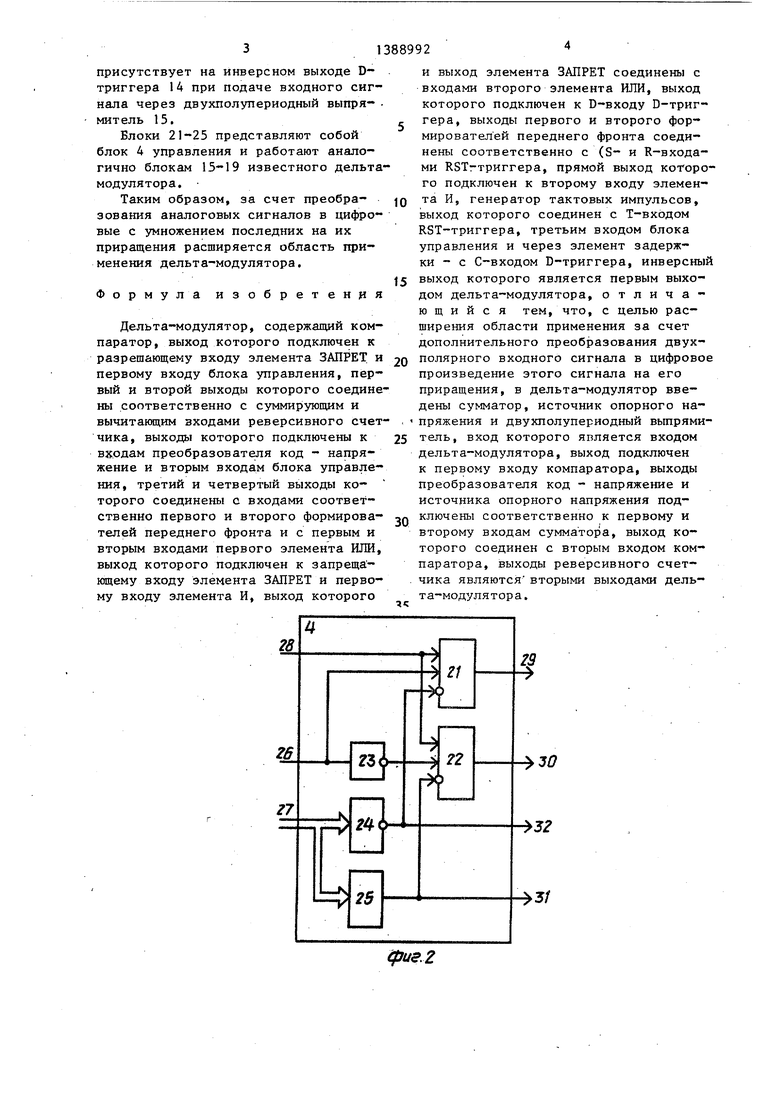

, На фиг. 1 приведена блок-схема предлагаемого дельта-модулятора;. на фиг. 2 функциональная схема блока управления; на фиг. 3 - времен ные диаграммы сигналов.

I Дельта-модулятор содержит генера- TJop 1 тактовых импульсов, компара- TJop 2, реверсивный счетчик 3, блок 4 у правления, преобразователь 5 код - напряжение, первый элемент ИЛИ 6, гервый и второй формирователи 7 и 8 гереднего фронта, элемент ЗАПРЕТ 9, элемент И 10. RST-триггер 11, элемент 12 задержки, второй элемент ИЛИ 13, D-триггер 1А, двухполупери- Одный выпрямитель 15, источник 16 Опорного напряжения и сумматор 17. На фиг. I обозначены вход 18, первый И вторые выходы 19 и 20.

Блок 4 управления выполнен на Йервом и втором элементах ЗАПРЕТ 21

:22, элементе НЕ 23j элементе ИЛИ- Е 24 и элементе И .25, имеет входы i6-28 и выходы 29-32.

Дельта-модулятор работает следующим образом.

Входной аналоговый двухполярный Сигнал (фиг. За) подается с входа 18 на двухполупериодный выпрямитель 15, которые выделяет абсолютное значение Входного сигнала (фиг. 36)

i

и.ь.х и,

и.

Однополярный сигнал с выхода выпрямителя 15 поступает на первый . вход компаратора 2. На второй вход компаратора 2 поступает сигнал обратной связи с выхода сумматора 17. Сумматор 17 производит суммирование Выходного сигнала преобразователя 5 код - напряжение, аппроксимирующего входной сигнал (поступающий на первый вход компаратора 2), с выходным напряжением постоянного тока величиной и

- 2

on9 - шаг квантоваlfraя дельта-модулятора (поступающий с

выхода источника 16 опорного напряжения) . Это необходимо для получения линейной (равномерной) шкапы кодов на -выходе реверсивного счетчика 3 в области нулевых значений входного сигнала устройства.

Блоки 1-14 предлагаемого дельта- модулятора при подаче однополярного

аналогового сигнала работают так

же, как и блоки 1-14 известного дельта-модулятора 1 , на выходе D-триг- гера 14 которого формируется одноразрядный дельта-код, характеризующий

5 приращение входного сигнала

i е

. 4, -.

,()

.W

V р /- Т ц к-1 к - к

1. еГгО; о,

0

5

а на выходах реверсивного счетчика 3 - т-разрядный смещенный код, соответствующий величине входного сигнала.

При подаче же на вход компаратора 2 абсолютного значения входного сигнала, поступающего с выхода двух- полупериодного выпрямителя 15, на выходах т-разрядного реверсивного счетчика 3 формируется прямой код, соответствующий входному сигналу (фиг. Зв), а на инверсном выходе D- триггера 14 - результат, аналогичный перемножению битов знака входного сигнала на символ дельта-кодовой последовательности за счет двухполу- 5 периодного выпрямления входного сигнала (фиг. Зг). Так, в интервалах (

времени (0; t,), (14, tj) знак L, и

приращение-L J (взятое в дискретные моменты времени, равные периоду дискретизации при дельта-модуляции)

входного сигнала Ug.. положитель: 1ы г(М „ , тМ-

L. 1, L 1, и поэтому результат умножения, аналогично суммированию по модулю два, должен быть также по- 5 ложителен

;: ь7©ьГ 1©1 0.

в интервалах времени ° (t, ; t), (t,; tj - ь7 1;

(XT

т Г), rW 1 . L - и, Ь 1 ,

(ti; t,), ( tj - L4 0; Li 0; 0;

5,(.

K - Ь 1.

Такой же результат, равный L

W

JK

в соответствующие интервалы времени.

присутствует на инверсном выходе D триггера 14 при подаче входного сигнала через двухполупериодный выпря- митель 15.

Блоки представляют собой блок 4 управления и работают аналогично блокам 15-19 известного дельта- модулятора,

Таким образом, за счет преобразования аналоговых сигналов в цифровые с умножением последних на их приращения расширяется область применения дельта-модулятора.

Формула изобретения

Дельта-модулятор, содержащий компаратор, выход которого подключен к

и выход элемента ЗАПРЕТ соединены с входами второго элемента ИЛИ, выход которого подключен к D-входу D-триг- гера, выходы первого и второго фор- мировател ей переднего фронта соединены соответственно с (S- и R-входами КЗТгтриггера, прямой выход которого подключен к второму входу элемен 0 та И, генератор тактовых импульсов, выход которого соединен с Т-входом RST-триггера, третьим входом блока управления и через элемент задержки - с С-входом D-триггера, инверсный

5 выход которого является первым выходом дельта-модулятора, отличающийся тем, что, с целью расширения области применения за счет дополнительного преобразования двухразрешающему входу элемента ЗАПРЕТ и 20 полярного входного сигнала в цифровое

первому входу блока управления, первый и второй выходы которого соединены соответственно с суммирующим и вычитающим входами реверсивного счетчика, выходы которого подключены к входам преобразователя код - напряжение и вторым входам блока управления, третий и четвертый выходы которого соединены с входами соответственно первого и второго формирователей переднего фронта и с первым и вторым входами первого элемента ИЛИ, выход которого подключен к запрещающему входу элемента ЗАПРЕТ и первому входу элемента И, выход которого

и выход элемента ЗАПРЕТ соединены с входами второго элемента ИЛИ, выход которого подключен к D-входу D-триг- гера, выходы первого и второго фор- мировател ей переднего фронта соединены соответственно с (S- и R-входами КЗТгтриггера, прямой выход которого подключен к второму входу элемента И, генератор тактовых импульсов, выход которого соединен с Т-входом RST-триггера, третьим входом блока управления и через элемент задержки - с С-входом D-триггера, инверсный

выход которого является первым выходом дельта-модулятора, отличающийся тем, что, с целью расширения области применения за счет дополнительного преобразования двух

произведение этого сигнала на его приращения, в дельта-модулятор введены сумматор, источник опорного напряжения и двухполупериодный вьшрями- тель, вход которого является входом дельта-модулятора, выход подключен к первому входу компаратора, выходы преобразователя код - напряжение и источника опорного напряжения подключены соответственно к первому и второму входам сумматора, выход которого соединен с вторым входом компаратора, выходы реверсивного счетчика являются вторыми выходами дельта-модулятора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дельта-модулятор | 1986 |

|

SU1345349A2 |

| Дельта-модулятор | 1987 |

|

SU1508350A2 |

| Дельта-модулятор | 1985 |

|

SU1257849A1 |

| Дельта-модулятор | 1988 |

|

SU1510090A2 |

| Дельта-модулятор | 1987 |

|

SU1448411A1 |

| Дельта-модулятор | 1990 |

|

SU1718383A1 |

| Дельта-модулятор | 1990 |

|

SU1709531A2 |

| Адаптивный дельта-модулятор со слоговым компандированием | 1991 |

|

SU1785078A1 |

| Дельта-модулятор | 1989 |

|

SU1649666A1 |

| Устройство для кодирования аналоговой информации | 1986 |

|

SU1338074A1 |

Изобретение относится к вычислительной технике. Его использование в системах преобразования и передачи информации позволяет расширить область применения за счет дополнительного преобразования двухполярного входного сигнала в цифровое произведение этого сигнала на его приращение. Дельта-модулятор содержит генератор 1 тактовых импульсов, компаратор 2, реверсивный счетчик 3, блок 4 управления, -преобразователь 5 код - напряжение, элементы ИЛИ 6 и 13, формирователи 7 и 8 переднего фронта, элемент ЗАПРЕТ 9, элемент И 10, элемент 12 задержки, RST-триггер 11 и D-триггер 14. Введение двухполупери- одного выпрямителя 15, источника 16 опорного напряжения и сумматора 17 обеспечивает требуемое преобразование . 3 ил. с «S (Л

ериг.2

(

rf

гГтТЪгС

t

i

.t

(Pu2.:j

| Кодирующее устройство с дельтамодуляцией и импульсно-кодовой модуляцией | 1977 |

|

SU661789A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Дельта-модулятор | 1985 |

|

SU1257849A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-04-15—Публикация

1986-08-11—Подача