Изобретение относится к вычислительной технике и может быть использовано при построении специализированных ЭВМ.

Вычисление функции 1/Z комплекс- ного переменного осуществляется по алгоритму 1/Z()/(X -lYV- -j (2XY/()

Целью изобретения является расширение области применения за.счет обеспечения вычисления значения функции от комплексного переменного.

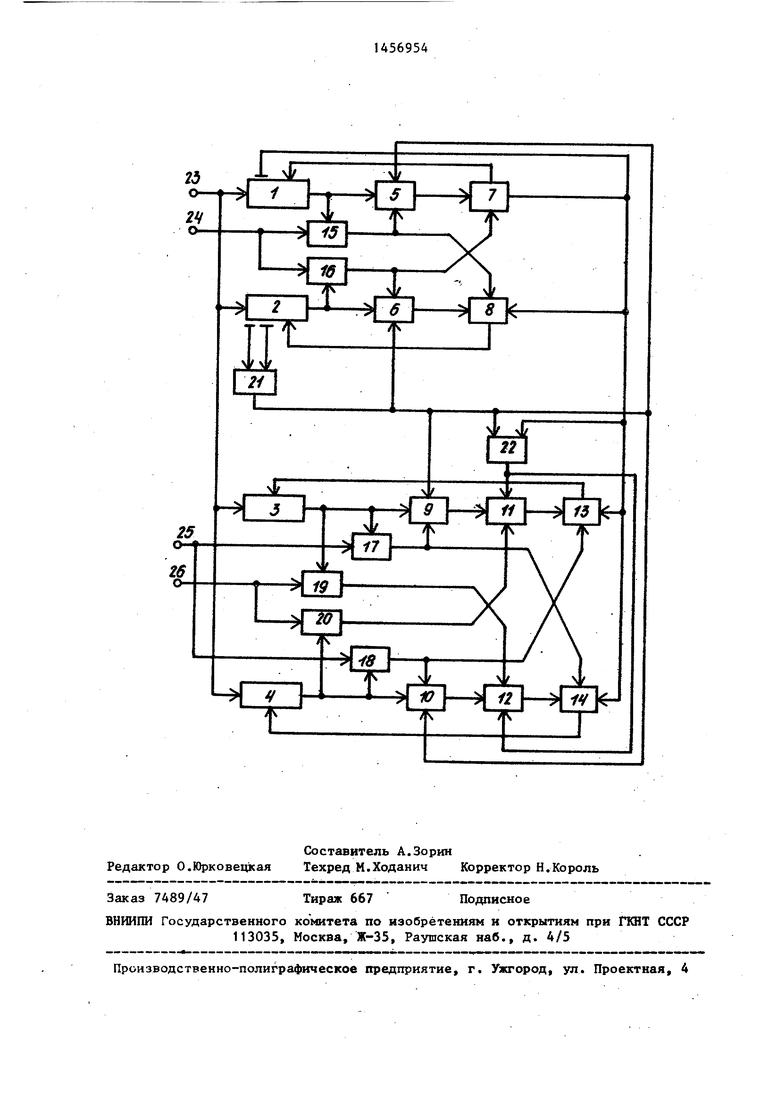

На чертеже изображена блок-схема предлагаемого устройства.

Устройство содержит четыре регистра 1 - 4, десять сумматоров-вычита- телей 5 - 14, шесть сдвигателей 15 - 20, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ.21 и 22, вход 23 тактовых импульсов, вход 24 кода величины К, вход 25 кода величины К-1 и вход 26 кода вели

чины 2К-1. I

Дпя пояснения работы устройства

введены следующие обозначения: А и В - соответственно мнимая (ордината вектора) и действительная (абсцисса вектора) части комплексного переменного (B+JA) приближения.аргумента к единице на л-м шаге алгоритма; С, и D - соответственно мнимая (ордината вектора) и действительная (абсцисса вектора) части комплексного переменного (D+jC) приближения функции l/Z на л-м шаге алгоритма; Е е Г-1, + 1 - оператор направления изменения аргумента (угла вектора) комплексного переменного (B+jA) H (D+jC), на л-м шаге алгоритма; Рд € f-1, + 1) - оператор направления изменения модуля (дпины вектора) комплексного переменного (B+jA) и () на л-м шаге алгоритма; л - сквозной номер шага от начала вычислений; К - номер выполняемой итерации; п - количество разрядов в дробной части числа, количество выполняемых итераций с двойными шагами; (п+2) - разрядность устройства, включая разряд в целой части числа и знаковый. Области значения аргумента О : 1X1 1;

О и: IYI 1.

Области значения функции

О I -2ХУ/(хЧуЪ I 1/2;

О Г(() 1 1/4.

Устройство реализует следзлияций

алгоритм вычисления функции ««A величины сдвига), од плексного переменного Z-X+jY. «° значепг е кода (К-О первой моди25 личины сдвига для третьего 19 и шестого 20 сдвигателей. При этом двум тактовым импульсам соответствует одно значение номера К выполняемой итерации (кода величины сдвига),- одНачальные условия

A, Y;

B, X;

C, 0;

D,- 1. Итерации Ej,

о

ЗНАК (Ад)

;t-l, если 1, если В. 5 1;

Л

А,-ЕЛ Вл

ВА+Ея-Ах-2 -СЛ-КА2

к

+P/I- А

Пл- 2- +Р,

-Е„.Р,-Вл-2; ;

D,+E,. Сд-2- +Р, +Е,.Р,. С,.

2- Ся

(1) (2) (3) (А) (5)

(б)

.-2-(7)

влв)

г- .

где

. /2 - для нечетных л; | л/2 - для четных л;

(О) (12)

(13) (14) (15) (16)

гп( являются соответственно мнимой и действительной частя-j ми функции комплексного переменного

л 1, 2,...,2п. Результаты

., 0;

Zntl 122

С.„., - - 2XY/(x4f) ; D-2n., (X -Y )/( .

фикахщи величины сдвига и одно значение кода (2К-О второй модификации величины сдвига, т.е. используются двойные шаги итераций в соответст35 ВИИ с выражениями (И) и (12). Под воздействием тактовых импульсов, номеров итераций (кодов величины сдвига), кодов первой.модификации величины сдвига и кодов второй модифика40 ции величины сдвига в устройстве развивается вычислительный процесс. Под воздействием каждого тактового импульса реализуется один шаг в соответствии с выражениями (5) -

45 (10).

QO) Значение оператора Е направления изменения аргумента комплексного переменного снимается с выхода знакового разряда первого регистра 1 50 выражение (5). Сигнал Е поступает на- входы седьмого 7, восьмого 8, третьего 13 и пятого 14 сумматоров- вычитателей для задания режимов работы (сложения или вычитания), а так55 же на второй вход второго элемента ИСКЛЮЧАМЦЕЕ ИЛИ 21 - выражение (6). Сигнал Рд поступает на входы первого 5, второго 6, четвертого 9 и шестого 10 сумматоров-вычитателей для за695А

««A величины сдвига), од «° значепг е кода (К-О первой модиl/Z« l/(X-t-iY)()/(xSY - -j (2XY/(XVY)).

В исходном положении в регистрах находятся следующие данные; в первом регистре 1 - мнимая часть Y комплексного аргумента Z; во втором регистре 2 - действительная часть X комплексного аргумента Z; в третьем регистре

10 3 - число 0; в четвертом регистре 4 - число I. Таким образом, реализованы выражения (1) -, (4).

Устройство работает циклически. На л-м шаге на вход 23 тгштовых им15 пульсов устройства подается синхросигнал, на вход 24 кода величины К - номер К выполняемой итерации (код величины сдвига для четвертого 15 и первого 16 сдвигателей), на.вход

20 25 кода величины К-1 - код (К-1) первой модификации величины сдвига для второго 17 и пятого 18 сдвига- телей, на вход 6 кода величины 2К-1 - код (2К-1) второй модифика;ции ве25 личины сдвига для третьего 19 и шестого 20 сдвигателей. При этом двум тактовым импульсам соответствует одно значение номера К выполняемой итерации (кода величины сдвига),- оддания режимов работы (сложения или вычитания), а также на первый вход второго элемента ИСЮЮЧАЮЩЕЕ ИЛИ 22.

На выходе второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 22 формируется сигнал которьгй поступает на входы девятого 1-1 и десятого 12 сумматоров-вычи- тателей для задания режимов работы (сложения или вычитания).

В соответствии с кодом К величины сдвига (номером выполняемой итерации) в четвертом 13 и первом 16 сдви- гателях выполняется сдвиг предыдущих значений соответственно мнимой Ад и действительной В/, частей комплексного переменного (B+jA) на К разрядов вправо, т.е. на выходах четвертого 15 и первого 16 сдвигателей формируются величины соответственно А.- 2

и Вд. 2

В соответствии t кодом (К-1) первой модификации величины сдвига во втором 17 и пятом 18 сдвигателях выполняется сдвиг предыдущих значений соответственно мнимой Сд и действительной D частей комплексного переменного (D+JC) на К-1 разрядов вправо, т.е. на выходах второго 17 и пятого 18 сдвигателей формируются ве личины соответственно С,- 2 и D, 2-- .

В соответствии с кодом 2К-1 второй модификации величины сдвига в третьем 19 и шестом 20 сдвигателях вьшолняется сдвиг предыдущих значений соответственно мнимой Сд и действительной Од частей комплексного переменного (D+JC) на 2К-1 разрядов вправо, т.е. на выходах третьего 19 и шестого 20 сдвигателей формируются величины соответственно С,- 2 .и

D . и

Предьщущее значение мнимой части А комплексного переменного (B+jA) и его приращения Ад 2 и 2 поступают соответственно с первого регистра 1, четвертого сдвигателя 15 и первого сдвигателя 16 в цепь, состоящую из первого 5 и седьмого 7 сумматоров-вычитателей, в результате в седьмом сумматоре-вычитателе 7 формируется новое значение мнимой части Ад, комплексного переменного (B+JA), которое фиксируется в пер- вом регистре 1 - выражение (7).

Предыдущее значение действительной части Вд комплексного переменного (B+JA) и его приращения БД- 2 и

поступают соответственно с второго регистра 2, первого 16 и четвертого 15 сдвигателей в цепь, состоящую из второго 6 и восьмого 8 сум- маторов-вычитателей, в результате в восьмом сумматоре-вычитателе 8 формируется новое значение действительной части Вд., комплексного переменного (B+JA), которое фиксируется во втором регистре 2 - выражение (8).

Предьщущее значение мнимой части Сд комплексного переменного (D+jC)

и его приращения С, 2 , D, 2

, - к

и Пд

,поступают соответствен

но с третьего регистра 3, второго 17, шестого 20 и пятого 18 сдвигателей в цепь, состоящую из четвертого 9, девятого 11 и третьего 13 сумматоров-вычитателей, в результате в третьем сумматоре-вычитателе 13 формируется новое значение мнимой части Сfl., комплексного переменного (D+JC), которое фиксируется в третьем регистре 3 - выражение (9).

Предыдущее значение действительной части D, комплексного переменно- k 41

го (D+JC) и его приращения D,- 2 , Сд- и поступают соответственно с четвертого регистра 4, пятого 18,третьего . 19 и второго 17 сдвигателей в цепь, состоящую из шестого 10 и пятого 14 сумматоров- вычитателей, в результате в пятом сумматоре-вычитателе 14 формируется новое значение действительной части D д., комплексного переменного (D+ +JC), которое фиксируется в четвертом регистре 4 -: выражение (10).

Все итерационные шаги выполняются в устройстве аналогично.

После выполнения п итераций с двойными шагами в регистрах зафиксированы следукидие результаты: в первом регистре 1 - А,., 0; во втором регистре 2 - ,1; в третьем регистре 3 - , -2XY/();, в четвертом регистре 4 - D,, (Х -Y )/

(xVY)

Таким образом, реализованы выражения (13) - (16).

Формула изобретения

Устройство для вычисления функции 1/Z, содержащее три регистра, четыре сумматора-вычитателя, три сдвигателя, причем выходы первого и второго регистров соединены с входами первого слагаемого соответственно первго и второго сумматоров-вычитателей выход второго регистра соединен с информационным входом первого сдвиг теля, выход третьего регистра соединен с информационными входами второго и третьего сдвигателей, выходы первого и второго сдвигателей соединены с входами второго слагаемого соответственно второго и четвертого сумматоров-вычитателей, выход третьего сумматора-вь1читателя соединен с информационным.входом третьего регистра, вход тактовых импульсов устройства соединен; с входами синхронизации первого, второго и третьего регистров, вход кода величины К (К номер- итерации) устройства соединен с эходом управления сдвигом первого сдвигателя, вход кода величины К-1 устройства соединен с входом управлния сдвигом второго сдвигателя, вход кода величины 2К-1 устройства соединен с входом управления сдвигов третьего сдвигателя, отличающееся тем, что, с целью расширения области применения за счет обеспечения вычисления значения функции от комплексного переменного, в него введены четвертый регистр, с пятого по десятый сумматоры-вычитатели, с четвертого.по шестой сдвигатели,два элемента ИСКЛЮЧАВДЕЕ ИЛИ, причем выход первого регистра соединен с информационным входом четвертого сдвигателя, выход третьего регистра соединен с входом первого слагаемого четвертого сумматора-вычитателя, выход четвертого регистра соединен с входом первого.слагаемого шестого сумматора-вычитателя и информационными входами пятого и шестого сдвигателей, выходы первого второго, четвертого и шестого сумматоров-вычитателей соединены с входами первого слагаемого соответственно седьмого, восьмого, девятого и десятого сумма

0

5

0

торов-вычитателей, выходы которых соединены соответственно с информационным входом первого регистра, информационным входом второго регистра, входом первого слагаемого третьего сумматора-вычитателя и входом первого слагаемого пятого сумматора-вычитателя, выход пятого сумматора- вычитателя соединен с информационным входом четвертого регистра, выходы первого, второго, третьего и шестого сдвигателей соединены с входами второго слагаемого соответственно седьмого, пятого, десятого и девятого сумматоров-вычитателей, выход четвертого двигателя соединен с входами второго слагаемого первого и восьмого сумматоров-вычитателей, выход пятого сдвигателя соединен с входами второго слагаемого третьего и шестого сумматоров-вычитателей, вход тактовых импульсов устройства соединен с входами синхронизации четвертого регистра, входы кодов величин К, К-1 и 2К-1 устройства соединены с входами управления сдвигом соответственно четвертого, пятого и шестого сдвигателей, выход зна- Q кового разряда первого регистра соединен с входами задания режима седьмого, восьмого, третьего и пятого сумматоров-вычитателей, выходу знакового и старшего разрядов второго регистра соединены со ответственно с первым и вторым входами первого элемента ИСКПЮЧАКЯЦЕЕ ИЛИ, выход которого соединен с входами задания режима первого, второго, четвертого и шестого сумматоров-вычитателей и первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с входами задания режима девятого и десятого сумматоров-вычита- g телей, второй вход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с выходом - знакового разряда первого .регистра.

5

5

0

2д

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления квадратного корня | 1986 |

|

SU1397904A1 |

| Устройство для вычисления обратного гиперболического тангенса | 1987 |

|

SU1456952A1 |

| Устройство для вычисления гиперболических синуса и косинуса | 1987 |

|

SU1497615A1 |

| Устройство для вычисления функций | 1986 |

|

SU1374219A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ НАТУРАЛЬНОГО ЛОГАРИФМА КОМПЛЕКСНОГО ЧИСЛА | 1991 |

|

RU2010312C1 |

| Анализатор спектров | 1982 |

|

SU1023341A1 |

| Устройство для вычисления направляющих косинусов вектора в пространстве | 1982 |

|

SU1164700A1 |

| Вычислительное устройство | 1986 |

|

SU1322270A1 |

| Устройство для вычисления функции | 1986 |

|

SU1348829A1 |

| Устройство для быстрого преобразования Фурье | 1988 |

|

SU1524066A1 |

Изобретение относится к области вычислительной техники. Цель изобретения - расширение области применения устройства. Изобретение позволяет расширить за счет обеспечения вычисления функции 1/Z комплексного переменного Z-область применения устройства, содержащего три регистра, четыре сумматора, три сдвигателя и реализующего моди идированный алгоритм Волдера при вычислении функции Y X действительных переменных X и Y. Дпя этого в устройство дополнительно введены четвертый регистр, сумматоры с пятого по десятый, четвертый, пятый, шестой сдвигатели, первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, обусловливаю1дие появление свойства преобразования путем вычислений комплексного аргумента Z в единицу и преобразования единицы в комплексное число, обратное квадрату аргумента. 1 ил. 3 (Л

| Байков В.Д., Смолов В.Б., Специализированные процессоры: Итерационные алгоритмы и структуры | |||

| - М.: Радио и связь, 1985 | |||

| Устройство для вычисления функции вида ух | 1975 |

|

SU579612A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-02-07—Публикация

1987-06-29—Подача