(Л

р

О1

ю

Изобретение относится к вычислительной технике и может быть использовано при построении систем передачи и переработки дискретной информации.

Целью изобретения является упрощение сумматора по модулю три.

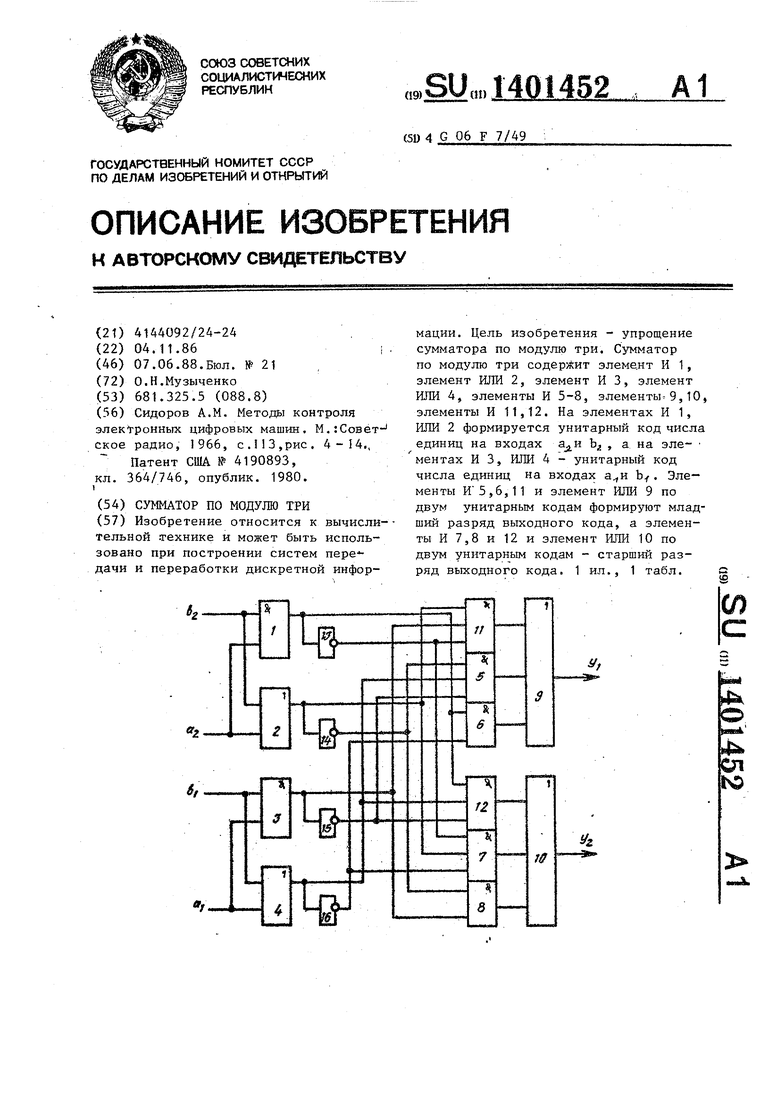

На чертеже изображена схема сумматора по модулю три.

Сумматор по модулю три содержит элементы И 1, ШШ 2, И 3, ИЛИ 4, И 5-8, ИЛИ 9 и to,И 11,12 и НЕ 13-16.

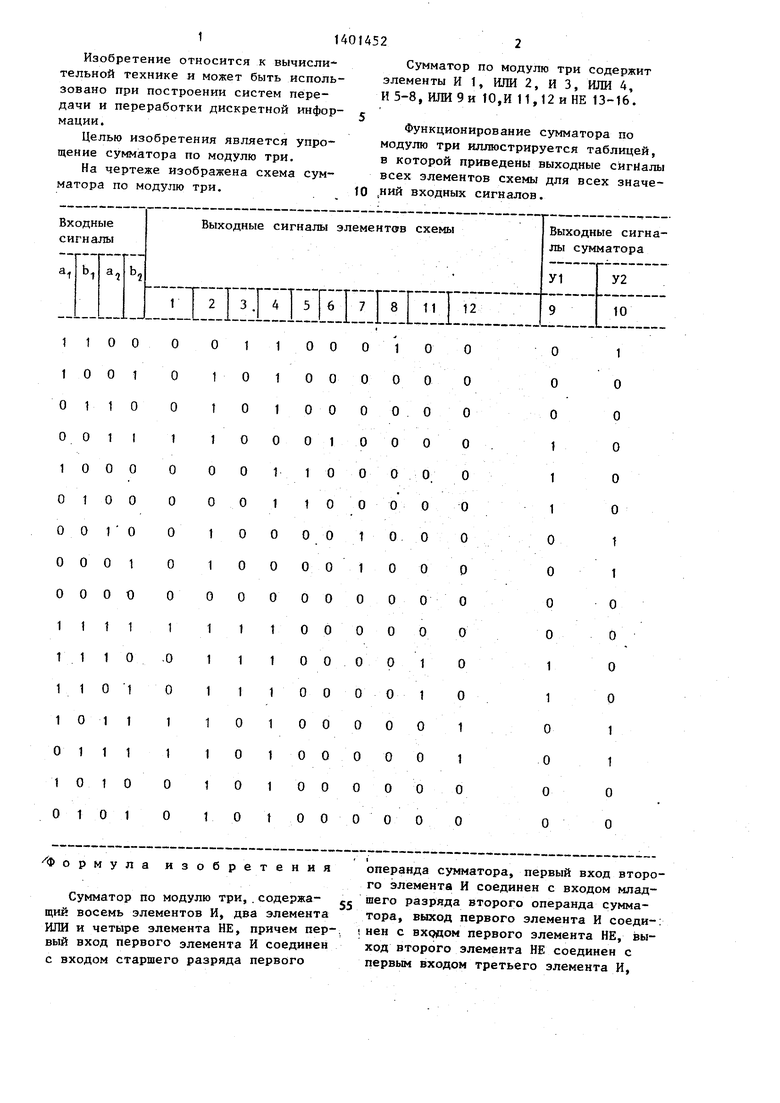

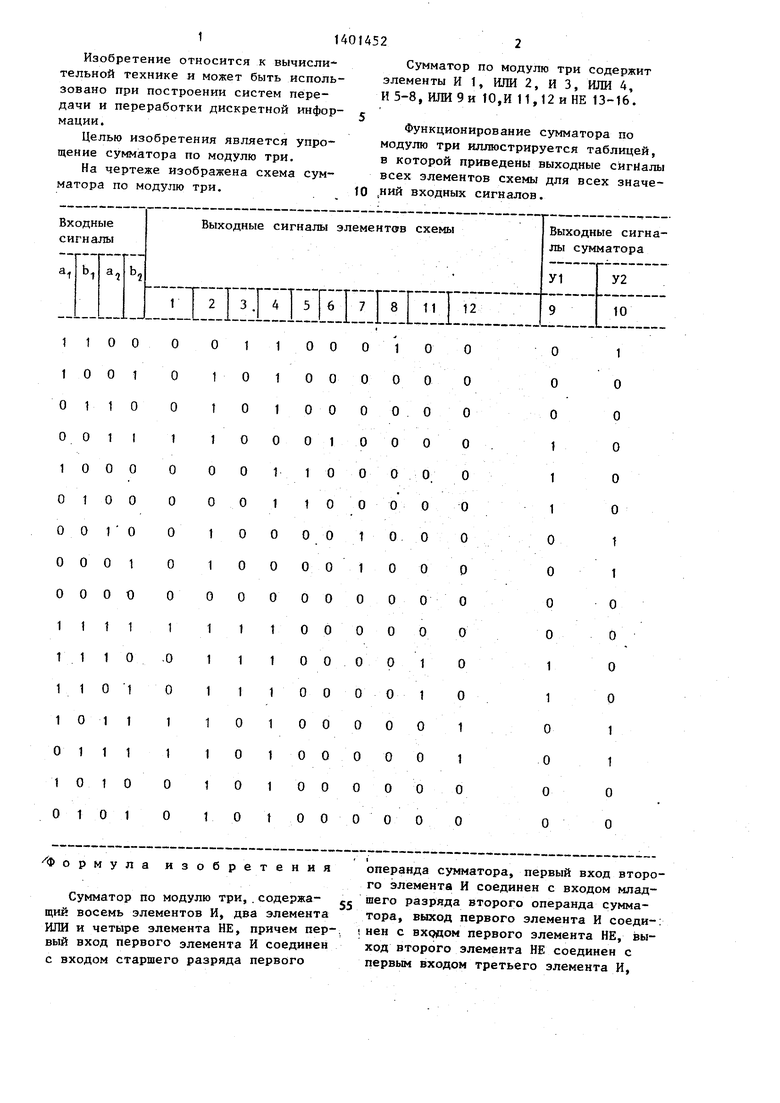

Функционирование сумматора по

модухпо три иллюстрируется таблицей, в которой приведены выходные сйгИалы всех элементов схемы для всех значе- ,ний входных сигналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство по модулю | 1985 |

|

SU1285468A1 |

| Устройство для контроля информации по модулю | 1989 |

|

SU1751764A1 |

| Устройство для деления чисел | 1990 |

|

SU1795456A1 |

| Устройство для контроля информации по модулю | 1989 |

|

SU1751763A1 |

| Сумматор-умножитель по модулю три | 1987 |

|

SU1441395A1 |

| Сумматор по модулю пять | 1991 |

|

SU1803911A1 |

| Устройство для выполнения операций умножения и деления | 1980 |

|

SU955038A1 |

| Управляемый арифметический модуль | 1989 |

|

SU1695292A1 |

| Устройство для вычисления квадратного корня из суммы квадратов | 1990 |

|

SU1751751A1 |

| СУММАТОР ПО МОДУЛЮ ПЯТЬ | 1992 |

|

RU2012038C1 |

Изобретение относится к вычислительной .технике и может быть использовано при построении систем пере- дачи и переработки дискретной информации. Цель изобретения - упрощение сумматора по модулю три. Сумматор по модулю три содержит элемент И 1, элемент РШИ 2, элемент И 3, элемент PfflH 4, элементы И 5-8, элементы 9,10, элементы И 11,12. На элементах И 1, ИЛИ 2 формируется унитарный код числа единиц на входах Ъ , а на эле- ментах И 3, ИЛИ 4 - унитарный код числа единиц на входах Ъ. Элементы И 5,6,11 и элемент ИЛИ 9 по двум унитарным кодам формируют младший разряд выходного кода, а элементы И 7,8 и 12 и элемент ИЛИ 10 по двум унитарным кодам - старший разряд выходного кода. 1 ил., 1 табл. (В

Формула изобретения

Сумматор по модулю три,.содержащий восемь элементов И, два элемента ИЛИ и четыре элемента НЕ, причем первый вход первого элемента И соединен с входом старшего разряда первого

операнда сумматора, первый вход второго элемента И соединен с входом млад- шего разряда второго операнда сумматора, выход первого элемента И соеди-: ней с входом первого элемента НЕ, выход второго элемента НЕ соединен с первым входом третьего элемента И,

второй вход которого соединен с выходом третьего элемента НЕ, вход которого подключен к выходу второго элемента И, первый вход четвертого элемента И соединен с выходом первого элемента И, первый и второй входы пятого элемента И подключены соответственно к выходам первого и четвертого элементов НЕ, первый вход шестого элемента И соединен с выходом второго элемента И, первый и второй входы седьмого элемента И соединены соответственно с выходами второго элемента И и первого элемента НЕ, первый и второй входы восьмого элемента И соединены соответственно с выходами первого элемента И и третьего элемента НЕ, выходы третьего, четвертого и седьмого элементов И соединены с вхо- дами первого элемента ИЛИ, выход которого является выходом младшего разряда сумматора, выходы пятого, шестого и восьмого элементов И соединены с входами второго элемента ИЛИ,

выход которого является выходом стар- шнго разряда сумматора, о т ч а ю- щ и и с я , тем, что, с целью упрощения, он содержит третий и четвертый элементы ИЛИ, причем входы третьего элемента ИЛИ соединены с входами старших разрядов первого и второго операндов сумматора, а выход подключен к третьим входам пятого и седьмого элементов И и входу второго элемента НЕ, выход которого соединен с вторым входом шестого элемента И, входы четвертого элемента ИЛИ соединены с входами младших азрядов первого и второго операндов сумматора, а выход подключен к третьим входам третьего и восьмого элементов И и входу четвертого элемента НЕ, выход которого соединен с вторым входом четвертого элемента И, вторые входы первого и второго элементов И соединены соответственно с входом старшего разряда второго операнда и с входом младшего разряда первого операнда сумматора.

| Сидоров A.M | |||

| Методы контроля электронных цифровых машин | |||

| М.:Совет- ское радио, 1966, с | |||

| Способ обработки грубых шерстей на различных аппаратах для мериносовой шерсти | 1920 |

|

SU113A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Способ получения мыла | 1920 |

|

SU364A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

| I | |||

Авторы

Даты

1988-06-07—Публикация

1986-11-04—Подача