Изобретение относится к вычислительной технике и электронике и может использоваться при построении многоразрядных сумматоров и арифметико-логических устройств в составе КМОП БИС.

Цель изобретения - повышение надежности и быстродействия схемы сквозного переноса.

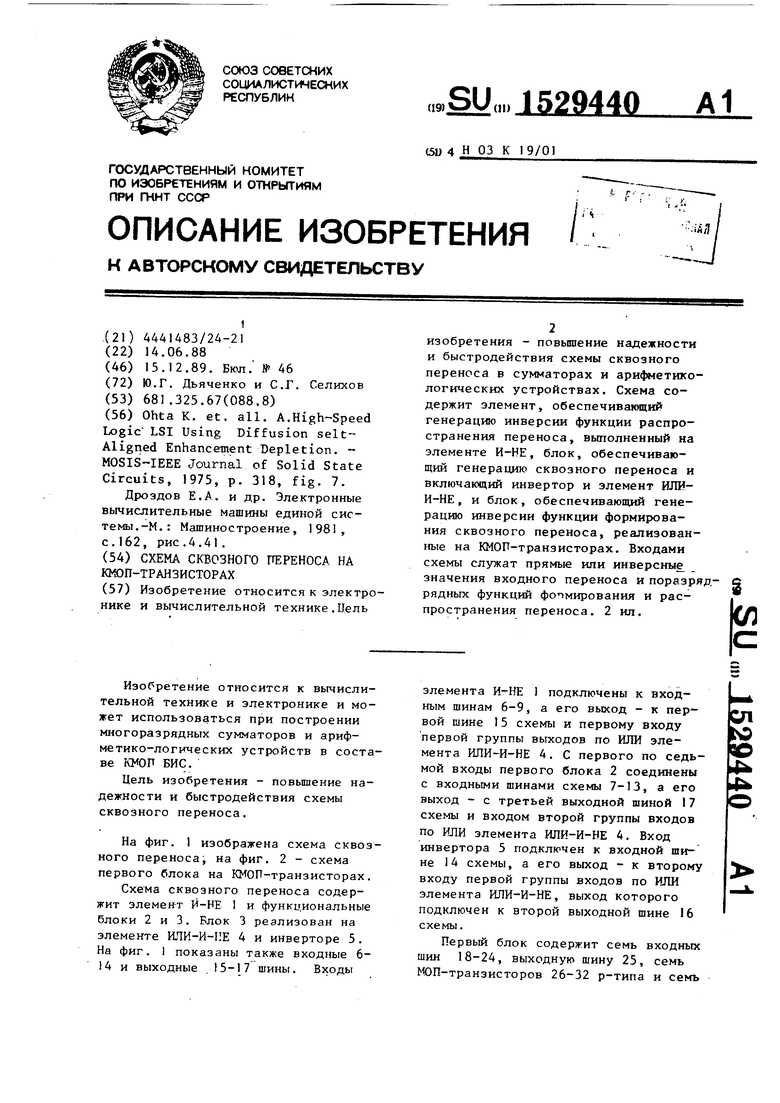

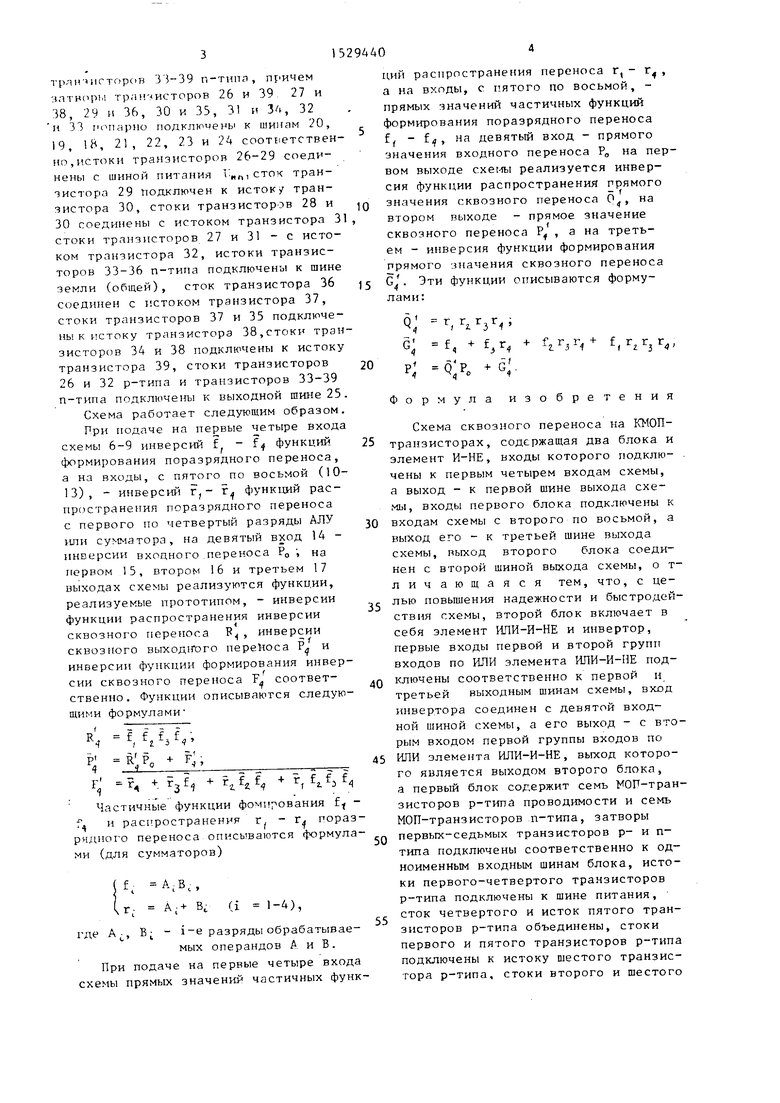

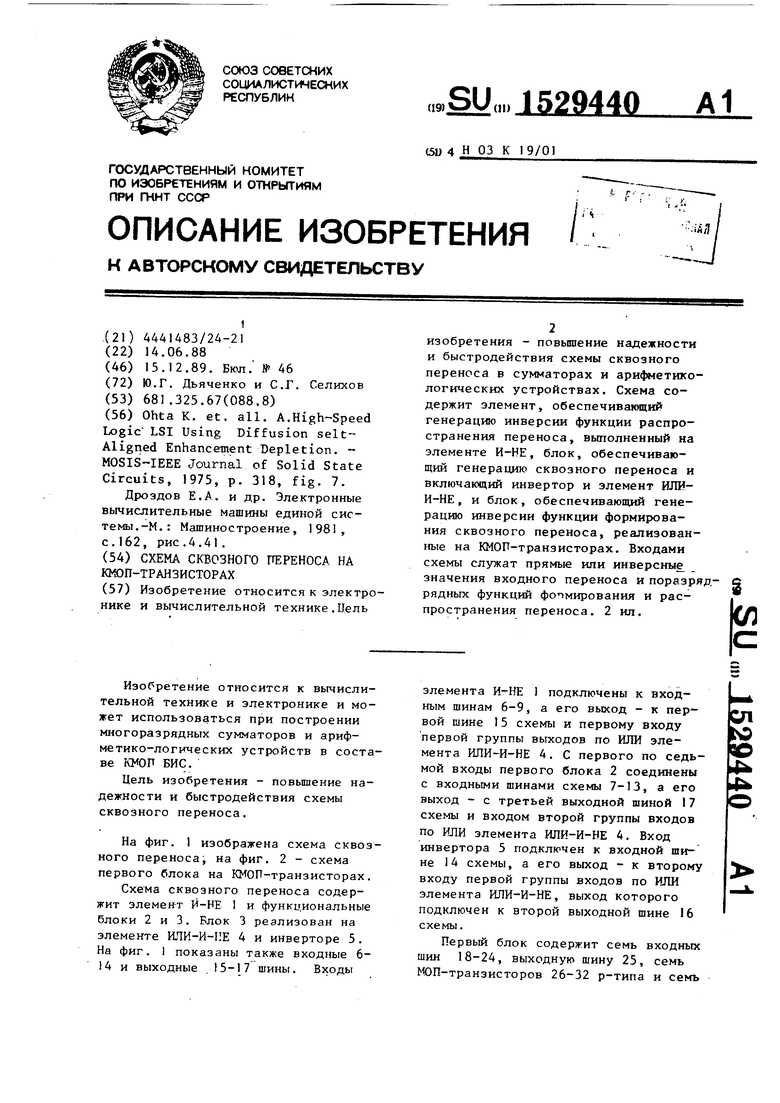

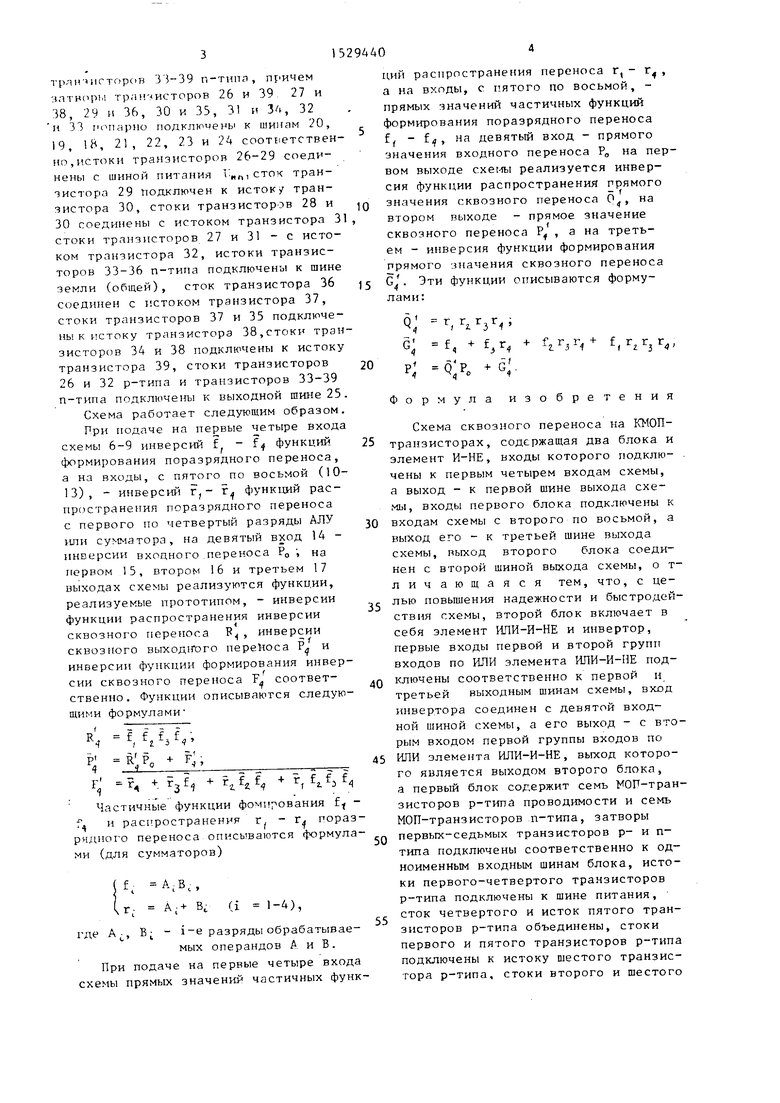

На фиг. 1 изображена схема сквозного переноса, на фиг. 2 - схема первого блока на КМОП-транзисторах.

Схема сквозного переноса содержит элемен-т Й-НЕ 1 и функциональные блоки 2 и 3. Блок 3 реализован на элементе ИЛИ-И-ПЕ 4 и инверторе 5. На фиг. 1 показаны также входные 6- 14 и выходные .15-17 шины. Входы

элемента И-НЕ 1 подключены к входным шинам 6-9, а его выход - к первой шине 15 схемы и первому входу первой группы выходов по ИЛИ элемента ИЛИ-И-НЕ 4. С первого по седьмой входы первого блока 2 соединены с входньми шинами схемы 7-13, а его выход - с третьей выходной шиной I7 схемы и входом второй группы входов

по или элемента ИЛИ-И-НЕ 4. Вход инвертора 5 подключен к входной шине 14 схемы, а его выход - к второму входу первой группы входов по ИЛИ элемента ИЛИ-И-НЕ, выход которого подключен к второй выходной шине 16 схемы.

Первый блок содержит семь входных шин 18-24, выходную шину 25, семь ЮП-транзисторов 26-32 р-типа и семь

ря1Г игторс1в 33-39 n-тнпа, пр ичем лтн(1ры траи чисторов 26 и 39 27 и 8, 29 и 36, 30 к 35, 31 и 34, 32 33 luniapiio подключень к шинам 20, 9, 18, 21, 22, 23 и 24 соотиетствен- о,истоки транзисторов 26-29 соедиены с шиной питания Г„,сток транзистора 29 подключен к исток/ транзистора 30, стоки транзисторов 28 и 30 соединены с истоком транзистора 31, стоки транзисторов 27 и 31 - с истоком транзистора 32, истоки транзисторов 33-36 п-типа подключены к шине земли (общей), сток транзистора 36 соединен с истоком транзистора 37, стоки транзисторов 37 и 35 подключены к истоку транзистора 38,стоки транзисторов 34 и 38 подключены к истоку транзистора 39, стоки транзисторов 26 и 32 р-типа и транзисторов 33-39 п-типа подключены к выходной шине 25.

Схема работает следутощим образом.

При подаче на первые четыре входа схемы 6-9 инверсий - f функций формирования поразрядного переноса, а на входы, с пятого по восьмой (10- 13), - инверсий г,- г. функций распространения поразрядного переноса с первого по четвертый разряды АЛУ или сумматора, на девятый вход 14 - инверсии входного.переноса РО ; на первом 15, втором 16 и третьем 17 выходах схемы реализуются функции, реализуемые прототипом, - инверсии функции распространения инверсии

PJ. инверсии f;

сквозного переноса

м

сквозного ВЫХОД1ГОГО перекоса Р. инверсии функции формирования инвер-п

сии сквозного переноса 1. соответственно. Функции описываются следующими формулами

Частичные функции фоми ования f

поразf и распространения

рядного переноса опись ваются формулами (для сумматоров)

Ь ,,

г. А;+ в, (i 1-4),

где А, В ; - разряды обрабатываемых операндов А и В. При подаче на первые четыре входа схемы прямых значений частичных функций распространения переноса

г,а на входы, с пятого по восьмой, - прямых значений частичных функций формирования поразрядного переноса f| f. ча девятый вход - прямого значения входного переноса „ на первом выходе cxet-ibi реализуется инверсия функции распространения прямого

значения сквозного переноса 0, на втором выходе - прямое значение сквозного переноса Р , а на третьем - инверсия функции формирования прямого значения сквозного переноса

G Эти функции описываются формулами:

Фор

У л а

изобретения

5

0

0

5

Схема сквозного переноса на КМОП- транзисторах, содержащая два блока и элемент И-НЕ, входы которого подклю- чены к первым четырем входам схемы, а выход - к первой шине выхода схемы, входы первого блока подключены к входам схемы с второго по восьмой, а выход его - к третьей шине выхода схемы, выход второго блока соединен с второй шиной выхода схемы, о т- личающаяся тем, что, с цес лью повьшения надежности и быстродействия схемы. Второй блок включает в себя элемент ИЛИ-Й-НЕ и инвертор, первые входы первой и второй групп входов по ИЛИ элемента ИЛИ-И-ИЕ подQ 1спючены соответственно к первой и третьей выходным шинам схемы, вход инвертора соединен с девятой входной шиной схемы, а его выход - с вторым входом первой группы входов по

5 ИЛИ элемента ИЛИ-И-НЕ, выход которого является выходом второго блока, а первый блок содержит семь МОП-транзисторов р-типа проводимости и семь МОП-транзисторов п-типа, затворы нервых-седьмых транзисторов р- и п- типа подключены соответственно к одноименным входным шинам блока, истоки первого-четвертого транзисторов р-типа подключены к шине питания, сток четвертого и исток пятого транзисторов р-типа объединены, стоки первого и пятого транзисторов р-типа подключены к истоку шестого транзистора р-типа, стоки второго и шестого

транзисторов р-тнпя соединены с истоком седьмого транзистор; р-титта, истоки четвертого-седьмого тран-эис- торов п-типа соединены с общей шиной, сток четвертого транзистора п-типа соединен с истоком первого транзистора п-типа, стоки первого и пятого

транзисторов п-типа подключены к истоку второго транзистора п-типа, стоки второго и QiecToro транзисторов п-типа соединены с истоком третьего транзистора п-типа, стоки третьих и седьмых транзисторов р- и п-типа - с шиной вькода блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный логический модуль | 1986 |

|

SU1405109A1 |

| СУММАТОР | 1994 |

|

RU2049346C1 |

| Г-ТРИГГЕР | 2007 |

|

RU2371842C2 |

| Арифметико-логическое устройство | 1987 |

|

SU1481742A1 |

| СУММАТОР НА КМДП ТРАНЗИСТОРАХ | 2001 |

|

RU2185655C1 |

| УСТРОЙСТВО СЛОЖЕНИЯ С УСКОРЕННЫМ ПЕРЕНОСОМ | 2000 |

|

RU2198421C2 |

| Логический элемент | 1989 |

|

SU1631715A1 |

| УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ УРОВНЕЙ ЛОГИЧЕСКИХ СИГНАЛОВ НА КМОП-ТРАНЗИСТОРАХ | 1993 |

|

RU2085030C1 |

| ОДНОРАЗРЯДНЫЙ ДВОИЧНЫЙ КМОП СУММАТОР | 2011 |

|

RU2454703C1 |

| ТРОИЧНЫЙ ИНВЕРТОР НА КМОП ТРАНЗИСТОРАХ | 2008 |

|

RU2373639C1 |

Изобретение относится к электронике и вычислительной технике. Цель изобретения - повышение надежности и быстродействия схемы сквозного переноса в сумматорах и арифметико-логических устройствах. Схема содержит элемент, обеспечивающий генерацию инверсии функции распространения переноса, выполненный на элементе И-НЕ, блок, обеспечивающий генерацию сквозного переноса и включающий инвертор и элемент ИЛИ-И-НЕ, и блок, обеспечивающий генерацию инверсии функции формирования сквозного переноса, реализованные на КМОП-транзисторах. Входами схемы служат прямые или инверсные значения входного переноса и поразрадных функций формирования и распространения переноса. 2 ил.

Фиг Л

Фиг. 2

| Ohta К | |||

| ее | |||

| all | |||

| А.High-Speed Logic LSI Using Diffusion selt- Aligned Enhancement Depletion | |||

| - MOSIS-IEEE Journal of Solid State Circuits, 1975, p | |||

| Способ изготовления фасонных резцов для зуборезных фрез | 1921 |

|

SU318A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Дроздов E.A | |||

| и др | |||

| Электронные вычислительные машины единой системы.-М.: Машиностроение, 1981, с | |||

| Деревянное стыковое скрепление | 1920 |

|

SU162A1 |

Авторы

Даты

1989-12-15—Публикация

1988-06-14—Подача