(Л

с

о о

00 О)

(риг.1

ГЧ)

К4

Зинационных, так и в последователь- остньгх схемах, в том числе и неисправностей типа короткое замыкание, с|оздающих контуры обратной связи с и)ечетным числом инверсий и вызьшаю- Цих появление в линии короткого.за- уыкания устойчивой генерации. Это достигается тем, что после завершения переключения логических элементов проверяемого узла 3 в устройстве предусмотрен анализ на наличие в

10036

схеме устойчивой генерации, В случае ее возникновения в индуктивном датчике 28 появляется сигнал, который через дифференцирующий узел 21, первый 22 и второй 23 усилители поступает на входы элемента ИЛИ 2А и запускает формирователь импульсов 29. Сигнал с выхода формирователя 29 через элемент памяти 26 включает индикатор 27j фиксируя наличие неисправности б схеме. 2 ил „

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических узлов | 1982 |

|

SU1020829A1 |

| Устройство для контроля и диагностики цифровых блоков | 1986 |

|

SU1388871A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для проверки функционирования логических схем | 1980 |

|

SU955072A1 |

| Устройство для контроля и диагностики блоков микроЭВМ | 1985 |

|

SU1374230A1 |

| Устройство для контроля логических узлов | 1980 |

|

SU868764A1 |

| Устройство для локализации неисправностей | 1980 |

|

SU903888A1 |

| Устройство для контроля КМОП-логических схем | 1987 |

|

SU1552137A1 |

| Устройство для контроля многовыходных цифровых узлов | 1988 |

|

SU1566353A1 |

| Устройство для контроля логических узлов | 1980 |

|

SU991430A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля исправности логических блоков и цифровых схем. Цель изобретения - повышение достоверности контроля. Изобретение позволяет осуществить контроль и локализацию константных и неконстантных неисправностей как в ком

1

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля исправности логических блоков и цифровых схем и является дополнительным к основному ЗЕТ. св. № 1020829.

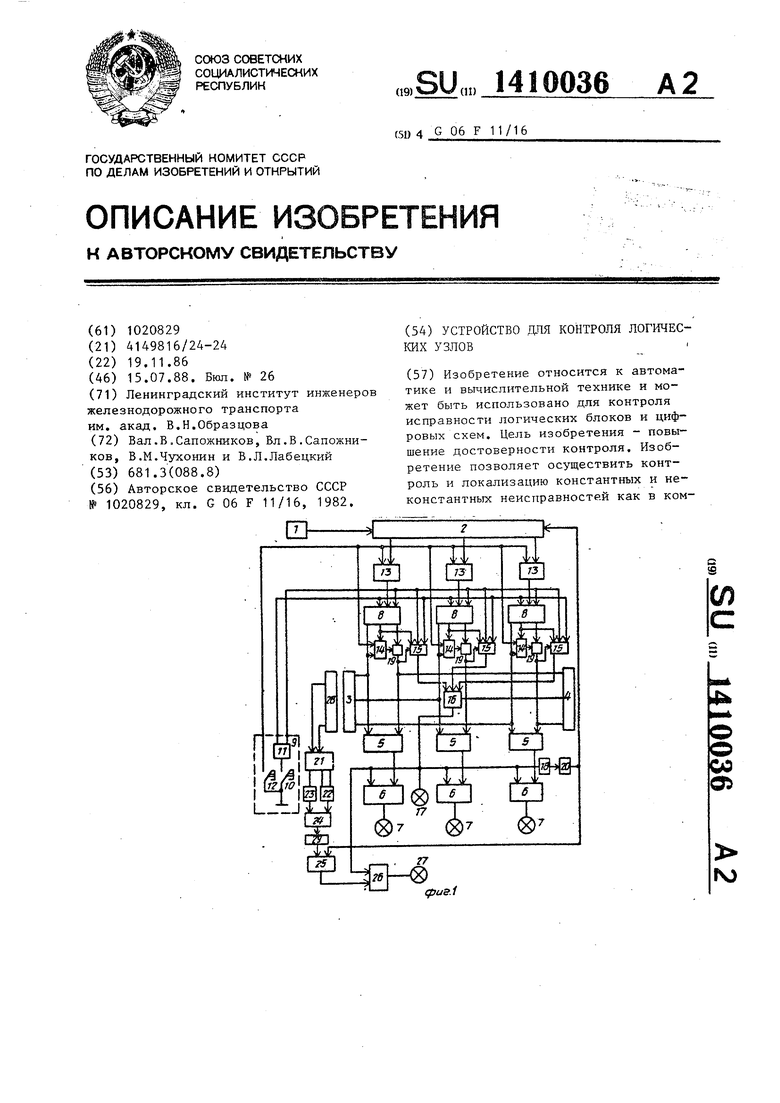

Цель изобретения - повышение достоверности контроля. I На фиг.1 представлена-схема предлагаемого устройства; на фиг.2 - при мер выполнения согласующего блока и индуктивного датчика.

I Устройство содержит генератор 1 импульсов, счетчик 2, проверяемый узел 3, блок 4 хранения эталонов, элемент 5 сравнения, элемент 6 памяти, индикатор 7, блок 8 фиксации вхо- дор, блок 9 управления, содержащий переключатель 10, формирователь 11 запуска, переключатель. 12, Кроме того устройство Ьодержит элемент И 13, переключатель 14, блок 15 регистрации переключений, элемент И-НЕ 16, инди- 17, формирователь 18 импульсов, элементы ИЛИ 19, элемент 20 задержки, бл0к электрического согласования, состоящий из дифференцирукнцего узла 21 первого усилителя 22 и второго ус Йлителя 23, элемент ИЛИ 24, элемент И 25, элемент 26 памяти, индикатор 27 индуктивный датчик 28, второй фо1()мирователь 29 импульсов, транзис- торы 30 и 31, резистор 32, конденсатор 33, резисторы 34 и 35.

Устройство работает по принципу сравнения входных и выходных сигналов двух идентичных блоков - проверяемого узла 3 и блока 4 хранения этапо

0

5

5 Q

0

5

нов. Устройство имеет два режима ра- боты. Первый соответствует контролю узлов, второй - контролю микросхем, установленных на печатных платах.

Устройство работает следующим образом (см. фиг.1).

Первоначальна все элементы 6 памяти, блоки 8, 15 и элемент 26 устайав- ливаются в нулевое состояние. Переключателем 10 запускается формирователь 11 запуска, открьгоающий блоки 8 фиксации входов, которые определяют выводы блока 4 хранения эталонов, соответствующие входам блока, включают блоки 15 регистрации переключений, соответствующие входам блока 4 хранения эталонов, устанавливая их в нулевое состояние, отключают блоки 15 регистрации переключений, соответствуют- щие выходам блока 4 хранения эталонов, устанавливая их в единичное состояние, а также в зависимости от режима работы либо начинают передавать тестовые сигналы от счетчика 2 через элементы И 13 на Иходы проверяемого узла 3 и блока 4 хранения эталонов, либо во втором режиме открывают переключатели 14, что обеспечивает передачу сигналов с входов проверяемого узла на входы блока 4 хранения эталонов. Включенные блоки 15 регистрации переключений через элемент И-НЕ 16 удерживают элементы 6 и 26 памяти в исходном состоянии. После того как на всех входах блока 4 хранения эталонов произойдет переключение, т.е. осуществится подача сигналов на все возможные установочные входы проверя 1410036

емого узла 3 и блока 4 хранения эталонов, все блоки 15 регистрации переключений отключаются, снимая запрет на включение элементов памяти сигналами с выходом элементов 5 сравнения. Одновременно с этим сигнал низкого логического уровня с выхода элемента И-НЕ 16 включает индикатор 17 и запускает формирователь 18 импульсов. Элементы 5 сравнения в обоих режимах сравнивают сигналы на вьгоодах блоков 3 и 4 и в случае их несовпадения выдают сигналы на соответствующий элемент 6 памяти, которьш в этом случае устанавливается в состояние, соответствующее свечению индикатора 7, Сиг- .нал с выхода формирователя 18 импульсов через элемент 20 задержки с вре

усиливается, дифференциальным каскадом и с резисторов 34 и 35 поступает на усилитель 22, где усиливается до уровня, достаточного для срабатывания элемента ИЛИ 24. Таким образом, если в испытуемом узле возникла устойчивая генерация, вызванная неисправностью типа короткое замыкание с обратными связями, на выходе формирователя 29 появится сигнал высокого логического уровня. Этот сигнал сохранится и после завершения переключений логических .элементов блока хранения 15 эталонов, т,е„ и после истечения задержки времени, выработанной элементом 20 задержки. Если в испытуемом узле устойчивая генерация не возннк10

ла, то после заверпюния переключения менной задержкой, необходимой для за- 20 логических элементов блоков 3 и 4 на вершения переключения логических эле™ выходе форг шрователя 29, а следоваи

ментов проверяемого узла, осуществляет установку счетчика 2 в исходное состояние и, поступая на вход элемента И 25, разрешает запись в элемент 26 памяти результатов определения на- в исследуемом узле генерации. При возникновении очага генерации в любом месте испытуемого узла (см.

тельно, и на выходе элемента И 25, будет присутствовать потенциал низкого логического уровня. TaKtM обра- 25 зом, при поступлен}ш на второй вход элемента И 25 с внхода элемента 20 задержки сигнала разрешения записи результатов определения наличия генерации на информационный вход элемен-

фиг.2) в индуктивном датчике 28,, ко- 30 та памяти 26 поступит сигнал соответствующего уровня. В случае возникно™ зения устойчивой генерации элемент 26 памяти включает индикатор 27.

Формула изобретения

торый представляет собой антенну, выполненную в виде печатной индуктивности, рассчитанную на максимальную частоту переключения, логических элементов и расположенную с минимальным зазором от испытуемого узла, появляется сигнал, имеюп1ий емкостную и индуктивную составляющие. Изменение потенциала будет передаваться через емкость, образованную печатными проводниками испытуемого узла и антенной, на узел 21. Потенциал, наведенный емкостной составляющей, поступает синфазно на оба входа узла 21, кого- рый представляет собой, например, дифференциальный каскад, выполненный на транзисторах 30 и 31. Выходом каскада является резистор 32, с которого поч енциал через конденсатор 33 поступает на вход усилителя 23, где усиливается до уровня, необходимого для срабатывания элемента ИЛИ 24 Индуктивная составляющая сигнала появляется за счет взаимоиндукции печатных проводников испытуемого узла и антенны. Она выражается в появлении разности потенциалов на концах антенны в момент изменения тока в очаге генерации. Эта разность потенциалов

35

Устройство для контроля логических узлов по авт. св. К-- 1020829, отличающееся тем, что, с це40 лью повьшения достоверности контроля, в него введены индуктивньй датчик, блок электрического согла сования, элемент 1ШИ, второй формирователь импульсов, элемент И, элемент памяти,

45 индикатор и элемент задержки, причем выход первого форштрователя импульсов через элемент задержки соединен с установочным входом счетчика и первым входом элемента И, выход которого со50 единен с информационным входом элемента памяти, управляющий вход которого соединен с выходом элемента И- НЕ, а выход - с входом индикатора, второй вход элемента И через второй

55 формирователь импульсов соединен с выходом элемента ИЛИ, входы которого через блок электрического согласования соединены с выходами индуктивного датчика.

усиливается, дифференциальным каскадом и с резисторов 34 и 35 поступает на усилитель 22, где усиливается до уровня, достаточного для срабатывания элемента ИЛИ 24. Таким образом, если в испытуемом узле возникла устойчивая генерация, вызванная неисправностью типа короткое замыкание с обратными связями, на выходе формирователя 29 появится сигнал высокого логического уровня. Этот сигнал сохранится и после завершения переключений логических .элементов блока хранения эталонов, т,е„ и после истечения задержки времени, выработанной элементом 20 задержки. Если в испытуемом узле устойчивая генерация не возннк

и

тельно, и на выходе элемента И 25, будет присутствовать потенциал низкого логического уровня. TaKtM обра- 25 зом, при поступлен}ш на второй вход элемента И 25 с внхода элемента 20 задержки сигнала разрешения записи результатов определения наличия генерации на информационный вход элемен-

Формула изобретения

35

Устройство для контроля логических узлов по авт. св. К-- 1020829, отличающееся тем, что, с це40 лью повьшения достоверности контроля, в него введены индуктивньй датчик, блок электрического согла сования, элемент 1ШИ, второй формирователь импульсов, элемент И, элемент памяти,

45 индикатор и элемент задержки, причем выход первого форштрователя импульсов через элемент задержки соединен с установочным входом счетчика и первым входом элемента И, выход которого со50 единен с информационным входом элемента памяти, управляющий вход которого соединен с выходом элемента И- НЕ, а выход - с входом индикатора, второй вход элемента И через второй

55 формирователь импульсов соединен с выходом элемента ИЛИ, входы которого через блок электрического согласования соединены с выходами индуктивного датчика.

фа$.2

| Устройство для контроля логических узлов | 1982 |

|

SU1020829A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-07-15—Публикация

1986-11-19—Подача