cpus.i

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может быть использовано для контроля блоков памяти.

Цель изобретения - повышение быстродействия устройства.

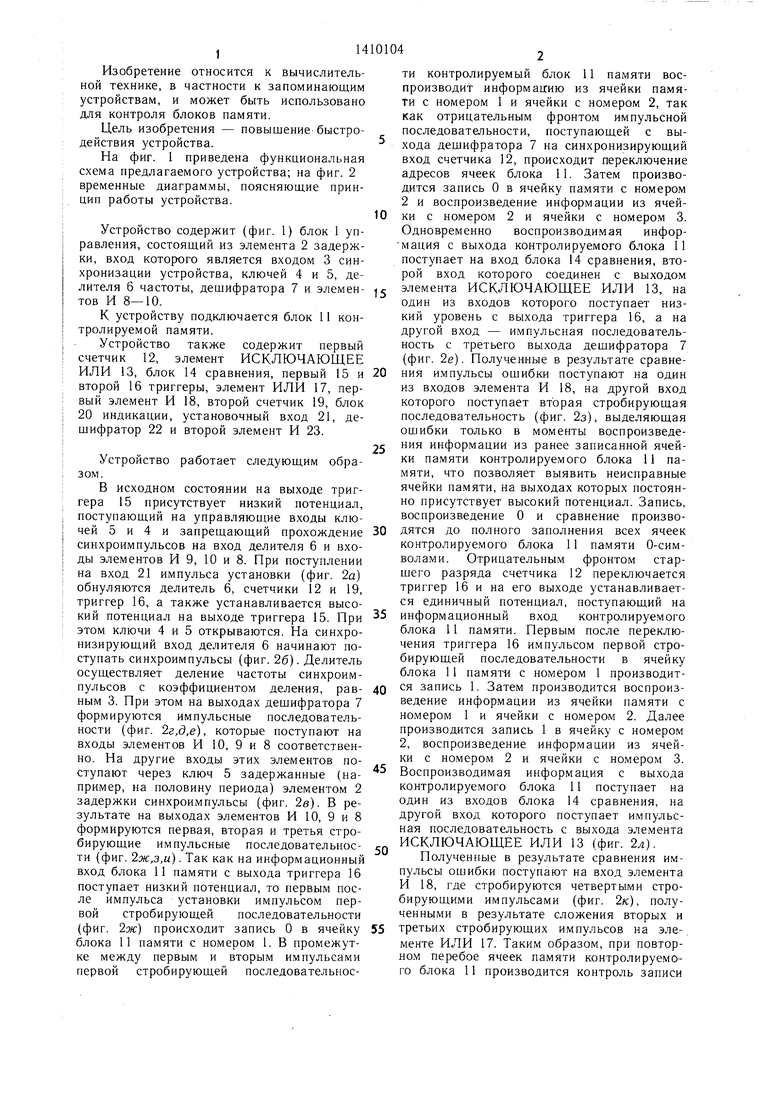

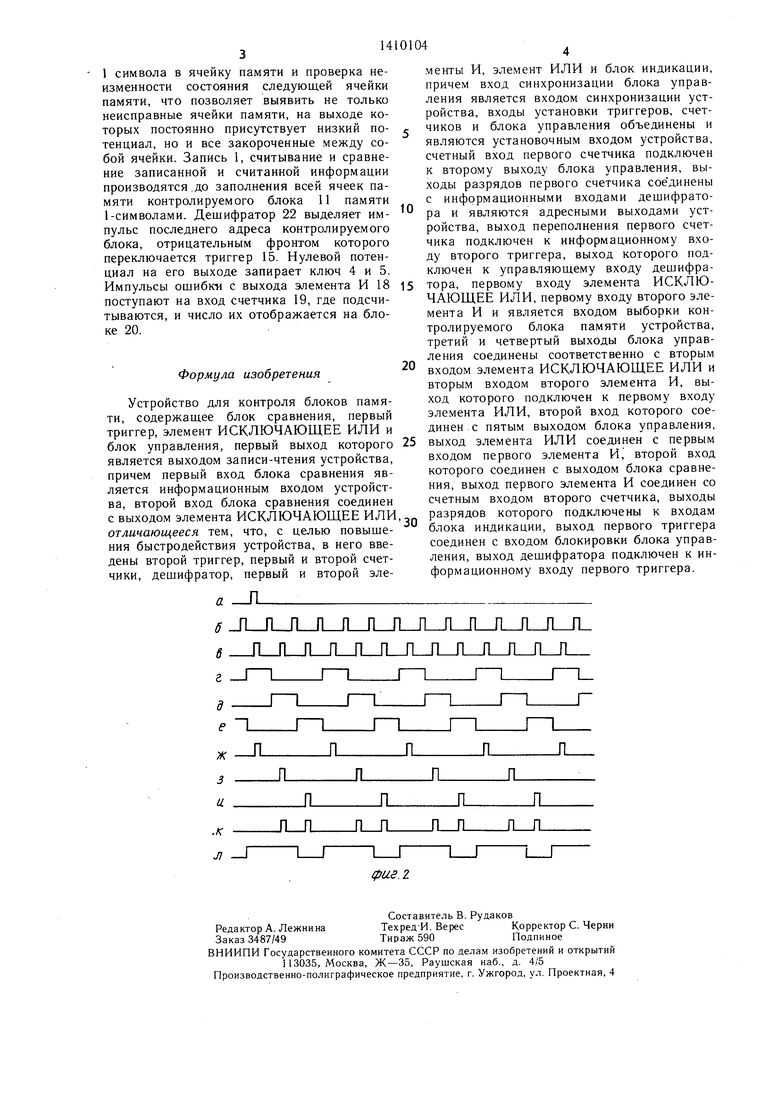

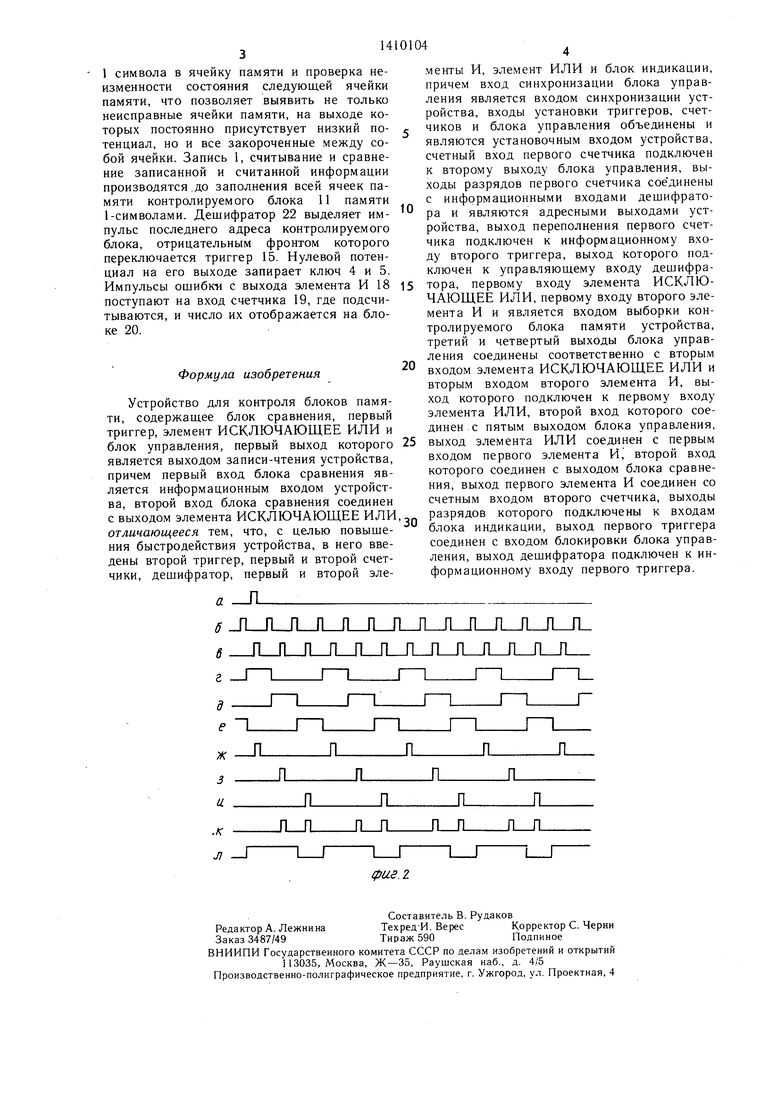

На фиг. 1 приведена функциональная схема предлагаемого устройства; на фиг. 2 временные диаграммы, поясняющие принцип работы устройства.

ти контролируемый блок 11 памяти воспроизводит информа1Гию из ячейки памяти с номером 1 и ячейки с номером 2, так как отрицательным фронтом импульсной последовательности, поступающей с выхода дешифратора 7 на синхронизирующий вход счетчика 12, происходит переключение адресов ячеек блока 11. Затем производится запись О в ячейку памяти с номером 2 и воспроизведение информации из ячейки с номером 2 и ячейки с номером 3. Одновременно воспроизводимая инфор- мация с выхода контролируемого блока 11 поступает на вход блока 14 сравнения, второй вход которого соединен с выходом

Устройство содержит (фиг. 1) блок 1 управления, состоящий из элемента 2 задержки, вход которого является входом 3 синхронизации устройства, ключей 4 и 5, делителя 6 частоты, дешифратора 7 и элемен- 5 элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13, на тов И 8-10.один из входов которого поступает низК устройству подключается блок 11 кон-кий уровень с выхода триггера 16, а на

тролируемой памяти.другой вход - импульсная последовательУстройство также содержит первыйность с третьего выхода дешифратора 7

счетчик 12, элемент ИСКЛЮЧАЮЩЕЕ(фиг. 2е). Полученные в результате сравнеИЛИ 13, блок 14 сравнения, первый 15 и 20 ния импульсы ощибки поступают на один второй 16 триггеры, элемент ИЛИ 17, пер-из входов элемента И 18, на другой вход

вый элемент И 18, второй счетчик 19, блок 20 индикации, установочный вход 21, де- щифратор 22 и второй элемент И 23.

которого поступает вторая стробирующая последовательность (фиг. 2з), выделяющая ошибки только в моменты воспроизведе- 25 ния информации из ранее записанной ячейки памяти контролируемого блока 11 памяти, что позволяет выявить неисправные ячейки памяти, на выходах которых постоянно присутствует высокий потенциал. Запись, воспроизведение О и сравнение произвоУстройство работает следующим образом.

которого поступает вторая стробирующая последовательность (фиг. 2з), выделяющая ошибки только в моменты воспроизведе- 25 ния информации из ранее записанной ячейки памяти контролируемого блока 11 памяти, что позволяет выявить неисправные ячейки памяти, на выходах которых постоянно присутствует высокий потенциал. Запись, воспроизведение О и сравнение произвоВ исходном состоянии на выходе триггера 15 присутствует низкий потенциал, ; поступающий на управляющие входы клю1 чей 5 и 4 и запрещающий прохождение 30 дятся до полного заполнения всех ячеек синхроимпульсов на вход делителя 6 и вхо-контролируемого блока И памяти 0-симI ды элементов И 9, 10 и 8. При поступленииволами. Отрицательным фронтом старi на вход 21 импульса установки (фиг. 2а)шего разряда счетчика 12 переключается

обнуляются делитель 6, счетчики 12 и 19,триггер 16 и на его выходе устанавливаеттриггер 16, а также устанавливается высо-ся единичный потенциал, поступающий на

кий потенциал на выходе триггера 15. При 5 информационный вход контролируемого этом ключи 4 и 5 открываются. На синхро-блока 11 памяти. Первым после переклюнизирующий вход делителя 6 начинают по-чения триггера 16 импульсом первой строступать синхроимпульсы (фиг. 26). Делительбирующей последовательности в ячейку

осуществляет деление частоты синхроим-блока 11 памяти с номером 1 производитпульсов с коэффициентом деления, рав- 40 запись 1. Затем производится воспроиз- ным 3. При этом на выходах дешифратора 7ведение информации из ячейки памяти с

формируются импульсные последовательности (фиг. 2г,д,е), которые поступают на входы элементов И 10, 9 и 8 соответственно. На другие входы этих элементов поступают через ключ 5 задержанные (например, на половину периода) элементом 2 задержки синхроимпульсы (фиг. 20). В результате на выходах элементов И 10, 9 и 8 формируются первая, вторая и третья стро45

номером 1 и ячейки с номером 2. Далее производится запись 1 в ячейку с номером 2, воспроизведение информации из ячейки с номером 2 и ячейки с номером 3. Воспроизводимая информация с выхода контролируемого блока 11 поступает на один из входов блока 14 сравнения, на другой вход которого поступает импульсная последовательность с выхода элемента

бирующие импульсные последовательное- сп ИСКЛЮЧАЮЩЕЕ ИЛИ 13 (фиг. 2л). ти (фиг. 2эс,з,ы). Так как на информационныйПолученные в результате сравнения импульсы ошибки поступают на вход элемента И 18, где стробируются четвертыми стро- бирующими импульсами (фиг. 2к), полученными в результате сложения вторых и

(фиг. 2ж) происходит запись О в ячейку 55 третьих стробирующих импульсов на эле-, блока 11 памяти с номером 1. В промежут-менте ИЛИ 17. Таким образом, при повторке между первым и вторым импульсамином перебое ячеек памяти контролируемопервой стробирующей последовательное-го блока 11 производится контроль записи

вход блока 11 памяти с выхода триггера 16 поступает низкий потенциал, то первым после импульса установки импульсом первой стробирующей последовательности

ти контролируемый блок 11 памяти воспроизводит информа1Гию из ячейки памяти с номером 1 и ячейки с номером 2, так как отрицательным фронтом импульсной последовательности, поступающей с выхода дешифратора 7 на синхронизирующий вход счетчика 12, происходит переключение адресов ячеек блока 11. Затем производится запись О в ячейку памяти с номером 2 и воспроизведение информации из ячейки с номером 2 и ячейки с номером 3. Одновременно воспроизводимая инфор- мация с выхода контролируемого блока 11 поступает на вход блока 14 сравнения, второй вход которого соединен с выходом

элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13, на один из входов которого поступает низния импульсы ощибки поступают на один из входов элемента И 18, на другой вход

которого поступает вторая стробирующая последовательность (фиг. 2з), выделяющая ошибки только в моменты воспроизведе- ния информации из ранее записанной ячейки памяти контролируемого блока 11 памяти, что позволяет выявить неисправные ячейки памяти, на выходах которых постоянно присутствует высокий потенциал. Запись, воспроизведение О и сравнение произво запись 1. Затем производится воспроиз- ведение информации из ячейки памяти с

номером 1 и ячейки с номером 2. Далее производится запись 1 в ячейку с номером 2, воспроизведение информации из ячейки с номером 2 и ячейки с номером 3. Воспроизводимая информация с выхода контролируемого блока 11 поступает на один из входов блока 14 сравнения, на другой вход которого поступает импульсменты И, элемент ИЛИ и блок индикации, причем вход синхронизации блока управления является входом синхронизации устройства, входы установки триггеров, счетчиков и блока управления объединены и являются установочным входом устройства, счетный вход первого счетчика подключен к второму выходу блока управления, выходы разрядов первого счетчика сое динены с информационными входами дешифратора и являются адресными выходами устройства, выход переполнения первого счетчика подключен к информационному входу второго триггера, выход которого подключен к управляющему входу дешифра1 символа в ячейку памяти и проверка неизменности состояния следующей ячейки памяти, что позволяет выявить не только неисправные ячейки памяти, на выходе которых постоянно присутствует низкий по- г тенциал, но и все закороченные между собой ячейки. Запись 1, считывание и сравнение записанной и считанной информации производятся.до заполнения всей ячеек памяти контролируемого блока И памяти 1-символами. Дешифратор 22 выделяет им- пульс последнего адреса контролируемого блока, отрицательным фронтом которого переключается триггер 15. Нулевой потенциал на его выходе запирает ключ 4 и 5.

Импульсы ошибка с выхода элемента И 18 15 тора, первому входу элемента ИСКЛЮ- поступают на вход счетчика 19, где подсчи-ЧАЮЩЕЕ ИЛИ, первому входу второго элемента И и является входом выборки контролируемого блока памяти устройства, третий и четвертый выходы блока управления соединены соответственно с вторым 20 входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и вторым входом второго элемента И, выход которого подключен к первому входу элемента ИЛИ, второй вход которого соединен с пятым выходом блока управления,

блок управления, первый выход которого 25 выход элемента ИЛИ соединен с первым является выходом записи-чтения устройства,входом первого элемента И; второй вход

причем первый вход блока сравнения является информационным входом устройства, второй вход блока сравнения соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены второй триггер, первый и второй счетчики, дешифратор, первый и второй элетываются, и число их отображается на блоке 20.

Формула изобретения

Устройство для контроля блоков памяти, содержащее блок сравнения, первый триггер, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и

30

которого соединен с выходом блока сравнения, выход первого элемента И соединен со счетным входом второго счетчика, выходы разрядов которого подключены к входам блока индикации, выход первого триггера соединен с входом блокировки блока управления, выход дешифратора подключен к информационному входу первого триггера.

менты И, элемент ИЛИ и блок индикации, причем вход синхронизации блока управления является входом синхронизации устройства, входы установки триггеров, счетчиков и блока управления объединены и являются установочным входом устройства, счетный вход первого счетчика подключен к второму выходу блока управления, выходы разрядов первого счетчика сое динены с информационными входами дешифратора и являются адресными выходами устройства, выход переполнения первого счетчика подключен к информационному входу второго триггера, выход которого подключен к управляющему входу дешифратора, первому входу элемента ИСКЛЮ- ЧАЮЩЕЕ ИЛИ, первому входу второго элевыход элемента ИЛИ соединен с первым входом первого элемента И; второй вход

которого соединен с выходом блока сравнения, выход первого элемента И соединен со счетным входом второго счетчика, выходы разрядов которого подключены к входам блока индикации, выход первого триггера соединен с входом блокировки блока управления, выход дешифратора подключен к информационному входу первого триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков памяти | 1986 |

|

SU1383449A1 |

| Устройство магнитной записи сигналов цифровой информации | 1983 |

|

SU1157566A1 |

| Устройство для контроля оперативной памяти | 1986 |

|

SU1401520A2 |

| Устройство тестового контроля цифровых блоков | 1985 |

|

SU1315982A1 |

| Устройство телеконтроля состояния стрелок и сигналов | 1986 |

|

SU1348252A1 |

| Устройство для контроля цифровых блоков памяти | 1985 |

|

SU1256101A1 |

| Устройство для контроля оперативной памяти | 1984 |

|

SU1226535A1 |

| Устройство для детектирования манипулированных по частоте и фазе сигналов воспроизведения цифровой магнитной записи | 1986 |

|

SU1327172A1 |

| Устройство для сопряжения с датчиками | 1989 |

|

SU1695286A1 |

| Устройство для воспроизведения цифровых сигналов с носителя магнитной записи | 1986 |

|

SU1352527A1 |

Изобретение относится к вычислитель-, ной технике, в частности к запоминающим устройствам, и может быть использовано для контроля блоков памяти. Цель изобретения - повышение быстродействия устройства. Устройство содержит блок 1 управления, в состав которого входят элемент 2 задержки, ключи 4 и 5, делитель 6 частоты, дешифратор 7, элементы И 8-10. Устройство также содержит счетчики 12 и 19, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 13, блок 14 сравнения, триггеры 15 и 16, элемент ИЛИ 17 элементы И 18 и 23, блок 20 индикации Устройство подключается к блоку 11 контролируемой памяти. 2 ил.

а 6 8 г

Л

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЗАПОМИНАЮЩИХМОДУЛЕЙ | 1972 |

|

SU428455A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для контроля блоков памяти | 1980 |

|

SU926725A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-07-15—Публикация

1986-06-09—Подача