ОЭ

сс

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный программируемый преобразователь код-фаза | 1990 |

|

SU1742998A1 |

| Многоканальное устройство ввода аналоговой информации | 1986 |

|

SU1403057A1 |

| Декодирующее устройство кода Рида-Соломона | 1988 |

|

SU1640830A1 |

| Селектор импульсов по длительности | 1988 |

|

SU1647876A1 |

| Устройство для приема последовательного кода | 1982 |

|

SU1089608A1 |

| Преобразователь параллельного кода в последовательный | 1985 |

|

SU1339896A1 |

| Преобразователь кодов | 1986 |

|

SU1438008A1 |

| Устройство для преобразования кодов с одного языка на другой | 1981 |

|

SU985793A1 |

| Устройство для уплотнения многоканальных сообщений с кодоимпульсной модуляцией | 1986 |

|

SU1365106A1 |

| Преобразователь последовательного кода в параллельный | 1987 |

|

SU1418911A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах для обработки цифровых данных. Изобретение позволяет без дополнительных аппаратурных затрат и нзменени11 структуры устройства преобразовывать параллельные коды произвольного вида, ЧТО обеспечивает расширение области .использования преобразователя. Преобразователь содержит счетчик I импульсов, два блока 2и 4 памяти, блок 3 сравнения кодов и блок 5 управления, состоящий из четырех триг. геров, четырех элементов, дешифратора, счетчика импульсов и генератора импульсов. 2 ил.

Фаг.1

Изобретение относится к вычислительной технике, а именно к преобразователям информации, и может быть яспользова но в устройствах для обра- Зотки цифровых данных.

Цель изобретения - упрощение пре- эбразователя и расширение области его использования за счет возможности преобразования параллельных кодов произвольного вида.

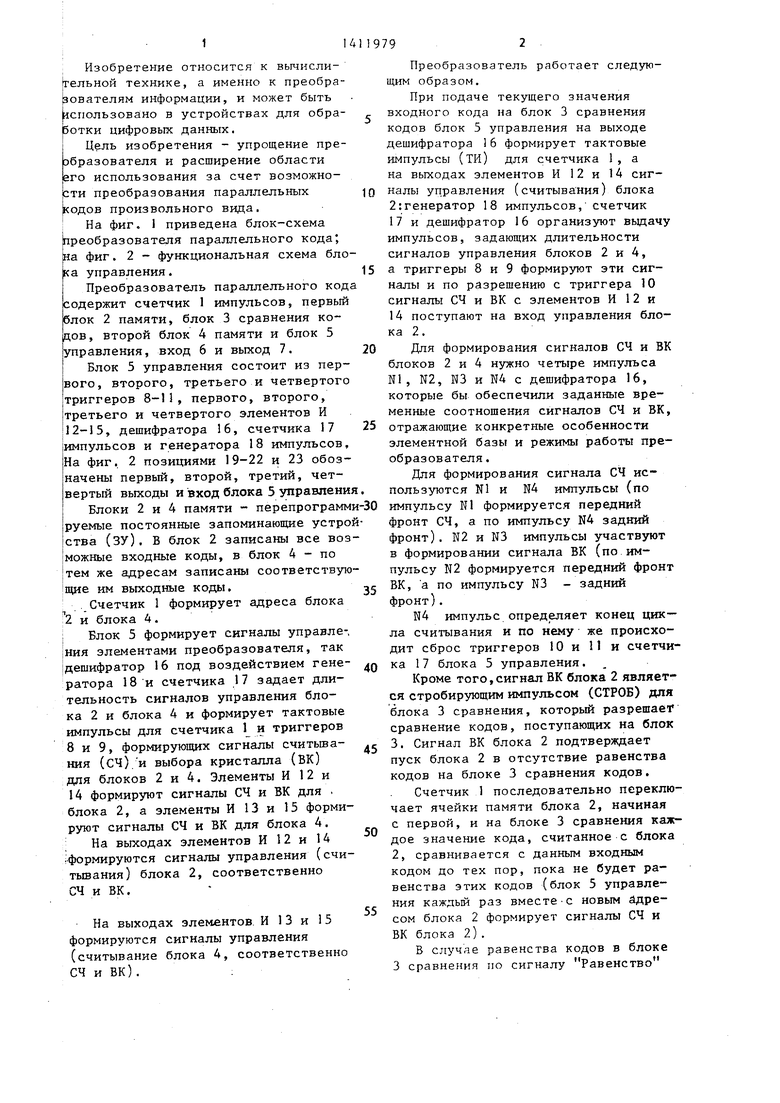

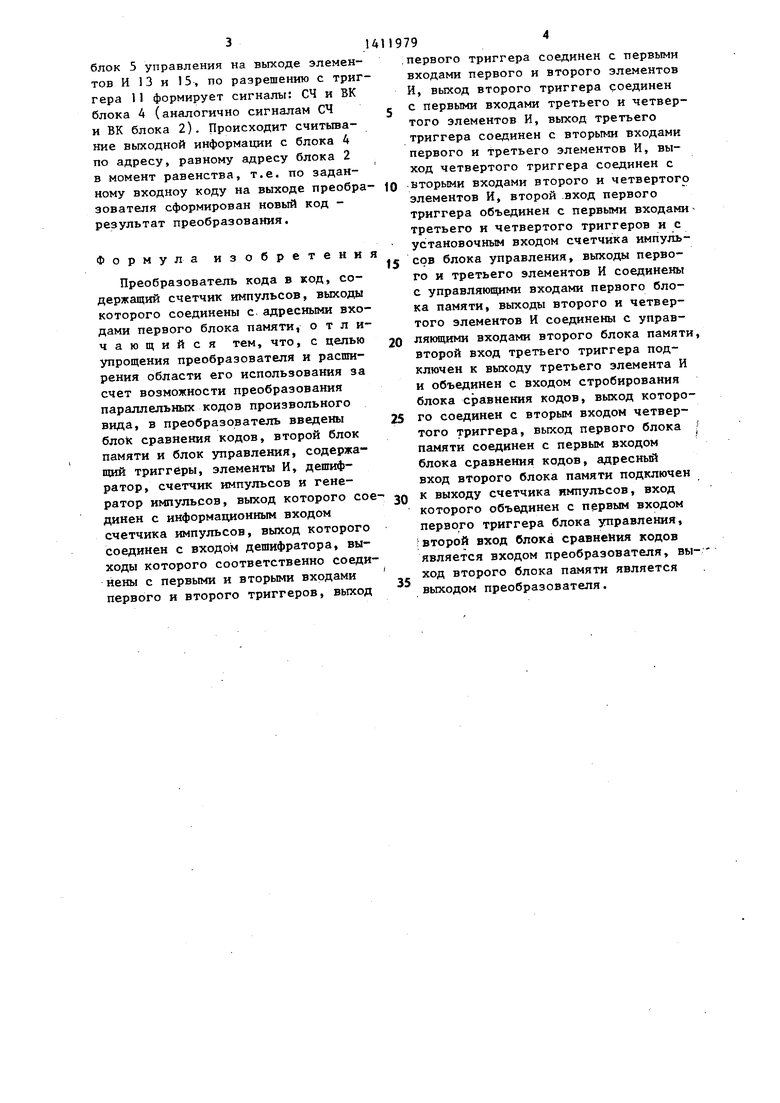

На фиг. 1 приведена блок-схема преобразователя параллельного кода; на фиг. 2 - функциональная схема блока управления.

Преобразователь параллельного код содержит счетчик 1 импульсов, первый блок 2 памяти, блок 3 сравнения ко- цов, второй блок 4 памяти и блок 5 управления, вход 6 и выход 7.

Блок 5 управления состоит из первого, второго, третьего и четвертого триггеров 8-П, первого, второго, третьего и четвертого элементов И 12-15, дешифратора 16, счетчика 17 импульсов и генератора 18 импульсов. На фиг. 2 позициями 19-22 и 23 обозначены первый, второй, третий, четвертый выходы и вход блока 5 управлени

Блоки 2 и 4 памяти перепрограмми-30 импульсу N1 формируется передний

руемь:е постоянные запоминающие устроства (ЗУ). В блок 2 записаны все воз можные входные коды, в блок 4 - по |тем же адресам записаны соответствую щие им выходные коды.

. Счетчик 1 формирует адреса блока 2 и блока 4.

i Блок 5 формирует сигналь: управле- |ния элементами преобразователя, так дешифратор 16 под воздействием генератора 18 и счетчика 17 задает длительность сигналов управления блока 2 и блока 4 и формирует тактовые импульсы для счетчика 1 и триггеров 8 и 9, формирующих сигналы считьша- ния (СЧ) и выбора кристалла (ВК) для блоков 2 и 4. Элементы И 12 и 14 формируют сигналы СЧ и ВК для . блока 2, а элементы И 13 и 15 формируют сигналы СЧ и ВК для блока 4. ; На выходах элементов И 12 и 14 .формируются сигналы управления (счи- тьюания) блока 2, соответственно СЧ и ВК.

На выходах элементов. И 13 и 15 формируются сигналы управления (считывание блока 4, соответственно СЧ и ВК).:

Преобразователь работает следующим образом.

При подаче текущего значения входного кода на блок 3 сравнения кодов блок 5 управления на выходе дешифратора 6 формирует тактовые импульсы (ТИ) для счетчика 1, а на выходах элементов И 12 и 14 сигналы управления (считывания) блока 2:генератор 18 импульсов, счетчик 17 и дешифратор 16 организуют вьщачу импульсов, задающих длительности сигналов управления блоков 2 и 4, а триггеры 8 и 9 формируют эти сигналы и по разрешению с триггера 10 сигналы СЧ и ВК с элементов И 12 и 14 поступают на вход управления блока 2.

Для формирования сигналов СЧ и ВК блоков 2 и 4 нужно четыре импульса N1, N2, N3 и N4 с дешифратора 16, которые бы обеспечили заданные временные соотношения сигналов СЧ и ВК отражающие конкретные особенности элементной базы и режимы работы преобразователя.

Для формирования сигнала СЧ используются N1 и N4 импульсы (по

5

0

5

0

5

фронт СЧ, а по импульсу N4 задний фронт). N2 и N3 импульсы участвуют в формировании сигнала ВК (по импульсу N2 формируется передний фронт ВК, а по импульсу N3 - задний фронт).

N4 импульс определяет конец цикла считывания и по нему же происходит сброс триггеров 10 и 11 и счетчика 17 блока 5 управления.

Кроме того,сигнал ВК блока 2 является стробирующим импульсом (СТРОБ) для блока 3 сравнения, который разрешает сравнение кодов, поступающих на блок 3. Сигнал ВК блока 2 подтверждает пуск блока 2 в отсутствие равенства кодов на блоке 3 сравнения кодов.

Счетчик 1 последовательно переключает ячейки памяти блока 2, начиная с первой, и на блоке 3 сравнения каждое значение кода, считанное с блока 2, сравнивается с данным входным кодом до тех пор, пока не будет равенства этих кодов (блок 5 управления каждый раз вместе-с новым адресом блока 2 формирует сигналы СЧ и ВК блока 2).

В случае равенства кодов в блоке 3 сравнения по сигналу Равенство

блок 5 управления на выходе элементов И 13 и 15, по разрешению с триггера 11 формирует сигналы: СЧ и ВК блока А (аналогично сигналам СЧ и ВК блока 2). Происходит считывание выходной информации с блока 4 по адресу, равному адресу блока 2 в момент равенства, т.е. по заданному входноу коду на выходе преобразователя сформирован новый код - результат преобразования.

Формула изобретени

Преобразователь кода в код, содержащий счетчик импульсов, выходы которого соединены с адресными входами первого блока памяти, отличающийся тем, что, с целью упрощения преобразователя и расширения области его использования за счет возможности преобразования параллельных кодов произвольного вида, в преобразователь введены блок сравнения кодов, второй блок памяти и блок управления, содержащий триггеры, элементы И, дещиф- ратор, счетчик импульсов и генератор импульсов, выход которого соединен с информационным входом счетчика импульсов, выход которого соединен с входом дешифратора, выходы которого соответственно соединены с первыми и вторыми входами первого и второго триггеров, выход

:первого триггера соединен с первыми входами первого и второго элементов И, выход второго триггера соединен с первыми входами третьего и четвертого элементов И, выход третьего триггера соединен с вторыми входами первого и третьего элементов И, выход четвертого триггера соединен с вторыми входами второго и четвертого элементов И, второй вход первого триггера объединен с первыми входами - третьего и четвертого триггеров и с установочным входом счетчика импульсов блока управления, выходы первого к третьего элементов И соединены с управляющими входами первого блока памяти, выходы второго и четвертого элементов И соединены с управ- лякицими входами второго блока памяти, второй вход третьего триггера подключен к выходу третьего элемента И и объединен с входом стробирования блока сравнения кодов, выход которого соединен с вторым входом четвертого триггера, выход первого блока : памяти соединен с первым входом блока сравнения кодов, адресный вход второго блока памяти подключен к выходу счетчика импульсов, вход которого объединен с первым входом первого триггера блока управления, г второй вход блока сравнения кодов является входом преобразователя, вы- ход второго блока памяти является выходом преобразователя.

Фив. 2

| Авторское свидетельство СССР № 1162052, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1167737A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-07-23—Публикация

1986-04-23—Подача