CD 41

/«

СО

11

Изобретение относится к автоматике и цифро.;ой вычислительной технике и может быть использовано в многоканальных информационно-измерительных системах с цифровой обработкой данных.

Цель изобретения - упрощение структурной схемы преобразователя и уменьшение количества связей.

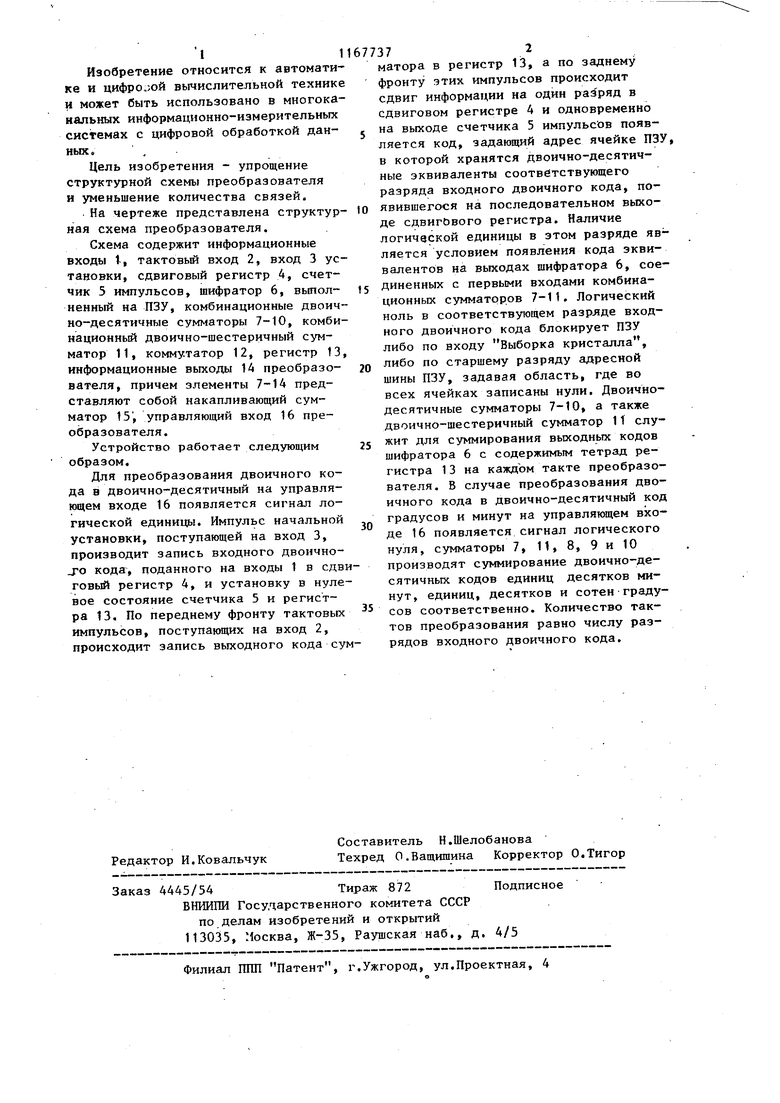

На чертеже представлена структурная схема преобразователя.

Схема содержит информационные входы t, тактовый вход 2, вход 3 установки, сдвиговый регистр 4, счетчик 5 импульсов, шифратор 6, выполненный на ПЗУ, комбинационные двоично-десятичные сумматоры 7-10, комбинационный двоично-шестеричный сумматор 11, коммутатор 12, регистр 13, информационные выходы 14 преобразователя, причем элементы 7-14 представляют собой накапливающий сумматор 15, управляющий вход 16 преобразователя.

Устройство работает следующим образом.

Для преобразования двоичного кода в двоично-десятичный на управляющем входе 16 появляется сигнал логической единицы. Импульс начальной установки, поступающей на вход 3, производит запись входного двоичного кода, поданного на входы 1 в сдвиговый регистр 4, и установку в нулевое состояние счетчика 5 и регистра 13. По переднему фронту тактовых импульсов, поступающих на вход 2, происходит запись выходного кода сум677372

матора в регистр 13, а по заднему фронту этих импульсов происходит сдвиг информации на один разряд в сдвиговом регистре 4 и одновременно , на выходе счетчика 5 импульсов появляется код, задающий адрес ячейке ПЗУ, в которой хранятся двоично-десятичные эквиваленты соответствующего разряда входного двоичного кода, появившегося на последовательном выходе сдвиг&вого регистра. Наличие логической единицы в этом разряде является условием появления кода эквивалентов на выходах шифратора 6, соединенных с первыми входами комбинационных сумматоров 7-11. Логический ноль в соответствующем разряде входного двоичного кода блокирует ПЗУ

либо по входу Выборка кристалла, либо по старшему разряду адресной шины ПЗУ, задавая область, где во всех ячейках записаны нули. Двоичнодесятичные сумматоры 7-10, а также двоично-шестеричный сумматор 11 служит для суммирования выходных кодов шифратора 6 с содержимым тетрад регистра 13 на каждом такте преобразователя. В случае преобразования двоичного кода в двоично-десятичный код градусов и минут на управляющем входе 16 появляется сигнал логического нуля, сумматоры 7, 11, 8, 9и 10 производят суммирование двоично-десятичных кодов единиц десятков минут, единиц, десятков и сотен градусов соответственно. Количество тактов преобразования равно числу разрядов входного двоичного кода.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода вдВОичНО-дЕСяТичНый КОд | 1979 |

|

SU849199A1 |

| Преобразователь двоичных кодов в двоично-десятичные | 1984 |

|

SU1200428A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1042010A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283979A1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1985 |

|

SU1396280A2 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1501276A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1280702A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1221757A1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1986 |

|

SU1349008A2 |

| Преобразователь двоичного кода в двоично-десятичный | 1978 |

|

SU864278A1 |

ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В ДВОИЧНО-ДЕСЯТИЧНЫЙ, содержащий шифратор и .накапливающий сумматор, входы которого соединены с выходами шифратора, а выходы являются информационными выходами преобразователя, отличающийся тем, что, с целью упрощения, он содержит счетчик импульсов и сдвиговый регистр, а шифратор вьтолнен на ПЗУ, причем информационные входы преобразователя соединены с разрядными входами сдвигового регистра, выход которого подключён к входу считывания содержимого адреса ПЗУ, входы задания адреса которого соединены с выходом счетчика импульсов, тактовый вход которого и одноименный вход сдвигового регистра соединены с тактовьм входом преобразователя, управлякирй вход которого соединен с управляющими входами ПЗУ и накапливающего сумматора, установочный вход которого и установочные входы счетчика импуль(Л сов и сдвигового регистра подключены к входу установки преобразователя.

| Преобразователь двоичного кода вдВОичНО-дЕСяТичНый | 1979 |

|

SU851394A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Преобразователь двоичного кода вдВОичНО-дЕСяТичНый КОд | 1979 |

|

SU849199A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-07-15—Публикация

1984-01-02—Подача