1чЭ

U

ванне в момент прихода импульсов частоты записио По окончании импульса частоты записи элемент И 9 закры- вается и начинает срабатывать элемент 17, время срабатывания которого равно времени срабатывания элементов И 15 и ИЛИ 13, Таким образом, исчезновение сигналов управления по входам Запись-считывание и Выбор

кристашш происходит одновременно. В режиме считыняния для блока 3 импульсы считывания с другого выхода генератора 6 проходят через открытый элемент И 11 и через элемент ИЛИ 13. на вход Выбор кристалла блока 3. Аналогичным образом работает в режимах записи или считывания блок 4. 1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство буферной памяти | 1987 |

|

SU1494010A1 |

| Устройство для управления доступом к памяти | 1986 |

|

SU1376089A1 |

| Устройство для управления обменом информацией процессора с памятью | 1988 |

|

SU1587525A1 |

| Устройство буферной памяти | 1990 |

|

SU1805475A1 |

| Устройство для управления обменом процессора с памятью | 1989 |

|

SU1603393A2 |

| Устройство для управления обменом процессора с памятью | 1988 |

|

SU1667087A1 |

| Устройство для сопряжения процессора с памятью | 1989 |

|

SU1742823A1 |

| Устройство для управления доступом к памяти | 1985 |

|

SU1282147A1 |

| Устройство для управления обменом информацией процессора с памятью | 1986 |

|

SU1325494A1 |

| Буферное запоминающее устройство | 1989 |

|

SU1644148A1 |

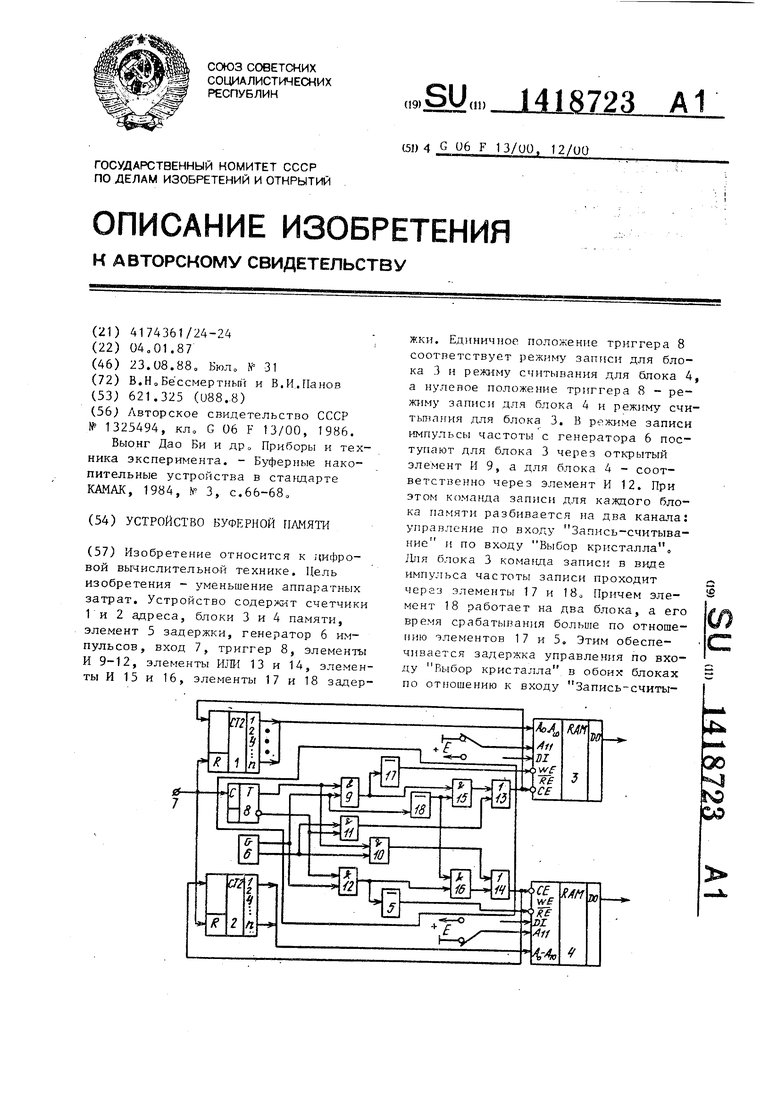

Изобретение относится к цифровой вычислительной технике. Цель изобретения - уменьшение аппаратных затрат. Устройство содержит счетчики 1 и 2 адреса, блоки 3 и 4 памяти, элемент 5 задержки, генератор 6 импульсов, вход 7, триггер 8, элементы И 9-12, элементы ИЛИ 13 и 14, элементы И 15 и 16, элементы 17 и 18 задержки. Единичное положение триггера 8 соответствует режиму для блока 3 и реж)му считывания для блока 4, а нулевое положение триггера 8 - режиму записи для блока 4 и режиму счи- тьтл1гия для блока 3. В режиме записи импульсы частоты с генератора 6 поступают для блока 3 через отктзытый элемент И 9, а для блока 4 - соответственно через элемент И 12. При этом команда записи для каждого блока памяти разбивается на два канала; управление по входу Запись-считывание и по входу Выбор кристалла Лля блока 3 команда записи в вид.е импульса частоты записи проходит через элементы 17 и 18о Причем элемент 18 работает на два блока, а его время срабатывания больше по отношению элементов 17 и 5. Этим обеспечивается задержка управления по входу Выбор кристалла в обоих блоках по отношению к входу У

1

Изобретение относится к 1щфровой вычислительной технике, в частности к устройствам для сопряжения с памятью, и может быть использовано для построения систем с быстродействующей памятью.

Цель изобретения - уменьшение аппаратных затрат за счет упрощения алгоритма сбора данных,

На чертеже представлена структурная схема предлагаемого устройства.

Устройство содержит счетчики 1 и

2адреса, блоки 3 и 4 памяти, элемент

5 задержки, генератор 6 импульсов, вход 7 запуска устройства, триггер 8, элементы И 9-12, элементы ИЛИ 13 и 14 элементы И 15 и 16, элементы 17 и 18 задержкИо

Устройство работает следующим образом.

Информация, подлежащая записи по входу и 1 в блоки 3 и 4, привязывается к сигналу запуска по входу 7 и, при необходимости, может быть синх- ронизирована импульсами частоты записи, поступающими с первого выхода генератора 6 (не показано).

Сигнал запуска по входу 7 используется также для синхрониэатщи счет- чиков 1 и 2,

Информация, считываемая из блоков

3и 4, может быть объединена в один канал через элемент ИЛИ и, при необходимости, синхронизирована импульсами частоты считывания с задержкой на время срабатывания блоков 3 и 4, для этой цели может быть, использован тщу- щий мультивибратор, запускаемый импульсами частоты считывания,

Синхронизация входной и выходной информации может быть реализована на триггерах.

0

5

О

.

5

Единичный выход триггера 8 соответствует режиму записи для блока 3 и режиму считывания для блока 4, а нулевой выход триггера 8 соответству-- ет режиму считывания для блока 3 и режиму записи для блока 4,

В режиме записи информации для блоков 3 и 4 импульсы частоты записи с генератора 6 поступают через соответственно открытые элементы И 9 и 12о При этом команда записи для каждого блока памяти разбивается на два канала: управление по входу Запись- считывание и по входу Выбор кристалла. Для блока 3 команда записи в виде импульсной частоты записи проходит через элементы 17 и 18, причем время срабатывания элемента 18 боль- ще времени срабатывания элемента 17, этим обеспечивается задержка управления по входу Выбор кристалла по отношению к входу Запись-считывание в момент прихода импульса частоты за писи с выхода генератора 6, По окончании импульса частоты записи эле( мент И 9 закрывается и начинает срабатывать элемент 17, время срабатывания которого равно времени срабатывания элементов И 15 и ИЛИ 1 3, таким образом исчезновение сигналов управления по входам Запись-считывание и Выбор кристалла происходит одновременно,

В режиме считывания для блока 3 импульсы частоты считьгоания с другого выхода генератора 6 проходят через открытый элемент И 11 и через элемент ИЛИ 13 на вход Выбор кристалла блока 3.

Аналогичньш образом работает в режиме записи или считывания блок 4„

31

Если в гфоцессе работы поступает информация об искажении достоверности информации от блока контроля, то этот сигнал можно использовать для перевода блоков 3 или 4 в работу по резервной зоне, которая подключается к работе сменой потенциала на входе старшего адресного разряда,

Смена адреса памяти в блоках 3 и 4 происходит по спаду импульсов на входах Выбор кристалла, которые с элементов ШШ 13 и 14 поступают в соответствующие счетчики 1 и 2 как в режиме записи, так и в режиме считывания.

Формула изобретения

Устройство буферной памяти, содержащее два счетчика адреса, два блока памяти, триггер, шесть элементов И, два элемента ИЛИ, вход синхронизации триггера является входом запуска устройства и соединен с входами сброса первого и второго счетчиков адреса, выходы первого и второго счетчиков адреса соединены с входами младших разрядов адреса первого и второго блоков памяти соответственно, прямой выход триггера соединен с первыми входами первого и второго элементов И, инверсный выход триггера соединен с первыми входами третьего и четвертого элементов И, выходы первого и четвертого элементов И соединены с первыми входами пятого и шестого элементов И, соответственно, выходы пятого и шестого элементов И соединены

5

8723

с первыми нходами первого и второго элементов ИЛИ соответственно, выходы третьего и второго элементов И соединены с вторыми входами первого и второго элементов ШШ соответственно, выход первого элемента ИЛИ соединен с входом Выборки кристалла первого блока памяти и счетным входом первого Q счетчика адреса, выход второго элемента ИЛИ соединен с входом Выборка кристалла второго блока памяти и счетным входом второго счетчика адреса, информационные входы первого и второго блоков памяти являются первым и вт6|рым информационными входами устройства, выходы блоков памяти образуют информационньй выход устройства, отличающееся тем, что, с целью уменьшения аппаратных затрат, в него введены три элемента задержки и генератор импульсов, первьпЧ выход генератора импульсов соед1-гаен с вторыми входами первого и четвертого элементов И и через первьп элемент задержки - с вторыми входами пятого и шестого элементов И, второй выход генератора импульсов соединен с вторыми входами второго и третьего элементов И, выход первого элемента И соединен через второй элемент задержки с входом чтения-записи первого блока памяти, выход четвертого элемента И соединен через третий элемент задержки с входом чтения-записи второго блока памяти, входы старших разрядов адреса первого и второго блоков памяти являются входами резервирования блоков памяти устройства.

0

5

0

5

| Устройство для управления обменом информацией процессора с памятью | 1986 |

|

SU1325494A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Выонг Дао Би и др Приборы и техника эксперимента | |||

| - Буферные накопительные устройства в стандарте КАМАК, 1984, № 3, с.66-68„ | |||

Авторы

Даты

1988-08-23—Публикация

1987-01-04—Подача