Изобретение относится к области цифровой вычислительной техники, в частности к буферным накопительным устройствам, позволяющим эффективно использовать ЭВМ при вводе информации, и может быть использовано в системах обработки потоков информации, а также для построения процессорных систем с быстрой памятью.

Цель изобретения - повышение быстродействия устройства.

В устройстве переключение блоков памяти происходит после того, как из какого-либо блока памяти будет считана вся информация, занесенная туда в режиме записи, т.е. переключение происходит при обнулении блока памяти, находящегося в режиме счи- тывания, а не при заполнении блока памяти, находящегося в режиме записи. Признаком обнуления блока памяти является считывание из него приэна- jKa последнего слова, который записывается в блок памяти непосредственно перед моментом переключения блоков памяти.

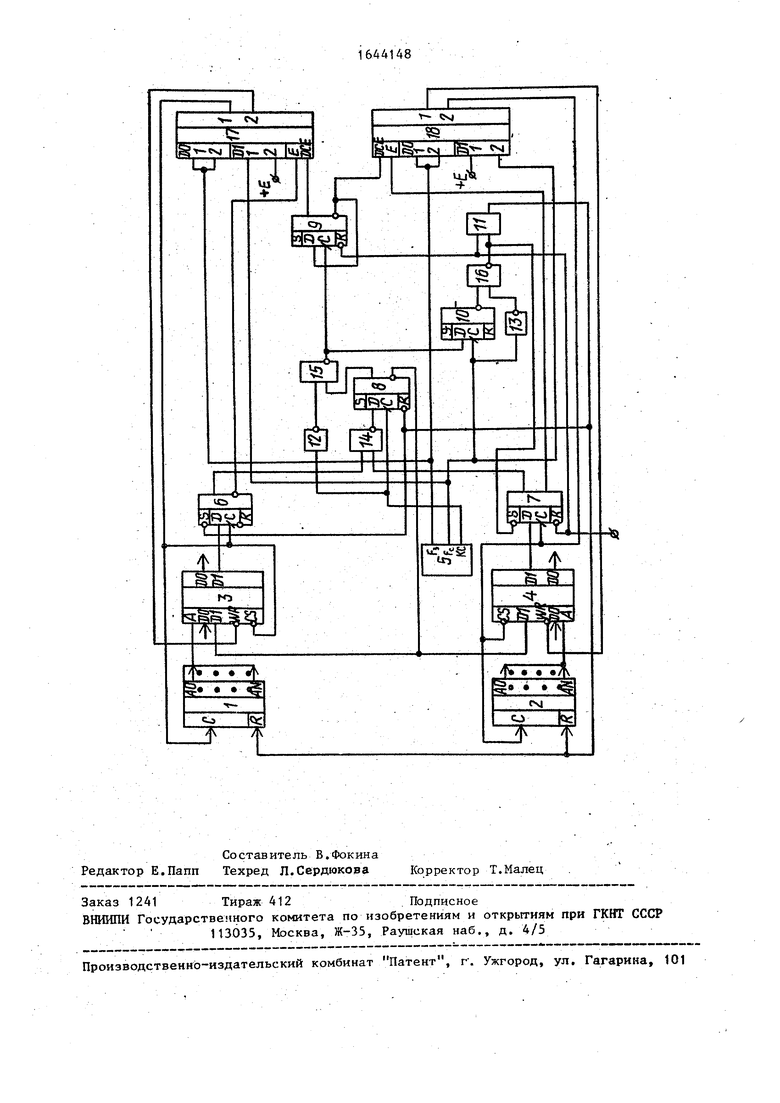

На чертеже показана схема устройства.

Устройство содержит два счетчика 1 и 2 адреса, два блока 3 и 4 памяти, генератор 5 импульсов и схему управления, включающую в себя триггеры 6-tO, элемент И 11, инверторы 12 и 13, элементы И-НЕ 14-16 и два коммутатора 17 и 18.

Устройство работает следующим образом.

При отсутствии сигнала Пуск обнуляются счетчики 1 и 2 адреса, триггеры 7-9, триггер 6 устанавливается в единичное состояние. Низкий потен- циал с прямого выхода триггера 9 поступает на адресный вход коммутатора 17, в результате чего импульсы записи, поступающие на первый и второй входы коммутатора 17с генератора 5,

(Л

о

Ј

4

Јь

00

проходят на выходы коммутатора 1 7 и подаются на счетчик 1 адреса, блок 3 памяти и триггер 6, т.е. низший потенциал на прямом выходе триггера 9 соответствует режиму записи в блок 3 памяти, а высокий потенциал с инверсного выхода триггера 9 поступает на адресный вход коммутатора 18, что соответствует выбору третьего входа коммутатора 18, на котором присутствует высокий потенциал, и четвертого входа коммутатора 18, на который поступают импульсы считывания с генератора 5, что соответствует режиму счи- тывания из блока 4 памяти. Однако высокий потенциал с инверсного выхода триггера 7 поступает на управляющий вход коммутатора 18 и запрещает прохождение на выходы коммутатора 18 управляющих сигналов с третьего и четвертого входов. Поэтому считывание из блока 4 памяти не происходит. Такое состояние устройства является исходным к приходу сигнала Пуск, т.е. устройство готово производить запись поступающей информации в блок 3 памяти, так как в блоке 4 памяти отсутствует информация, он находится

практически в отключенном состоянии

и считывание из него не происходит.

После прихода сигнала Пуск информация, подлежащая записи в блок 3 памяти, привязывается к сигналу Пуск и синхронизируется частотой записи Р с генератора 5. Импульсы записи с выхода коммутатора 17 поступают в блок памяти одновременно с импульсами выбора блока памяти, благодаря чему становится возможным обойтись без сложной схемы формирования временной диаграммы, содержащей элементы задержки. Импульсы выбора блока 3 памяти в то же время являются импульсами модификации счетчика адреса 1, из- менение состояния которого происходит по заднему фронту импульса выбора блока памяти.

Таким образом, информация записывается в блок 3 памяти до прихода сигнала Конец слова (КС). Необходимость сигнала КС обуславливается тем, что при последовательно-параллельной передаче информации необходимо инициализировать каждое слово во избежание потерь информации. В случае если длина передаваемого слова соответствует информационной разрядности блока памяти, сигналом КС сопровож

Q Q 5

0

40

.,

50

55

дается каждая посылка записываемой информации. Переключение блоков памяти по сигналу КС позволяет избежать ситуации, при которой часть записанного слова находится в одном блоке памяти, а часть в другом.

При поступлении на вход устройства сигнала КС триггер 8 устанавливается в высокое состояние, так как на вход элемента И-НЕ 14 поступает потенциал низкого уровня с выхода триггера 7. По переднему фронту сигнала КС формируется признак последнего слова на инверсном выходе триггера 8, который записывается в блок 3 памяти по вхо- ДУ D1.

По.заднему фронту сигнала КС триггер 9 изменяет свое состояние и на прямом выходе триггера 9 устанавливается высокий потенциал, который поступает на адресный вход коммутатора 17. В результате этого на выход коммутатора 17 поступают сигналы с третьего и четвёртого входов коммутатора. Низкий потенциал с инверсного выхода триггера 9 поступает на адресный вход коммутатора 18, благодаря чему становится возможным прохождение сигналов с первого и второго входов коммутатора 18 на его выходы. Это состояние устройства соответствует режиму записи в блок 4 памяти и режиму считывания из блока 3 памяти.

Схема сброса, построенная на триггере 10 и элементах 11,13 и 16, t формирует импульс сброса, привязанный к частоте считывания, устанавливающий триггеры 6 и 7 в высокое состояние, обнуляющий счетчик 1 и 2 и устанавливающий триггер 8 в низкое состояние. В такое исходное положение устройство переходит всякий раз после переключения блоков памяти.

Информация, подлежащая записи в блок 4 памяти, записывается аналогично тому, как она записывалась в блок 3 памяти. Однако прекращение записи происходит по сигналу КС лишь тогда, когда полностью Считывается информация, записанная в блок 3 памяти, о чем свидетельствует считывание из блока 3 памяти с выхода D1 признака последнего записанного слова. Это происходит следующим образом.

В процессе считывания из блока 3 памяти на вход разрешения записи блока 3 с коммутатора 1 7 поступает высокий потенциал,удерживающий блок памяти в

режиме считывания. Импульсы выбора блока памяти, формирующиеся по частоте считывания Fc, одновременно поступают на счетчик 1 адреса и триггер 6, на котором фиксируется наличие признака последнего, записанного в блок 3, слова. При достижении счетчиком 1 адреса, по которому записано последнее слово в блок 3, на выходе D1 блока 3 появляется низкий потенциал - признак последнего слова, который задним фронтом импульса выбора блока памяти фиксируется на триггере 6, Сигнал с прямого выхода триггера 6 поступает на элемент И-НЕ 14 и устанавливает на входе D триггера 8 высокий потенциал, подготавливая схему к переключению. Высоким потенциалом с инверсного выхода триггера 6, поступающим на управляющий вход коммута- трра 17, блокируется выдача сигналов выбора блока 3 памяти и, следовательно, сигналов модификации счетчика .1 адреса через коммутатор 17. С приходом сигнала КС блоки памяти переключаются и схема работает так, как описано выше.

Информация, считываемая из блоков 3 и 4 памяти, может быть объединена в один канал при помощи коммутатора, управляемого триггером 9 или через элементы ИЛИ, и синхронизирована частотой считывания.

Формула изобретения Буферное запоминающее устройство, содержащее два счетчика адреса, два блока памяти, первый триггер, генератор импульсов и коммутаторы, причем выходы первого и второго счетчиков адреса соединены с адресными входами первого и второго блоков памяти соответственно, информационные входы первого и второго счетчиков адреса соединены соответственно с первым и вторым выходами первого и второго коммутаторов, второй и первый выходы которых соединены с входами Выбор кристалла и разрешения записи первого и второго блоков памяти соответственно, прямой выход первого триггера соединен с первым управляющим входом первого коммутатора, инверсный выход , первого триггера соединен с первым управляющим входом второго коммутатора, первый выход генератора импульсов соединен с первыми информационными входами коммутаторов, второй

5

выход генератора импульсов соединен с вторыми информационными входами коммутаторов, первый и второй информационные входы блоков памяти являются соответственно первым и вторым информационными входами устройства, первый и второй выходы блоков памяти являются информационными выходами устройст- ва, отличающееся тем, что, с целью повышения быстродействия, в устройство введены триггеры с второго по пятый, три элемента И-НЕ, два инвертора и элемент И, выход которого соединен с обнуляющими входами счетчиков адреса и четвертого триггера и с установочным входом второго триггера, информационные входы второго и третьего триггеров соединены с вторыми выходами блоков памяти, первый и второй входы первого элемента И-НЕ подключены к прямым выходам второго и третьего триггеров, инверсные выходы которых соединены с вторыми управляющими входами первого и второго коммутаторов соответственно, выход первого элемента И-НЕ соединен с информационным входом четвертого триггера, вход синхронизации которого соединен с входом первого инвертора и третьим выходом генератора импульсов, выход инвертора подключен к первому входу второго элемента И-НЕ, второй вход которого соединен с прямым выходом четвертого триггера, инверсный выход которого соединен с вторыми информационными входами блоков памяти, выход второго элемента И-НЕ соединен с входом синхронизации первого триггера и информационным входом пятого триггера, вход синхронизации которого и вход второго инвертора объединены и подключены к второму выходу генератора импульсов, инверсный выход пятого триггера и выход второго инвертора соединены соответственно с первым и вторым входами третьего элемента И-НЕ, выход которого соединен с установочным входом третьего триггера и с вторым входом элемента И, первый вход которого соединен с обнуляющими входами первого и третьего триггеров и является входом запуска устройства, входы синхронизации второго и третьего триггеров подключены к первому выходу первого коммутатора и второму выходу второго коммутатора соответственно.

0

5

0

5

0

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля качества проводного монтажа | 1983 |

|

SU1108466A1 |

| Устройство для регистрации цифровой информации | 1986 |

|

SU1386915A2 |

| Буферное запоминающее устройство | 1978 |

|

SU942132A1 |

| Устройство для контроля инкубаторов | 1983 |

|

SU1212394A1 |

| Устройство для сопряжения ЭВМ с факсимильным аппаратом | 1988 |

|

SU1524060A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1985 |

|

SU1437907A1 |

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

| Устройство для управления обращением к общей памяти | 1987 |

|

SU1495804A1 |

| Устройство для обнаружения ошибок в блоках интегральной оперативной памяти | 1988 |

|

SU1605281A1 |

| Мажоритарное декодирующее устройство | 1987 |

|

SU1471313A1 |

Изобретение относится к вычислительной технике и может быть использовано в качестве буферной памяти для сопряжения потоков информации в устройствах, работающих в реальном времени. Цель изобретения - повышение быстродействия устройства. В устройстве переключение происходит после считывания всей записанной информации в одном из блоков памяти. Для реализации данного метода в устройство введены триггеры, элементы И-НЕ, инверторы и элемент И с соответствующими связями. 1 ил.

| Устройство для управления обменом информацией процессора с памятью | 1986 |

|

SU1325494A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство буферной памяти | 1987 |

|

SU1418723A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-04-23—Публикация

1989-01-09—Подача