начают, что мантиссу входного числа необходимо сдвинуть соответственно на один, два или три разряда влево.

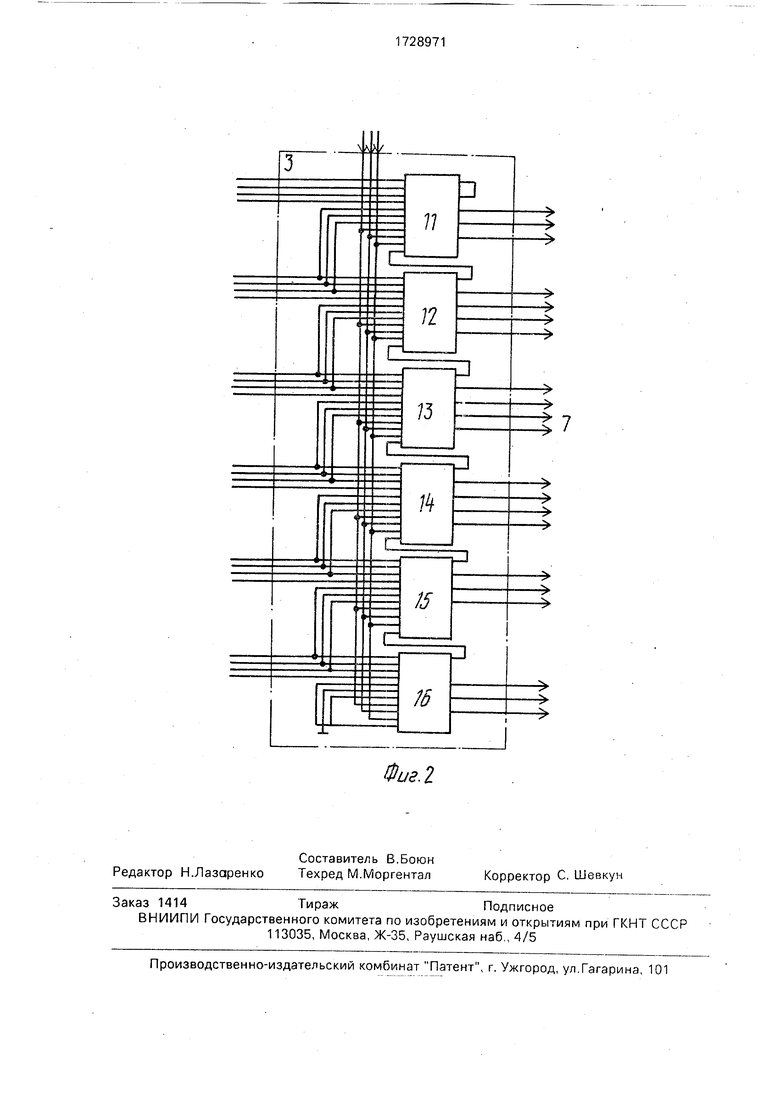

Код, поступающий с выходов сдвига блока 1 соответственно на входы ППЗУ 11 - 16 (фиг.2) блока 3 формирования мантиссы, совместно со значениями сигналов, поступающими соответственно на входы 4, выбирают соответствующие ячейки памяти, содержимое которых передается на выход преобразователя как преобразованная мантисса.

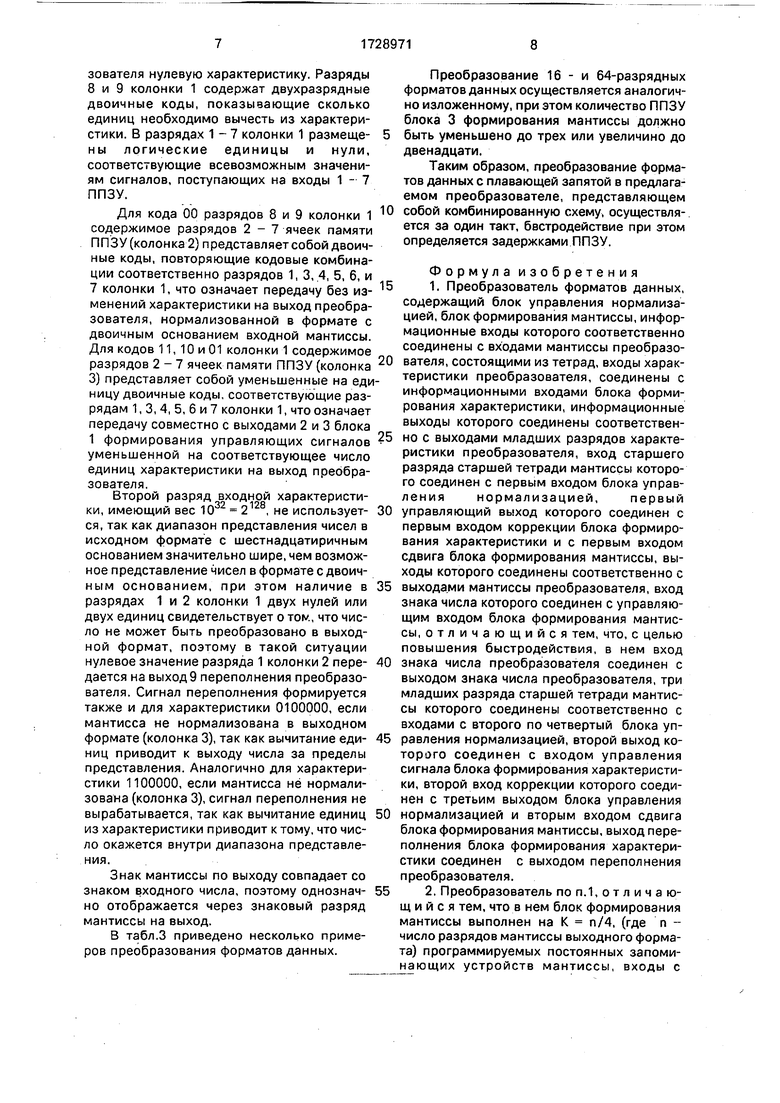

Разряд 11 адреса содержит двоичное значение сигнала переноса, поступающего с первого выхода предыдущего ППЗУ. Разряд 10 адреса содержит двоичное значение сигнала, поступающего с входа знака преобразователя. Разряды 8 и 9 адреса содержат двухразрядные двоичные коды, показывающие на сколько разрядов необходимо сдвинуть мантиссу входного числа влево. В разрядах 1 - 7 адреса размещены логические единицы и нули, соответствующие всевозможным значениям сигналов, поступающих на входы 4 ППЗУ блока 3 формирования мантиссы.

При преобразовании мантиссы положительного входного числа (нулевое значение разряда 10 адреса 1) для кода 00 разрядов

8и адреса содержимое разрядов 2-5 ячеек памяти ППЗУ 11 - 16 и представляет собой двоичные коды, повторяющие кодовые комбинации соответственно разрядов 1-4 адреса, что означает передачу без изменений нормализованной в формате с двоичным основанием входной мантиссы на выход преобразователя. Для кода 11 разрядоз 8 и 9 адреса содержимое разрядов 2-5 ячеек памяти ППЗУ представляет собой двоичные коды, повторяющие кодовые комбинации соответственно разрядов 2-5 адреса, что означает передачу сдвинутой на один разряд влево входной мантиссы на выход преобразователя. Для кода 10 разрядов 8 и

9адреса содержимое разрядов 2-5 ППЗУ представляет собой двоичные коды, повторяющие кодовые комбинации соответственно разрядов 3-6 адреса, что означает передачу сдвинутой на два разряда влево входной мантиссы на выход преобразователя. Для кода 0 1 разрядов 8 и 9 адреса содержимое разрядов 2-5 ячеек памяти ППЗУ представляет собой двоичные коды, повторяющие кодовые комбинации соответственно разрядов 4-7 адреса, что означает передачу сдвинутой на три разряда влево входной мантиссы на выход преобразователя. Для положительной входной мантиссы значение первого разряда

содержимого ячеек памяти ППЗУ, являющегося сигналом переноса, равно нулю.

Отрицательная мантисса во входном формате должна быть представлена в вы- ходном формате в дополнительном коде со знаковым разрядом, равным единице, поэтому по единичному значению знака входного числа на в ыход мантиссы преобразователя передается содержимое 0 ППЗУ 11 - 16. Получение дополнительного кода осуществляется по правилу: все нули и первая встретившаяся единица при просмотре мантиссы входного числа справа налево передается без изменений, остальная 5 же часть мантиссы инвертируется.

Нулевое значение первого разряда содержимого ячейки, поступающее на вход 11 последующего ППЗУ, означает, что предыдущим ППЗУ обнаружены одни нули и что 0 последующее ППЗУ должно выдать дополнительный код соответствующей входной тетрады. Единичное значение первого разряда содержимого ячейки означает, что предыдущим ППЗУ обнаружена первая еди- 5 ница и им выдан дополнительный код сдвинутой на соответствующее количество разрядов входной тетрады и что последующее ППЗУ должно выдать инверсный код соответствующей тетрады. 0 Единичное значение первого разряда содержимого ячейки означает, что предыдущим ППЗУ выдан дополнительный или инверсный код соответствующей тетрады и что последующее ППЗУ должно выдать ин- 5 вереныи код соответствующей тетрады.

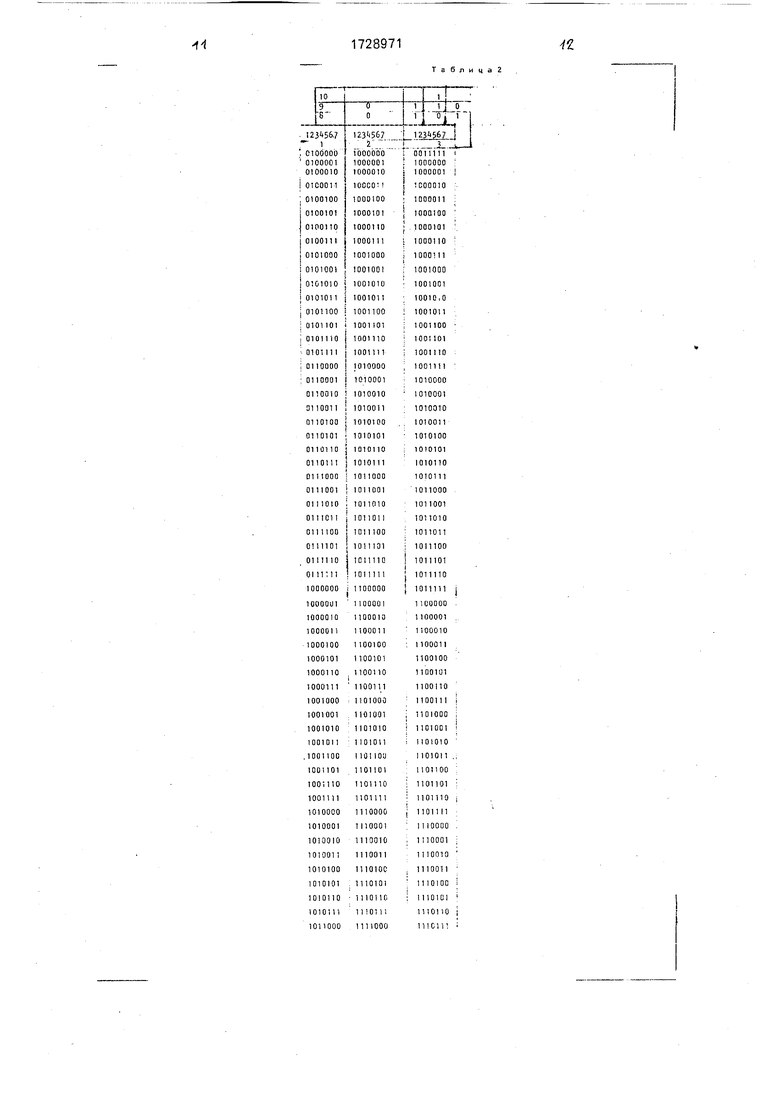

Вычитание единиц из характеристики входного числа, обусловленное сдвигами мантиссы, осуществляется блоком 2 формирования характеристики, который представ- 0 ляет собой программируемое постоянное запоминающее устройство, запрограммированное в соответствии с табл.2. Условно табл.2 разбита на три колонки, Логические единицы и нули в разрядах 1-10 колонки 1 5 представляют собой по отношению к ППЗУ адрес соответствующей ячейки памяти. Логические единицы и нули в каждой из колонок 2 и 3 представляют собой запрограммированное содержимое ячеек 0 памяти. Для упрощения табл.2 разряды 8 - 10 колонки 1 занимают горизонтальное положение. Единичное значение разряда 10 колонки 1 указывает на ненулевое значение входной мантиссы и разрешает передачу 5 преобразованной характеристики на выход преобразователя. Нулевое же значение разряда 10 колонки 1 указывает на ненулевое значение мантиссы входного числа, выбирает область памяти ППЗУ, содержащую нули, и выдает, таким образом, на выход преобразователя нулевую характеристику. Разряды 8 и 9 колонки 1 содержат двухразрядные двоичные коды, показывающие сколько единиц необходимо вычесть из характеристики. В разрядах 1-7 колонки 1 размеще- ны логические единицы и нули, соответствующие всевозможным значениям сигналов, поступающих на входы 1-7 ППЗУ.

Для кода 00 разрядов 8 и 9 колонки 1 содержимое разрядов 2-7 ячеек памяти ППЗУ (колонка 2) представляет собой двоичные коды, повторяющие кодовые комбинации соответственно разрядов 1, 3, 4, 5, 6, и 7 колонки 1, что означает передачу без из- менений характеристики на выход преобразователя, нормализованной в формате с двоичным основанием входной мантиссы. Для кодов 11, 10 и 01 колонки 1 содержимое разрядов 2-7 ячеек памяти ППЗУ (колонка 3) представляет собой уменьшенные на единицу двоичные коды, соответствующие разрядам 1, 3, 4, 5, 6 и 7 колонки 1, что означает передачу совместно с выходами 2 и 3 блока 1 формирования управляющих сигналов уменьшенной на соответствующее число единиц характеристики на выход преобразователя.

Второй разряд входной характеристики, имеющий вес 1032 2128, не использует- ся, так как диапазон представления чисел в исходном формате с шестнадцатиричным основанием значительно шире, чем возможное представление чисел в формате с двоич- ным основанием, при этом наличие в разрядах 1 и 2 колонки 1 двух нулей или двух единиц свидетельствует о том, что число не может быть преобразовано в выходной формат, поэтому в такой ситуации нулевое значение разряда 1 колонки 2 пере- дается на выходЭ переполнения преобразователя. Сигнал переполнения формируется также и для характеристики 0100000, если мантисса не нормализована в выходном формате (колонка 3), так как вычитание еди- ниц приводит к выходу числа за пределы представления. Аналогично для характеристики 1100000, если мантисса не нормализована (колонка 3), сигнал переполнения не вырабатывается, так как вычитание единиц из характеристики приводит к тому, что число окажется внутри диапазона представления.

Знак мантиссы по выходу совпадает со знаком входного числа, поэтому однознач- но отображается через знаковый разряд мантиссы на выход.

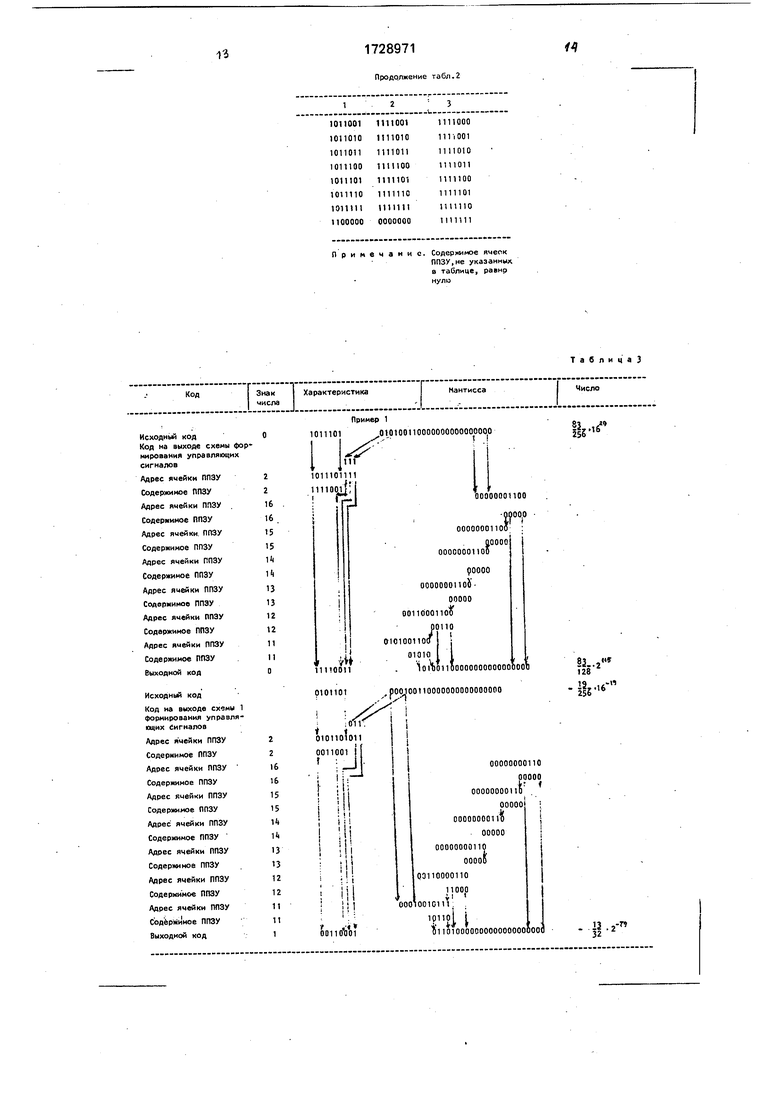

В табл.3 приведено несколько примеров преобразования форматов данных.

Преобразование 16 - и 64-разрядных форматов данных осуществляется аналогично изложенному, при этом количество ППЗУ блока 3 формирования мантиссы должно быть уменьшено до трех или увеличино до двенадцати.

Таким образом, преобразование форматов данных с плавающей запятой в предлагаемом преобразователе, представляющем собой комбинированную схему, осуществляется за один такт, бвстродействие при этом определяется задержками ППЗУ.

Формула изобретения

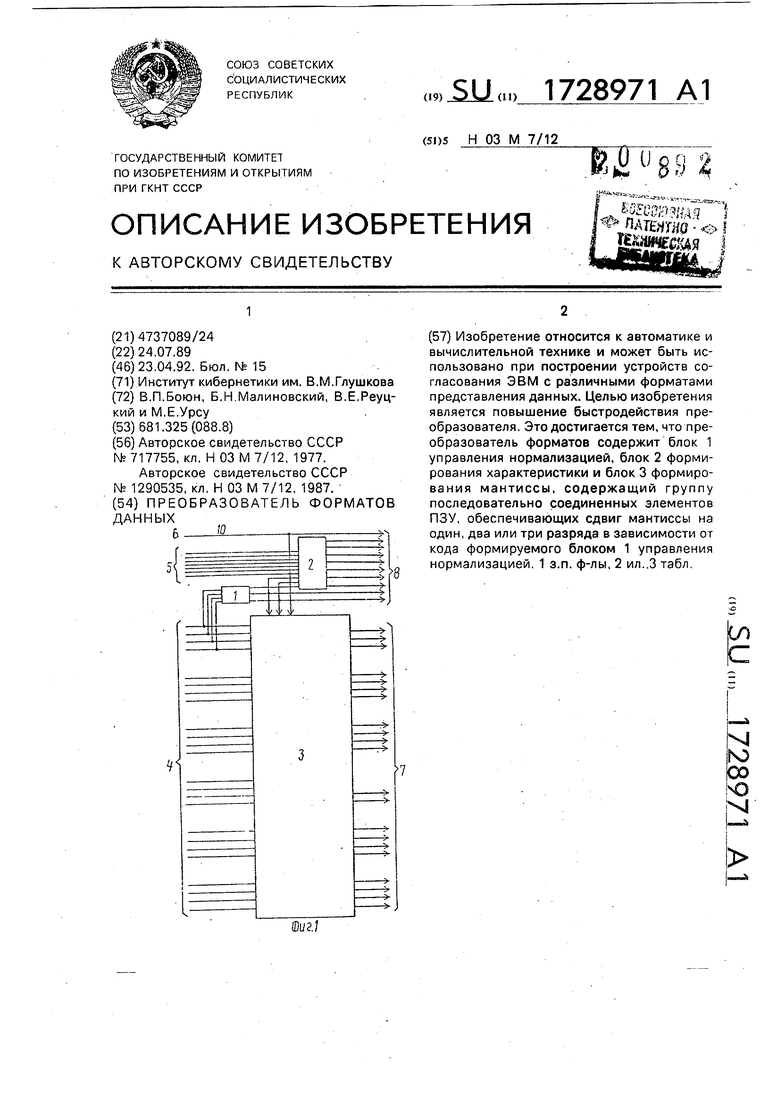

1.Преобразователь форматов данных, содержащий блок управления нормализацией, блок формирования мантиссы, информационные входы которого соответственно соединены с входами мантиссы преобразователя, состоящими из тетрад, входы характеристики преобразователя, соединены с информационными входами блока формирования характеристики, информационные выходы которого соединены соответственно с выходами младших разрядов характеристики преобразователя, вход старшего разряда старшей тетради мантиссы которого соединен с первым входом блока управления нормализацией, первый управляющий выход которого соединен с первым входом коррекции блока формирования характеристики и с первым входом сдвига блока формирования мантиссы, выходы которого соединены соответственно с выходами мантиссы преобразователя, вход знака числа которого соединен с управляющим входом блока формирования мантиссы, отличающийся тем, что, с целью повышения быстродействия, в нем вход знака числа преобразователя соединен с выходом знака числа преобразователя, три младших разряда старшей тетради мантиссы которого соединены соответственно с входами с второго по четвертый блока управления нормализацией, второй выход которого соединен с входом управления сигнала блока формирования характеристики, второй вход коррекции которого соединен с третьим выходом блока управления нормализацией и вторым входом сдвига блока формирования мантиссы, выход переполнения блока формирования характеристики соединен с выходом переполнения преобразователя.

2.Преобразователь по п.1, от л и ч а ю- щ и и с я тем, что в нем блок формирования мантиссы выполнен на К п/4, (где п - число разрядов мантиссы выходного формата) программируемых постоянных запоминающих устройств мантиссы, входы с

первого по четвертый разрядов каждого из которых соответственно соединены с информационными входами соответствующих тетрад блока формирования мантиссы, входы с пятого по седьмой разрядов всех программируемых постоянных запоминающих устройств, кроме последнего, соединены соответственно с входами с первого по третий разрядов соседней младшей тетради, входы с восьмого по десятый разрядов всех программируемых постоянных запоминающих устройств объединены и соответствен0

но соединены с первым и вторым входами сдвига и управляющим входом блока формирования мантиссы, входы одиннадцатых разрядов 1-го (1 1- п-1) программируемого постоянного запоминающего устройства соединены с первым выходом (I + 1)-го программируемого постоянного запоминающего устройства, входы с пятого по седьмой разрядов и вход одиннадцатого разряда п- го программируемого постоянного запоминающего устройства соединены с входом логического нуля преобразователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь форматов данных | 1989 |

|

SU1686701A1 |

| Преобразователь форматов данных | 1985 |

|

SU1290535A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Преобразователь форматов данных | 1986 |

|

SU1476615A1 |

| Преобразователь двоично-десятичногоКОдА B дВОичНый КОд | 1979 |

|

SU809151A1 |

| Преобразователь форматов данных | 1985 |

|

SU1418909A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОЙ ДРОБИ В ДВОИЧНУЮ ДРОБЬ | 1979 |

|

SU826335A1 |

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1978 |

|

SU752323A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1979 |

|

SU860053A1 |

15

Таблица 1

Таблица 2

Продолжение табл.2

ППЗУ,не указанных а таблице, равно нулю

Авторы

Даты

1992-04-23—Публикация

1989-07-24—Подача