ff

ф Л7

-Изобретение относится к цифровой вьмислите,Щ)Ной технмхе и может быть использовано при построении устройст согласования ЭВМ с ра.зличными фор- матами представления дйнных

Цел1) изобретения - расширение класса решаемых задач за счет обеспечения преобразования данных со знако порядка, а также упрощение преобра- зователЯНа х ертеже приведена блок-схема предлагаемого преобразователя фор-матов данных.

Преобразователь содержит блок 1 ,, счетчик 2 порядка, коммутатор 3 мантиссы, блок 4 управления, триггер 5 знака мантиссы, элементы ИЛИ 6, ИСКЛЮЧАЮЩЕЕ ИШ 7, выход 8 разрешения приема, выход 9 занято-- стн, 10 разрешенная выдачи, II окончания приема, тактовий вход 1 2.

Принцип построения к работу предлагаемого преобразователя рассмотрим на npiBv-jepe преобразования формата данных СМ ЭВМ в формат ЕС ЭВМ.

Дво1Вд Ные числа с плав,ч:1ош,ей запятой в йормате Ш ЭВМ (мо;зели СМ-2, CM-i2 0), представл рпо гся следующем образом: разряд - знак мантиссы, 23 разряда - маЕ1тксса, 7 разрядов -- порядокJ I разряд - знак порядка.

Основание системы счиспания в юр мате СМ ЭВМ принято ранным 2, поэтому норглализация чисс;; ссуществляется с точностью до 1 разряр.а.

Положительная мантисса и положи- TejibH-Dii-i порядок представлятется в прямом коде со знаковьш:и разрядами, равными О. Отрицательная мантисса и отрицательный порядок представляются в дополннтеш ном коде со знаковыми разрядами, равньми 1. Пред- пслагается,, что запятая в мантиссе фиксируется непосредственно слева от ее старшей :цифры,

Диапазон представления нормализованных чисел (по абсолютному зна- ченио) находится в пределах от 2 до 2

Д:зотнь е числа с плавающей запятой 3 иорнате ЕС ЭВМ пз едставляютея следуюглям образом 1 разряд - энг.к числа, 7 разрядов - смещенный порядок,

9/5

разряда - маитксса.

Основание системы счисления в зтом формате прш1ято равньм 2 Ib,

-

5

5

-0

5

поэтому нормализация чисел осуществляется с точностью до тетрады. Порядок чисел представляется увеличением на 2 645 т.е. смещенным на числовой оси 3 положительном направлении на 6 разряд.ов, в результате чего все порядки являются положн- тельнымй . Положительные и отрицательные числа с плавающей запятой (их смещенные порядки к мантиссы) во всех моделях ЭВМ единой системы в оператизной п;змяти хранятся в прямом коде .

Знак числа определяется по зна- ченгФ) двотданой цифры в первом старшем разряде смещенного порядка.

Диапазон представления нормализо- ванньгк шестнад:цатиричных чисел (по абсолютному значению) определяется пределами от 6 до 6 , т,е„ значительно шире., чем диапазон представления чисел в формате СМ ЭВМ.

Преобразователь работает следующим образом.

При подклюггенки входного кода и подаче сигнала Разрешение приема по входу осуществляется запись нулевого разряда (знак числа) в нулевой (знаковый) разряд блока 3 сдвига, 1 -- 23 разрядов - в 24-разрядньй блок сдвига (причем в 24-й разряд всегда записьшается О) , тридцать первого разряда (знак порядка) - в знаковьгй разряд c4eT4VD a 2 порядка, 24-30 разрядов порадка - во 2 - 8 рг-зряды счетчика 2 порядка, в 1 разряд счетчика 2 порядка при этом за

5

письшается

О

Нулевой разряд входного кода записьюается также в триггер блока 4 у11:равления. Сигнал 8° Разрешение приема, поступивший также в блок 4 управления, подготавливает его к работе и выдает сигнал Занято на 9, предзшрелщая источник: входной ; шформации о занятости ус гройст ва .,

Знак мантиссы по выходе совпадает со sHaKoiyi входного числа, поэтому он однозначно отображается через знаковый разркд мантиссы на зьгход. Отрицательный порядок числа в РГСХОДНОМ формате представляется в дополнительном коде с единидай в знаковом разряде порядка, а положительный - в прямом коде с кулем в знаковом разряде порядка, поэтому первый разряд сме-. щенного порядка в преобразованном

формате определяется как инверсия 3i разряда порядка входного числа. . При переходе от двоичного основания к шестнадцатиричному для полу- чения целого значения шестнадцатиричного смещенного порядка требуется выполнить сдвиги вправо содержимого блока 1 нормализации мантиссы с добавлением единиц в счетчик 2 порядка до 10 тех пор, пока два младших его разряда, не станут равными О.

Если логическая сумма младших двух разрядов счетчика 2 порядка равна 1, то на первом выходе блока 4 уп- 15 равления появится сигнал разрешения сдвигов (со знаком) содержимого блока 1 сдвигов вправо и на выходе инкремента блока 4 управления - сигнал для добавления единицы в счетчик 2 порядка. Сдвиги в блоке 1 и сложение единиц в счетчике 2 порядка осуществляются под воздействием тактовых импульсов (ТИ) по входу 12 до тех

разрядами, а в выходном - 24 разрядами, поэтому в 24-й разряд блока I сдвиг-а записьшается О и для этог разряда расширен коммутатор 3 манти сы.

В случае отрицательной мантиссы с помощью коммутатора 3 мантиссы осуществляется вьщача на выход преобразователя инверсного значения мантиссы.

При отрицательном порядке един1« ный выход знакового разряда счетчика 2 порядка подается на вход элеме та ИСКЛЮЧАЮЩЕЕ ИЛИ 7. Если дополнительный старший разряд счетчика 2 порядка находится в 1, то во второй разряд выходного формата вьща- ется О, а если дополнительный ста ший разряд счетчика 2 порядка находится в нулевом состоянии, то во- второй разряд выходного формата через элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 7 выдается 1 и в первый разряд выходног

20

пор, пока логическая сумма двух млад-25 смещенного порядка через элемент 6

выдается О.

ших разрядов счетчика 2 порядка не станет равна О. Количество возможных сдвигов равно 0-3. Когда логическая сумма двух младших разрядов счетчика 2 порядка будет равна О, снимается разрешающий сигнал с первого и третьего выходов блока 4 управления и блок управления подготавливается для дальнейшей работы. Ес- ли младшие два разряда счетчика 2 порядка сразу оказались равными О, то сложение единиц в счетчике 2 порядка и сдвиги в блоке 1 не производятся.

Отрицательная мантисса в выходном формате должна быть представлена в прямом коде со знаком числа, равным 1, поэтому после денормализации числа блоком 4 управления осуществляется проверка знака входного числа, записанного по входу знака блока 4 управления. Если мантисса отрицательна, то на второй выход блока управления вьщается сигнал декремента для вычитания единицы из содержимого блока 1. Следующим тактовым импульсом блок управления формирует сигнал Разрешение выдачи и подает на выход 10 преобразователя.

Особенностью преобразования ман- т иссы является также то, что в исходном коде мантисса представлена 23

10,

15 6012

разрядами, а в выходном - 24 разрядами, поэтому в 24-й разряд блока I сдвиг-а записьшается О и для этого разряда расширен коммутатор 3 мантиссы.

В случае отрицательной мантиссы с помощью коммутатора 3 мантиссы осуществляется вьщача на выход преобразователя инверсного значения мантиссы.

При отрицательном порядке един1«- ный выход знакового разряда счетчика 2 порядка подается на вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 7. Если дополнительный старший разряд счетчика 2 порядка находится в 1, то во второй разряд выходного формата вьща- ется О, а если дополнительный старший разряд счетчика 2 порядка находится в нулевом состоянии, то во- второй разряд выходного формата через элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 7 выдается 1 и в первый разряд выходного

20

смещенного порядка через элемент 6

выдается О.

При положительном порядке единица с инверсного знакового разряда счетчика 2 порядка через элемент ИЛИ 6 вьщается на выход 1 разряда выходного формата. Ввиду того, что в выходном формате порядок числа смещен в положительном направлении и все порядки являются положительными, а 1 и О в первом разряде смещенного порядка свидетельствуют соответственно о положительном и отрицательном порядках, то во всех случаях, кроме случая, когда порядок в выходном формате равняется О, знаковый разряд счетчика 2 порядка инвертирует свое значение на противоположное. Элемент ИСКЛОЧАЮЩЕЕ ИЛИ 7 управляет вторым разрядом выходного смещенного порядка в зависимости от состояний знакового разряда и дополнительного старшего разряда счетчика 2 порядка.

После того, как выходной код бу- дет принят приемником информации, из него должен поступить сигнал Окончание приема по входу 1I, который сбрасьтает блок 4 управления в нулевое состояние, снимает сигнал занятости по выходу 9, после чего устройство готово к приему нового числа.

Пример,

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь форматов данных | 1982 |

|

SU1092490A1 |

| Преобразователь форматов данных | 1985 |

|

SU1418909A1 |

| Преобразователь форматов данных | 1985 |

|

SU1290535A1 |

| Специализированный процессор обработки данных | 1982 |

|

SU1062715A1 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

| Преобразователь форматов данных | 1989 |

|

SU1686701A1 |

| Преобразователь форматов данных | 1986 |

|

SU1476615A1 |

| Устройство для обработки данных | 1985 |

|

SU1287146A1 |

| Арифметическое устройство | 1989 |

|

SU1647557A1 |

| Суммирующее устройство | 1991 |

|

SU1807480A1 |

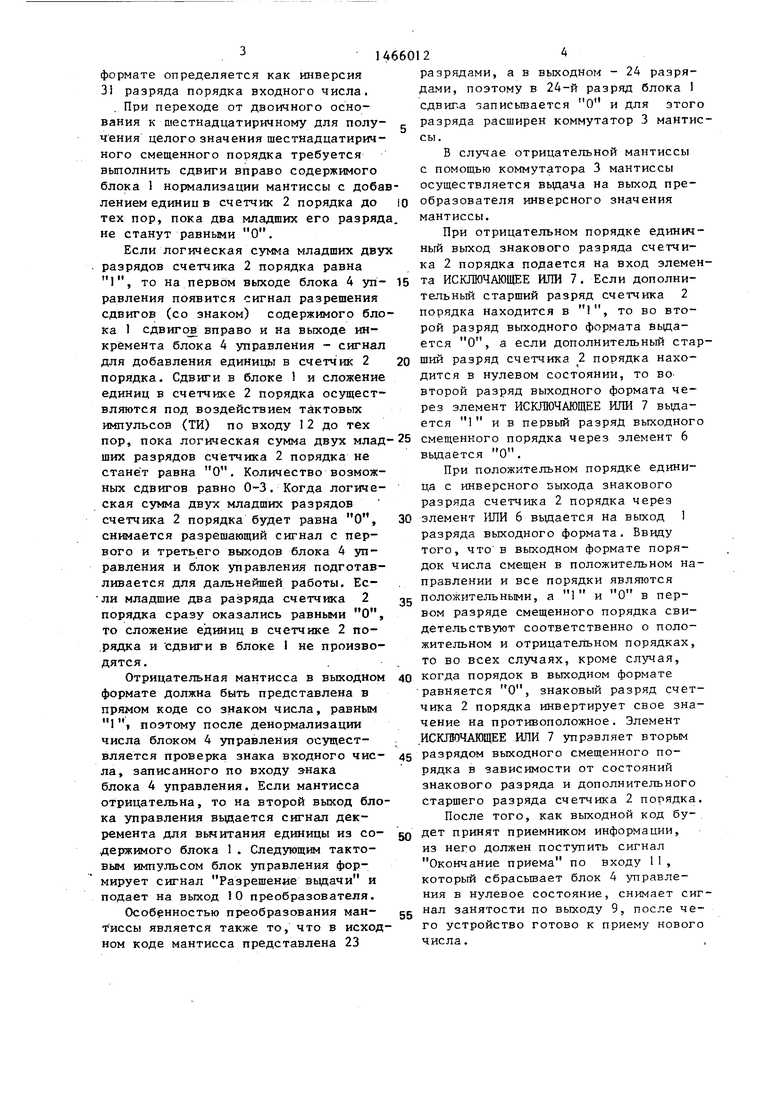

Изобретение откосится к вьянс- лительной технике и может быть использовано при построении устройств согласования 38М с различными форматами представления данных. Целью изобретения является расширение класса решаемых задач за счет обеспечения преобразования данньк со знаком порядка, а также упрощение преобразователя. Поставленная цель достш ается тем, что в преобразователь форматов, содержащий блок 1 сдвига, счетчик 2 порядка, коммутатор 3 мантиссы, блок 4 управления, триггер 5 знака мантиссы, элемент HCItW-lATOlilEE Шт 7, дополнительно введен элемент ИЛИ 6.1 ил.

Знак май- 1И;антисса тиссы

Исходный код

Прием на блок сдвига и счетчик порядка

После денормали- зации

Выходной код

О 101000000000000000000000110110 о 5.2

о 10100000000000000000000 0 00110110

о 00101000000000000000000 о 00111000

|1

о 0010 000000000000000000 1 ООП 1 о

J .16 32

Знак

числа

Мантисса

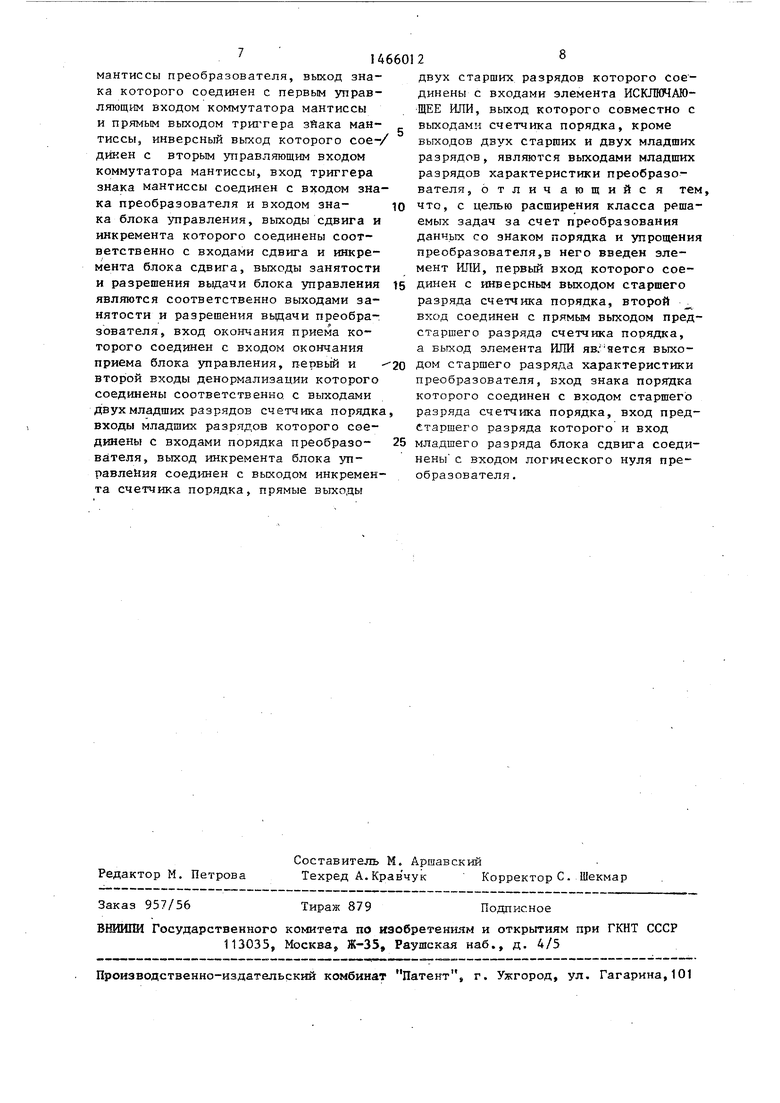

Пример 2.

Знак мантиссыМантисса

Исходный код

прием на блок сдвига и счетчик порядка

После денормали- зации

Ion ООООООООООООООООООСО010010101

10110000000000000000000001 01001010

0110000000000000000000 1 О 0001100

После вьнитания

II Т|

Выходной код Знак числа

1 10101 1 1 111 11 11 11 П 11 111 J 01 000 100

tOi Р) ) К ж

вз( S I 1 0010100000000000000000000 11 ООН

МантиссаХарактеристика

Преобразование 16 и 64-разрядньпс форматов данных осуществляется аналогично изложенному, при этом разрядность блока сдвига должна быть ;теньшена или увеличена на соответствующее количество разрядов.

Формула изобретения

Преобразователь форматов данных, содержащий счетчик порядка, блок сдвига, триггер знака мантиссы, комДоп . Поря- Знак Число раз- док по- рядрядка

J .16 32

и

Характеристгаса

Доп. Поря- Знак Число раз- док по- рядрядка

5 , , - 1э

32

-16

мутатор мантиссы, элемент ИСКЛЮЧАЮ- ЩЕЕ ИЛИ и блок управления, тактовый вход которого соединен с тактовыми входами счетчика порядка и блока сдвига и с тактовым входом преобразователя,, входы мантиссы которого соединены со всеми, кроме младшего, информационными входами блока сдвига, выходы которого соединены с разрядными входами коммутатора мантиссы выходы которого являются выходами

14

мантиссы преобразователя, выход знака которого соединен с первым управляющим входом коммутатора мантиссы и прямым выходом трш гера зйака мантиссы, инверсный выход которого сое-/ дйкен с вторым управляющим входом коммутатора мантиссы, вход триггера знака мантиссы соединен с входом знака преобразователя и входом зна- ка блока управления, выходы сдвига и инкремента которого соединены соответственно с входами сдвига и инкремента блока сдвига, выходы занятости и разрешения вьдачи блока управления являются соответственно выходами занятости и разрешения выдачи преобразователя, вход окончания приема которого соединен с входом окончания приема блока управления, п-ервьй и второй входы денормализации которого соединены соответственно, с выходами двух младших разрядов счетчика порядка входы младших разрядов которого соединены с входами порядка преобразо- вателя, выход инкремента блока уп- равлейия соединен с выходом инкремента счетчика порядка, прямые выходы

28

двух старших разрядов которого соединены с входами элемента ИСКЛКНАЮ- ЩЕЕ ИЛИ, выход которого совместно с выходами счетчика порядка, кроме вьгходов двух старших и двух младших разрядов, являются выходами младших разрядов характеристики преобразователя, отличающийся тем что, с целью расширения класса решаемых задач за счет преобразования данных со знаком порядка и упрощени преобразователя,в него введен элемент ИЛИ, первый вход которого соединен с инверсным выходом старшего разряда счетчика порядка, второй - вход соединен с прямым выходом пред старшего разряда счетчика порядка, а выход элемента ИЛИ яа яется выходом старшего разряда характеристики преобразователя, вход знака порядка которого соединен с входом старшего разряда счетчика порядка, вход пред- старшего разряда которого и вход младшего разряда блока сдвига соединены с входом логического нуля преобразователя.

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-03-15—Публикация

1986-01-14—Подача