Изобретение относится к цифровой вычислительной технике и может быть исполь- зовано при построении устройств согласования ЭВМ с различными форматами представления данных,

Целью изобретения является повышение быстродействия и упрощение преобразователя.

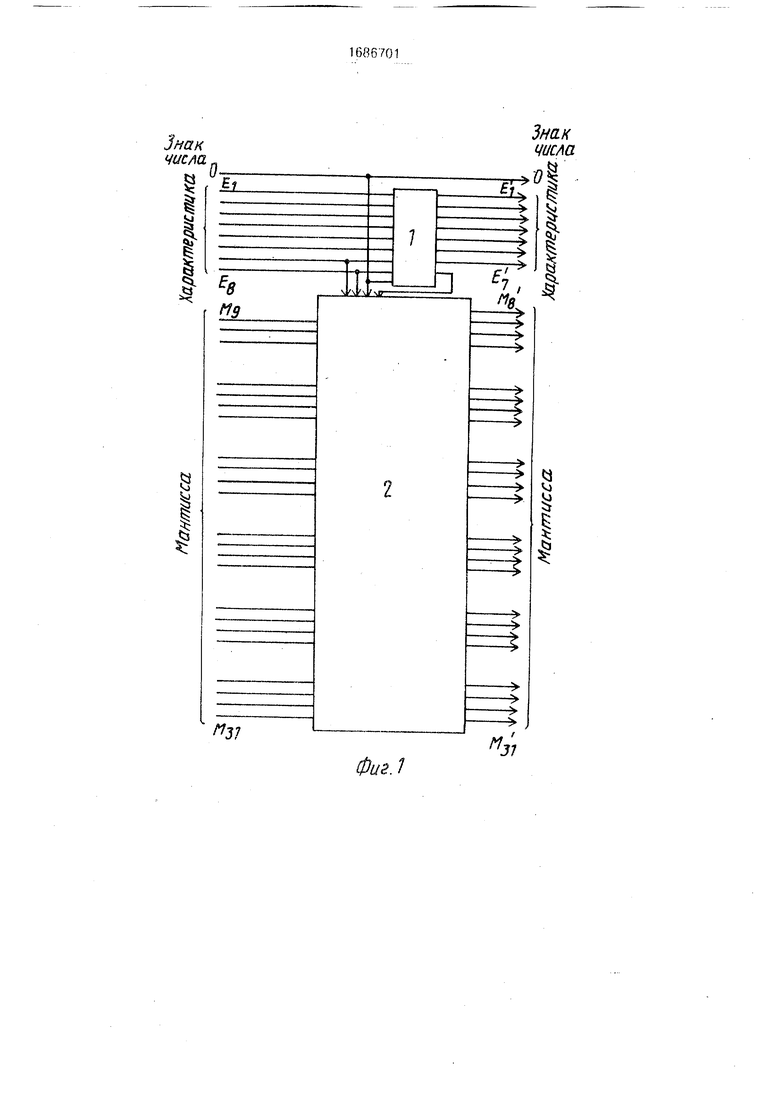

На фиг. 1 приведена блок-схема преобразователя; на фиг.2 - схема блока формирования мантиссы.

Преобразователь (фиг.1) содержит блок 1 формирования характеристики и блок 2 формирования мантиссы, информационные выходы которого являются выходами Ма Мз1 мантиссы преобразователя, выходы EI- Е характеристики которого соединены соответственно с выходами блока 1 формирования характеристики, входы которого соединены соответственно с входами Е i-Ee характеристики и входом знака преобразователя, блок формирования мантиссы, информационные входы которого соединены

соответственно с входами Мд-Мз1 мантиссы преобразователя.

Блок формирования мантиссы (фиг.2) содержит постоянные запоминающие устройства (ПЗУ) 3-8, выходы которых являются выходами блока формирования мантиссы, управляющие входы которого соединены соответственно с входами каждого из ПЗУ 3-8.

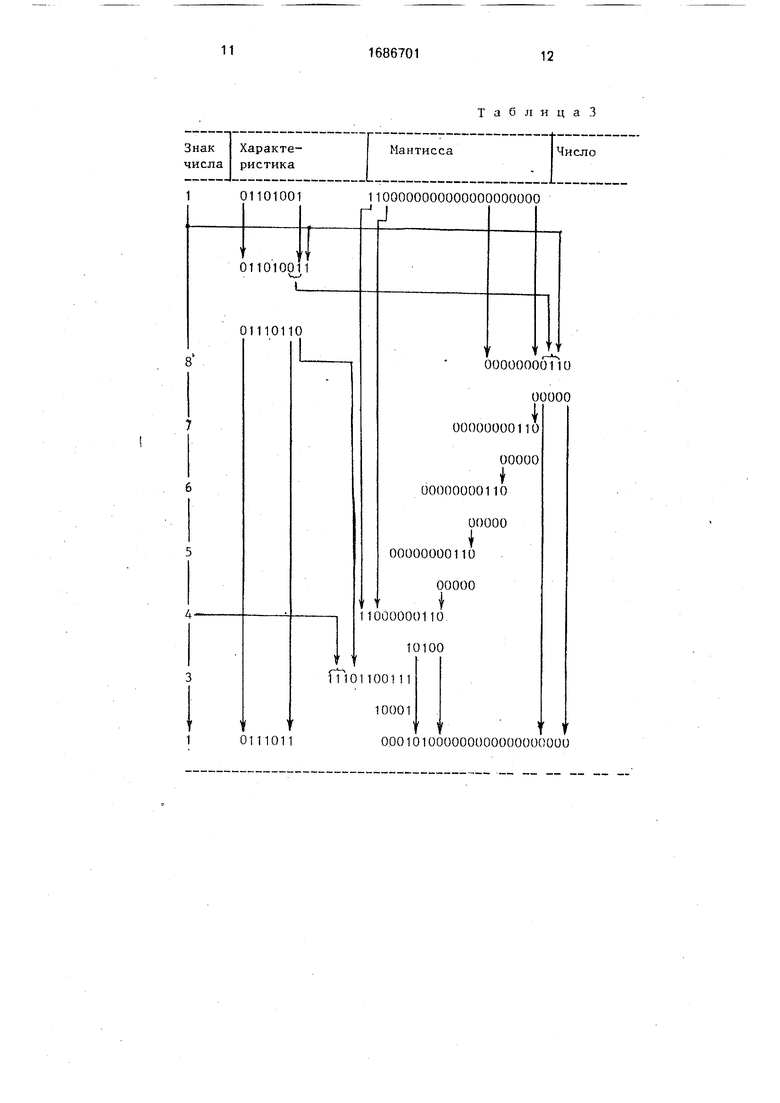

Принцип построения и работы предлагаемого преобразователя рассмотрим на примере преобразования форматов данных ЭВМ СМ-4 в формат ЕС ЭВМ.

Двоичные числа с плавающей запятой в формате ЭВМ СМ-4 представляются следующим образом: 1 разряд - знак числа; 8 разрядов - характеристика; 23 разряда - мантисса.

Основание системы счисления в формате ЭВМ СМ-4 принято равным двум, поэтому нормализация чисел осуществляется с

точностью до одного разряда.

Порядок чисел представляется увеличенным , т.е. смещенным на числоЁ

О 00

о

ч|

о

И з

4-4

ой оси в положительном направлении на 7 азрядов, в результате чего все порядки поожительны и являются характеристиками.

Положительная мантисса представляется в прямом коде со знаком разрядов, равным нулю. Отрицательная мантисса представляется в дополнительном коде со знаковым разрядом, равным единице.

Диапазон представления нормализованных двоичных чисел (по абсолютному значению) определяется пределами от 2 до .

Если характеристика тождественна нулю, а также если мантисса отрицательна, значение этого сигнала является логическим нулем,

Знак мантиссы по выходу совпадает со знаком входного числа, поэтому однозначно отображается через знаковый разряд мантиссы на выход преобразователяе ыраженмя 2х

- а1

(2 4 ) ( 164 )х 16 4 , связывающего числа в двоичной и шестнадцатиричной системах счисления, видно, что характеристика последнего в четыре раза меньше первой. Так как делением характеристики входного числа на двоичное число 100 (1002 4ю) последние ее два разряда теряются, необходимо эти разрядам придать нулевые значения. Для этого к характеристике входного числа необходимо добавлять единицы до тех пор, пока последние (младшие) ее два разряда не станут рае- ными нулю. Добавление необходимого количества единиц к входной характеристике осуществляется блоком 1 формирования характеристики, который представляет собой программируемое постоянное запоминающее устройство, запрограммированное в соответствии с табл. 1. Условно табл.1 разбита на колонки 1,2,3,4 и 5. Логические единицы и нули в колонке 1 представляют собой по отношению к ПЗУ адрес соответствующей ячейки памяти, Логические единицы и нули в каждой из колонок 2-5 представляют собой запрограммированное содержимое ячеек памяти ПЗУ. Для упрощения таблицы разряды 7-9 колонки 1 занимают горизонтальное положение.

Нулевое или единичное значение разряда 9 колонки 1 определяют по восьмому выходу соответствующее значение неявного старшего (восьмого) разряда мантиссы.

Для кода 00 разрядов 7-8 колонки 1 содержимое разрядов 1 и 3-7 ячеек памяти (колонка 2) представляет собой двоичные коды, повторяющие кодовые комбинации соответственно разрядоа 1-6 колонки 1,что

означает передачу без изменения характеристики положительного входного числа на выход преобразователя. Значения разряда 8 колонки 2 при этом равны единице, за исключением ячейки с адресом 000000000 разрядов 1 и 3-7 ячеек памяти (колонка 3) представляет собой увеличенные на едини- . цу двоичные коды соответствующие разрядам 1-6 колонки 1, что означает передачу 0 увеличенной соответственно на одну, две или три единицы характеристики положительного входного числа на выход преобразователя. Разряд 8 колонки 3 при этом имеет единичное значение. 5 Колонки 4 и 5 табл.1 иллюстрируют формирование характеристики и неявного старшего разряда мантиссы для отрицательного входного числа (разряд 9 колонки 1 равен единице). Содержимое колонок 4 и 5 повто- 0 ряют соответственно содержимое колонок 2 и 3 за исключением разряда 8, значение- которого равно нулю для всех адресов.

Диапазон изменения входного числа соответствует изменению характеристики 5 входного числа в пределах 0100000- 0111111 для отрицательных, и в пределах 1000000-10111111 : для положительных порядков, пределы 0000000-0011111 для отрицательных и пределы 110001-1111111 0 для положительных порядков при этом не используются. Поэтому второй разряд характеристики выходного числа всегда является инверсией первого разряда харак-. эристики выходного числа, кроме 5 случая, когда характеристика входного числа имеет одно из значений 1111101,1111110 и 1111111. В этом случае на выходе преобразователя характеристика имеет значение 1100000. В соответствии с изложенным, 0 разряд 2 колонок 2,3,4 и 5 табл. 1 является инверсией разряда 1 колонки 1 таблицы.

Сдвиг входной мантиссы вправо на 0,1,2 или 3 разряда.обусловленный добавлением к входной характеристике соответственно 5 0,1,2 и 3 единицы, осуществляется блоком 2 формирования мантиссы, постоянные запоминающие устройства которого реализуют табличные преобразования.

Логические значения входов представ- 0 ляют собой по отношению к каждому из блоков ПЗУ 3-8 адрес соответствующей ячейки памяти. Значения выходов представляют собой запрограммированное содержимое ячеек памяти. Первый (младший) 5 входной разряд содержит двоичные значения сигнала, поступающего с входа знака преобразования. Разряды управления сдвигом 1 содержат двухразрядные двоичные коды 0(Г,11Г,10 и ОГ, показывающие, что мантиссу входного числа необходимо

сдвинуть соответственно на 0,1,2 или 3 разряда вправо. Остальные разряды соответствуют всевозможным значениям сигналов, поступающих на входы ПЗУ 3-8 блока 2 формирования мантиссы.

При преобразовании мантиссы положительного входного числа для кода 00 разрядов управления сдвигом содержимое разрядов 2-5 ячеек памяти ПЗУ 3-8 представляет собой двоичные коды, повторяющие кодовые комбинации соответствующих входных разрядов, что означает передачу без изменений входной мантиссы на выход преобразователя. Для кода 11 разрядов управления сдвигом содержимое разрядов 2-5 ячеек памяти ПЗУ 3-8 представляет собой двоичные коды, повторяющие кодовые комбинации соответствующих разрядов, что означает передачу сдвинутой на один разряд вправо входной мантиссы на выход преобразователя. Для положительной входной мантиссы значение первого разряда содержимого ячеек памяти ПЗУ 3-8, являющегося сигналом переноса, равно нулю.

Отрицательная мантисса в дополнительном коде во входном формате должна быть представлена в выходном формате в прямом коде со знаковым разрядом, равным единице. Преобразование дополнительного кода в прямой код осуществляется по правилу: все нули и первая встретившаяся единица при просмотре мантиссы входного числа справа налево передаются без изменения, остальная же часть мантиссы инвертируется.

В соответствии с изложенным при преобразовании мантиссы отрицательного входного числа нулевое значение выхода, поступающее на вход переноса последующего ПЗУ, означает, что предыдущим ПЗУ обнаружены одни нули последующее ПЗУ должно выдать также прямой код сдвинутой соответствующей входной тетрады на соответствующее число разрядов. Единичное значение этого разряда означает, что предыдущим ПЗУ обнаружена первая единица и им выдан прямой код сдвинутой на соответствующее число разрядов входной тетрады,

Преобразование форматов данных приведено в табл. 2-5.

Преобразование 16 и 64 разрядных форматов данных осуществляется аналогично изложенному, при этом количество ПЗУ блока 2 формирования мантиссы должно быть уменьшено до трех или увеличено до двенадцати.

Таким образом, преобразование форматов данных с плавающей запятой в преобразователе, представляющем собой комбинационную схему, осуществляется зе

один такт, быстродействие при этом опре деляется задержками ПЗУ.

Формула изобретения 5Преобразователь форматов данных, содержащий блок формирования мантиссы и блок формирования характеристики, входы которого соединены с входами характеристики преобразователя, вход знака которо0 го является выходом знака преобразователя и соединен с входом знака блока формирования мантиссы тетрады, информационные входы которого соединены с входами мантиссы преооразователя, вы5 ходы мантиссы которого-соединены с выходами мантиссы блока формирования мантиссы, первый и второй входы управления сдвигом которого соединены соответственно с входами двух младших разрядов

0 характеристики преобразователя, выходы характеристики которого соединены с выходами блока формирования характеристики, выход нулевой характеристики которого соединен с управляющим входом блока фор5 мирования мантиссы, отличающийся тем, что, с целью повышения быстродействия и упрощения преобразователя, в нем вход знака преобразователя соединен с входом младшего разряда блока формиро0 вания характеристики, а блок формирования мантиссы выполнен на группе блоков ПЗУ, выходы младших разрядов которых являются выходами блока формирования мантиссы,, выход старшего разряда 1-го блока

ПЗУ (i Ь-, где п - разрядность мантиссы

преобразователя) соединен с адресным входом первого разряда (1+1)-го блока ПЗУ, ад- ресные входы второго, третьего и

0 четвертого разрядов всех блоков ПЗУ соединены соответственно со знаковым входом и первым и вторым входами управления сдвигом блока формирования мантиссы, адресные входы с пятого по девятый разрядов

5 всех блоков ПЗУ, кроме n-го, соединены с входами соответствующих тетрад входов блока формирования мантиссы, адресные входы с десятого по одиннадцатый разрядов всех блоков ПЗУ, кроме n-го, соединены

0 соответственно с входами трех младших разрядов соседней старшей тетрады входов блока формирования мантиссы, адресные входы с пятого по восьмой разрядов последнего блока ПЗУ соединены соответственно

5 с тремя старшими входами блока формирования мантиссы, адресный вход девятого разряда n-го блока ПЗУ соединен с управляющим входом блока формирования мантиссы, адресные входы с десятого по одиннадцатый разрядов n-го блока ПЗУ соединены с входом знака блока формирования мантиссы, адресный вход первого разряда первого блока ПЗУ соединен с аходом логического нуля.

Таблица 1 Таблица истинности схемы формирования характеристики

Продолжение табл.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь форматов данных | 1989 |

|

SU1728971A1 |

| Преобразователь форматов данных | 1985 |

|

SU1290535A1 |

| Преобразователь двоично-десятичногоКОдА B дВОичНый КОд | 1979 |

|

SU809151A1 |

| Преобразователь форматов данных | 1986 |

|

SU1476615A1 |

| Преобразователь двоичных чисел в двоично-десятичные | 1987 |

|

SU1481897A1 |

| Преобразователь форматов данных | 1985 |

|

SU1418909A1 |

| Устройство для накопления чисел с плавающей запятой | 1990 |

|

SU1829030A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Преобразователь форматов данных | 1982 |

|

SU1092490A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОЙ ДРОБИ В ДВОИЧНУЮ ДРОБЬ | 1979 |

|

SU826335A1 |

Изобретение относится к цифровой вычислительной технике и может быть исполь- зовано при построении устройств согласования ЭВМ с различными форматами представления данных. ЦепсЮ изобретения является пбвышение быстродействия и упрощение преобразователя. Поставленная цель достигается тем, что в преобразователе форматов, содержащем блок формирования характеристики и блок формирования мантиссы, последний выполнен в виде группы ПЗУ. 2 ил. 5 табл.

1001100

Таблица

0011010000000000000000000

1б 2

64

01101001

0111011

Т а б л и ц а 3

1100000000000000000000

000101000000000000000000

10101110

Ь4гЧ

10100

101011100 4J

10011001

10100001000

100100 {

00011011000

1001100

Адрес ячейки ПЗУ 7 Содержимое ПЗУ 7 Адрес ячейки ПЗУ 6 Содержимое ячейки Адрес ячейки ПЗУ 5 Содержимое ПЗУ 5 Адрес ячейки ПЗУ 4 Содержимое ПЗУ 4 Адее ячейки ПЗУ 3 Содержимое ПЗУ 3 Выходной код

101000000000000000000000

00000001000 00000

J

0000000100

00000

I

00000001000 00000

{

00000001000

00000

{

10100001000

00011

I .

0011010000000000000000000

ТаблкцаЗ

-a- f

64

Знак числа

8

I

Оi

Знак числа

| Устройство для преобразования двоичного кода в десятичный и обратно для чисел с плавающей запятой | 1977 |

|

SU717755A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь форматов данных | 1986 |

|

SU1476615A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-10-23—Публикация

1989-07-24—Подача