Изобретение относится к вычисли- тельной технике и может быть использовано в управляющих вычислительных машинах обработки информации.

Цель изобретения - повышение достоверности работы матричного сумма- тора.

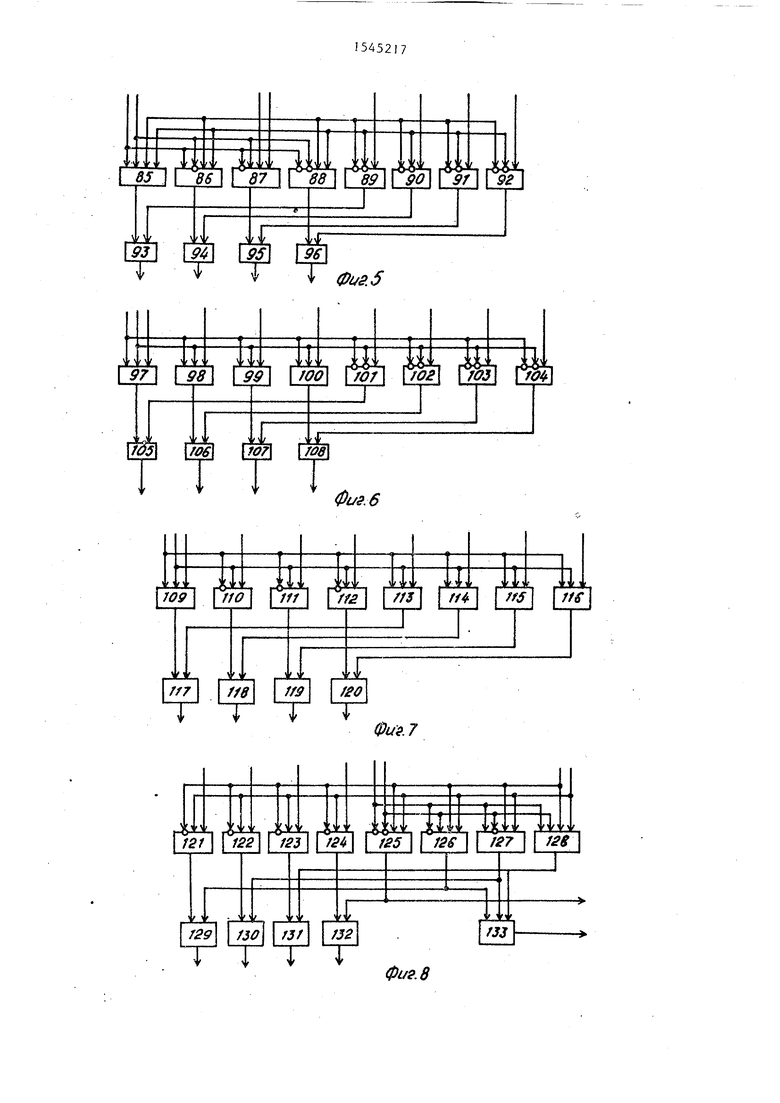

На фиг. 1 приведена функциональная схема матричного сумматора) на фиг.2- 4 - функциональные схемы шифратора кода режима, первого (второго) узла дешифрации и шифратора кода состояния соответственно; на фиг.5-8 - функциональные схемы первого, четвертого, второго и пятого коммутаторов с третьим узлом дешифрации соответст- венно; на фиг. 9 и 10 - функциональные схемы группы элементов ИЛИ и группы элементов И соответственно; на фиг.11- функциональная схема блока элементов И; на фиг. 12 - функ- циональная схема узла суммирования; на фиг. J3-15 - функциональные схемы третьего, шестого и седьмого коммутаторов соответственно на фиг.16 и 17 - функциональные схемы узла ело- жения по модулю два и восьмого коммутатора соответственно.

Матричный сумматор содержит входы 1 и 2 первого и второго слагаемых соответственно матричного сумматора, тактовый вход 3 матричного сумматора, шифраторы 4 и 5 кода состояния и кода режима соответственно, регистр 6 состояния, регистр 7 режима, первый и второй узлы 8 и 9 дешифрации, пер- вый, четвертый, второй и пятый коммутаторы 10-13 соответственно, первую группу элементов ИЛИ 14, первую группу элементов И 15, вторую группу элементов ИЛИ 16, вторую группу элементов И 17, первый и второй блоки элементов И 18 и 19, первый и второй узлы 20 и 21 суммирования, седьмой и третий коммутаторы 22 и 23, третью

5

0

5 0 , Q

5 Q

5

группу элементов ИЛИ 24, третью группу элементов И 25, третий узел 26 суммирования, шестой коммутатор 27, третий блок элементов И 28, узел 29 сложения по модулю два, восьмой коммутатор 30, выходы 3t и 32 результата и переноса матричного сумматора, трел тий узел 33 дешифрации.

Шифратор 5 кода режима (фиг1.2) содержит элементы И 34-48, элементы ИЛИ 49-53 и элемент И 54. Узлы 8 и 9 дешифрации (фиг.З) содержат элементы И 55 и 56, элемент ИЛИ 57, элементы И 58-62 и группу элементов ИЛИ 63. Шифратор 4 кода состояния (фиг.4) содержит в своем составе элементы И 64-79 и элементы ИЛИ 80-84. Коммутатор 10 (фиг.5) содержит в своем составе элементы И 85-92 и элементы ИЛИ 93-96. Коммутатор 11 (фиг.6) содержит в своем составе элементы И 97- 104 и элементы ИЛИ 105-108. Коммутатор 12 (фиг.7) содержит в своем составе элементы И 109-116 и элементы ИЛИ 117-120. Коммутатор 13 и третий узел 33 дешифрации (фиг.З) содержат в своем составе элементы И 121-128 и элементы ИЛИ 129-133. Группа элементов ИЛИ 14 (16,24)(фиг.9) содержит в своем составе элементы ИЛИ 134-137.

Группа элементов И 15 (17, 25) (фиг.10) содержит элементы И 138- 141. Блок элементов И 18 (19, 28) (фиг.11) содержит элементы И 142- 147. Узел 20 (21,26) суммирования (фиг.12) содержит элементы И 148- 157 и элементы ИЛИ 158-163. Коммутатор 23 (фиг.13) содержит элементы И 164-171 и элементы ИЛИ 172-175. Коммутатор 27 (фиг.14) содержит элементы И J76-183 и элементы ИЛИ 184- 187. Коммутатор 22 (фиг.15) содержит элементы И 188-203 и элементы ИЛИ 204-207. Узел 29 сложения по модулю

515

два (фиг.16) содержит элементы И 208-215 и элементы ИЛИ 216 и 217.

Коммутатор 30 (фиг.17) содержит элементы И 218-225 и элементы ИЛИ 226 и 227.

Матричный сумматор работает следующим образом.

Матричный сумматор функционирует в четырех режимах, каждый из которых определяется кодом режима Р, формируемым на втором и третьем выходах узла 9. При этом режимы работы матричного сумматора отличаются от другого составом задействуемых аппаратных средств. Изменение режима работы матричного сумматора производится по заднему фронту сигнала признака операции, поступающего на тактовый вход 3 матричного сумматора, каждый раз, когда на выходе 31 результата или на выходе 32 переноса сумматора формируется соответствующий код с позиционным представлением цифры суммы Z или переноса Р, имеющего ошибку кате гории S-a-О. При этом изменение кода режима Р. производится следующим образом.

Предположим, что после подачи на матричный сумматор питания в пятиразрядном регистре 7 режима, построенно на Т-триггерах, установится избыточный код режима F 01010. Тогда при поступлении в матричный сумматор сигнала признака операции с тактового входа 3 на первом выходе- узла 9 установится сигнал г 1, а на втором и третьем выходах данного узла 9 - код R 00. Если при снятии с входа 3 сумматора сигнала признака операции хотя бы в одном из кодов, формируемых на выходах 31 и 32, присутствует ошибка категории S-a-О, то под воздействием кода Р. 11010, поступающего с шифратора 5 кода режима, в регистре 7 режима установится новый избыточный код состояния Р 10000. В этом случае при поступлении в матричный сумматор на вход 3 очередного сигнала признака операции на первом выходе узла 9 установится сигнал г 0, а на втором и третьем выходах данного узла 9 - код Р. 01 , что соответствует изменению режима работы матричного сумматора.

Если при снятии с входа 3 сумматора очередного сигнала признака операции, по-прежнему хотя бы в одном из кодов, формируемых на выходах 31

0

5

0

21

5

5

0

5

0

5

0

5

7

и 32, присутствует ыиибка категории S-a-О, то под воздействием кода Р 01111, поступающего с шифратора 5 кода режима, в регистре 7 режима установится новый избыточный код состояния R Mill. В этом случае при поступлении в матричный сумматор на вход 3 следующего сигнала признака операции на первом выходе узла 9 установится сигнал г 1, а на втором и третьем выходах данного узла 9 - код R 1 I. .

Если и в дальнейшем на выходах 31г 32 сумматора формируются коды с ошибками категорий S-a-О, то последовательность изменения кода режима R следующая: 00, 01, II, 10, 00, 01,

Данная последовательность изменения кода режима Р сохраняется до тех пор, дока сам шифратор 5 кода режима, регистр 7 режима и узел 9 не будут иметь отказов. В противном случае последовательность изменения кода режима R меняется.

Предположим, что в матричном сумматоре имеются отказы отдельных элементов со следующими проявлениями: в первом разряде регистра 7 режима постоянно присутствует нулъ в четвертом разряде регистра 7 режима постоянно присутствует единица.

Предположим, что после подачи на матричный сумматор питания в регистре 7 режима также установится избыточный код режима R 010IO. Тогда при поступлении в матричный сумматор сигнала признака операции с входа 3 на первом выходе узла 9 установится сигнал г 1, а на втором и третьем выходах данного узла 9 - код R 00. Если при снятии с входа 3 сумматора сигнала признака операции хотя бы в одном из кодов, формируемых на выходах 31 и 32, присутствует ошибка категории S-a-О, то под воздействием кодаR 11010, поступающего с шифратора 5 кода режима,в регистре 7 режима установится новый избыточный код состояния R 11000. В этом случае при поступлении в матричный сумматор на вход 3 очередного сигнала признака операции, на первом выходе узла 9 установится сигнал г О, а на втором и третьем выходах данного узла 9 - код R 01.

Если при снятии с входа 3 сумматора очередного сигнала признака операции по-прежнему хотя бы в одном .

из кодов, формируемых на выходах 31 и 32-, присутствует ошибка категории S-a-О, то под воздействием кода F 00111, поступаюшего с шифратора 5 кода режима, в регистре 7 режима устновится новый избыточный код состояния R 11110. В этом случае при поступлении в матричный сумматор на вход 3 следующего сигнала признака операции на первом выходе узла 9 установится сигнал г 1, а на втором и третьем выходах данного узла 9 - код R 10..

Если в дальнейшем на выходах 31, 32 сумматора формируются коды с ошибками категорий S-a-О, то последовательность изменения кода режима В следующая: 00, 01, 10, II, 00, 01, ... . Следовательно, при данном рас- пределении отказов код режима R принимает все четыре возможных значения хотя последовательность их формирования и отлична от исходной. Это обепечивает работу матричного сумматора во всех четырех режимах.

Аналогичным образом код режима R принимает все свои возможные значения при сохранении возможности изменения в избыточном коде режима Б од ного разряда нз числа первого и пятого и двух разрядов из числа второго, третьего, четвертого.

В первом режиме (R 00) матричный сумматор работает следующим обра зом.

При поступлении на входы 1 и 2 слагаемых матричного сумматора кодов операндов X и Y совместно с сигналом признака операции на входе 3 коды операндов X и Y через коммутаторы 10 и 11 поступают на входы группы элементов ИЛИ 14 и группы элементов И 15. При этом на выходе результата узла 20 суммирования формируется код цифры

Z (X + Y )mod4,

а на выходе переноса узла 20 суммирования - код цифры

Р

О, при (X + Y Х4; 1 , при (X + Y )4

Коды этих чисел соответственно через коммутаторы 22 и 30 поступают на выходы 31 и 32. матричного сумматора и входы шифратора 5 кода режима и шифратора 4 кода состояния. Если коды

0

с Q 5

о

д $

0

5

цифр , и Р не содержат ошибок категории S-a-О, то выполнение операции на этом завершается. В противном случае операция сложения повторяется,но уже при другом режиме работы матричного сумматора.

Во втором режиме (Р 01 ) матричный сумматор работает следукмяим образом .

При поступлении на входы 1 и 2 мат ричного сумматора кодов операндов X и Y совместно с сигналом признака one рации на входе 3 коды операндов X и Y через коммутаторы 12 и 13 поступают на входы группы элементов ИЛ 16 и группы элементов И 17. При этом на выходе результата узла 21 суммирования формируется код суммы Z , а на выходе перенстса - код переноса Р. Коды суммы Z и переноса Р соот-э ветственно через коммутаторы 22 и 30 поступают на выходы 31 и 32 матричного сумматора и входы шифратора 5 кода режима и шифратора 4 кода состояния. Если коды цифр Z и Р не содержат ошибок категории S-a-О, то выполнение операции на этом завершается. В противном случае операция сложения повторяется, но уже при другом режиме работы матричного сумматора .

В третьем режиме (Р, 10) матричный сумматор работает следующим образом .

При поступлении на входы 1 и 2 матричного сумматора кодов операндов X и Y совместно с сигналом признака операции на входе 3 коды операндов X и Y через коммутаторы 23 и 27 поступают на входы группы элементов ИЛИ 24 и группы 25 элементов И. При этом на выходе результ та узла 26 суммирования формируется код суммы Z, а на выходе переноса - код переноса Р. Коды суммы Z и переноса Р соответственно через коммутаторы 22 и 30 поступают на выходы 31 и 32 матричного сумматора и входы шифратора 5 кода режима и шифратора 4 кода состояния. Если коды цифр Z и Р не содержат ошибок категории S-a-О, то выполнение операции на этом завершается. В противном случае операция сложения повторяется, но уже при другом режиме работы матричного сумматора.

91545217

В четвертом режиме (Р 11} матричный суммлтор работает следующим образом.

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричный сумматор | 1987 |

|

SU1582187A1 |

| Матричный сумматор | 1986 |

|

SU1424010A1 |

| Микропроцессор | 1983 |

|

SU1141419A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

| Вычислительное устройство | 1984 |

|

SU1203513A1 |

| Устройство для интерпретации выражений языков программирования | 1982 |

|

SU1078432A1 |

| Устройство для управления параллельным выполнением команд в электронной вычислительной машине | 1982 |

|

SU1078429A1 |

| Система обработки данных | 1980 |

|

SU1003063A1 |

| Устройство для обработки выражений языков программирования | 1981 |

|

SU1016790A1 |

Изобретение относится к вычислительной технике и может быть использовано в управляющих вычислительных машинах обработки информации. Цель изобретения - повышение достоверности работы матричного сумматора. Матричный сумматор содержит шифраторы 4, 5 кода состояния и кода режима, регистр 6 состояния, регистр 7 режима, узлы 8, 9, 33 дешифрации, коммутаторы 10 - 13, 22, 23, 27, 30, группы 14, 16, 24 элементов ИЛИ, группы 15, 17, 25 элементов И, блоки 18, 19, 28 элементов И, узлы 20, 21, 26 суммирования, узел 29 сложения по модулю два. Операнды поступают на входы 1, 2 первого и второго слагаемых матричного сумматора, результат вычисления снимается с выходов 31, 32 результата и переноса матричного сумматора. Тактирование работы ведется по входу 3 матричного сумматора. Осуществляется безошибочное формирование кода суммы при неисправности аппаратуры путем последовательного подключения различных узлов для проведения вычислений. 17 ил.

При поступлении на входы I и 2 матричного сумматора кодов операндов X и Y совместно с сигналом признака операции на входе 3 код операнда X через коммутатор 1 1 поступает на первые входы группы элементов ИЛИ 14 и группы элементов И 15, а код операнда Y через коммутатор 12 поступает на первые входы группы элементов ИЛИ 16 и группы элементов И 17. При этом двухразрядный код состояния S с выходов узла 8 через коммутатор 10 поступает на вторые входы группы элементов ИЛИ 14 и группы элементов И 15, а через коммутатор 13 - па вто рые входы группы элементов ИЛИ 16 и группы элементов И 17. В результате этого на выходе результата узла 20 формируется код цифры

г t (Y + Sj)raod4 ;

где S - цифра, описываемая двоичным кодом S;

на выходе переноса формируется код цифры

. ° I1

О, при X + S 4; при X + S 4,

на вторых выходах узла 33 дешифрации 35 формируется код цифры

Г

к

при 5 0; при S 0 ,

на выходе узла 21 формируется код цифры

Z з (X - S ) mod4 , на выходе переноса формируется код цифры

о,

- Ь.

О, при Y + (4 - S ) mod4 : 4; при Y + (4 - S 3 mod4 , 4.

Код цифры Z через коммутатор . 23, а код цифры 7. через коммутатор 3.1 поступают на входы группы элементов ИЛИ 24 и группы элементов И 25. При этом на выходе узла 26 суммирования формируется код цифры

Z5 Z (Z , + Z 2)mod4 (X+Y )mod4,

а на выходе переноса формируется код цифры

o

5

0

5

0

5

g

5

Коды цифр Р, , Р7, Р3, Р, поступают на входы узла 29 сложения по модулю два, на выходе которого при этом формируется код переноса

Р (Pf + Рг + Р3 + Р;, )mod2.

Коды суммы Z и переноса Р соответственно через коммутаторы 22 и 30 поступают на выходы 31 и 32 матрич- ног-о сумматора и входы шифратора 5 кода режима и шифратора 4 кода состояния. Если коды цифр Z и Р не содержат ошибок категории S-a-О, то выполнение операции на этом завершается. В противном случае по заднему фронту сигнала признака операции происходит изменение кода состояния S и кода режима R. При этом следует отметить, что изменение кода состояния S производится аналогично изменению кода состояния R. Отличие состоит лишь в том, что S формируется на выходах шифратора 4 кода состояния только при R 1J и наличии ошибки категории S-a-О хотя бы в одном из кодов, поступаюших на выходы 31 и 32 матричного сумматора.

Одновременное изменение кода состояния S и кода режима R позволяет матричному сумматору при возвращении, после отработки первого, второго, третьего режимов, в четвертый режим производить обработку информации при другом коде состояния S, а следовательно, и при задействовании других элементов сумматора, исключая тем самым из работы отказавшие элементы.

Таким образом, все ошибки в обрабатываемых сумматором кодах можно свести к ошибкам одной категории S-a-О. Это значительно упрощает контроль выходной информации сумматора и позволяет использовать в нем отказоустойчивые средства контроля и управления.,

Предлагаемый матричный сумматор обладает устойчивостью к двум-четырем отказам элементов контроля и управления .

Сообщение матричному сумматору устойчивости к отказам элементов управ- ления и контроля повышает его безотказность, как системы, при равных показателях надежности его компонентов. Это повышает показатели надежности процессора IIВМ, построенного на основе предлагаемого решения.

Формула изобретения

Матричный сумматор, содержащий восемь коммутаторов, три группы элементов И, три группы элементов ИЛИ и три блока элементов И, причем вход

первого слагаемого матричного сумма тора соединен с первыми информационными входами первого, -второго и третьего коммутаторов, вход второго слагаемого матричного сумматора подклю- чей к первым информационным входам четвертого, питого и шестого коммутаторов, выходы элементов ИЛИ первой, второй и третьей групп соединены с входами первого, второго и третьего блоков элементов И соответственно, о т л и ч а ю т, и и с я тем, что, с целью повышения достоверности работы матричного сумматора, в него введены три узла суммирования, узел ело жения по модулю два, регистр состояния, регистр режима, шифратор кода состояния, шифратор кода режима и три узла дешифрации, причем вход первого слагаемого матричного сумматора подключен к второму информационному входу четвертого коммутатора, вход второго слагаемого матричного сумматора подключен к второму информационному входу второго коммутатора выходы первого коммутатора и выходы четвертого коммутатора соединены соответственно с первыми и вторыми входами соответствующих элементов И первой группы и элементов ИЛИ первой группы, выходы второго коммутатора и выходы пятого коммутатора соединены соответственно с первыми и вторыми входами соответствующих элементов И второй группы и элементов ИЛИ второй группы, выходы трет)его и выходы шестого коммутаторов соединены соответственно с первыми и вторыми входами соответствующих элементов И третьей группы и элементов ИЛИ треть ей группы, выходы 1-го блока элементов И и выходы элементов И i-й группы соединены соответственно с первой и второй группами информационных входов i-ro узла суммирования (1 i 3 выходы результата первого, второго и третьего узлов суммирования соединены соответственно с первым, вторым и третьим информационными входами

0

Q 5 0 Q

5

седьмого коммутатора, выход которого является выходом результата матричного сумматора, выходы переноса первого, второго ц третьего утлов суммирования соединены соответственно с первым, вторым и третьим информационными входами узла сложения по модулю дна и восьмого коммутатора, выход которого является выходом переноса матричного сумматора, выходы шифраторов кода состояния и кода режима соединены с соответствующими информационными входами регистра Состояния и регистра режима соответственно, информационные выходы регистров состояния и режима соединены с информационными входами первого и второго узлов дешифрации соответственно, выходы седьмого и во сьмого коммутаторов, информационные выходы второго, третьего и четвертого разрядов регистра состояния и первый первого узла дешифрации соединены с соответствующими информационными входами шифратора кода состояния, выходы седьмого и восьмого коммутаторов, информационные выходы второго, третьего и четвертого разрядов регистра режима и первый выход второго узла дешифрации соединены с соответствующими информационными входами шифратора кода режима, тактовый вход матричного сумматора подключен к тактовым входам регистров состояния и режима и первого и второго узлов дешифрации, . второй и третий выходы второго узла дешифрации соединены с управляющими входами всех коммутаторов и соответствующими информационными входами шифратора кода состояния, второй и третий выходы первого узла дешифрации соединены с соответствующими разрядами вторых информационных входов первого и пятого коммутаторов, выходы результата первого и второго узлов суммирования соединены с вторыми информационными входами третьего и шестого коммутаторов соответственно, вторые и третьи выходы первого и второго узлов дешифрации соединены с информационными входами третьего узла дешифрации, информационный выход которого соединен с четвертым информационным входом узла сложения по модулю два, выход результата которого соединен с четвертым информационным входом восьмого коммутатора .

ЈЫф

/ i/i

4ЈJ LЈЈj ШО

.Л lii

Ю I. /У. .1 QЈ

f

i i i

-vv xjnry :

SQDU

W 89

f

V4L ,

Ш M

r05 tO€ 107 Ш

т

I

V I

9f 92

Фиг. 5

Фиг. 6

Фи 9.7

фиг. 8

Ј

0W/

Фиг. /У

Ч F F V Ч М ч f1 F

I

166 fff7

LJ

U

/Л

f

Й/г /J

iI

Т

Щ

I--w--I r--w i /wi OS LZ5J

t/p. 15

Составитель В. Гречнев Редактор С. Патрушева Техред М.Ходаннч Корректор М.Самборская

Фиг. 16

Фиг. f7

| Матричный сумматор-умножитель | 1978 |

|

SU767759A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР №,1348824, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-02-23—Публикация

1987-11-17—Подача