1

(21)4382391/24-24

(22)22.12.87

(46) 30.07.90. Бюл. N1 28 (72) И.А.Баранов и А.А.Шикин

(53)681.3(088.8).

(56)Авторское свидетельство СССР № 1104508, кл. G Об F 7/52, 1982.

Авторское свидетельство СССР F 1424010, кл. G Об F 7/50, 1986.

(54)МАТРИЧНЫЙ СУММАТОР

(57)Изобретение относится к вычислительной технике и может быть использовано в управляющих системах повышенной надежности. Цель изобретения - повышение достоверности работы

матричного сумматора. Матричный сумматор содержит два коммутатора, четыре элемента ИЛИ, семь элементов И, три узла сложения, шесть регистров, два пороговых элемента, две группы элементов И, узел дешифрации, группу элементов ИЛИ, узел свертки по модулю два, элемент НЕ и блок управления. Операнды, пройдя через коммутаторы, поступают на входы первого узла сложения. Первый пороговый элемент контролируют правильность представления кодов переноса и результата первого узла сложения. При обнаружении ошибки с помощью сигналов на выходах блока управления возможно исправление аппаратурных ошибок. 2 з.п. ф-лы, 4 ил.

I

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричный сумматор | 1987 |

|

SU1545217A1 |

| Матричный сумматор | 1986 |

|

SU1424010A1 |

| Микропроцессор | 1983 |

|

SU1141419A1 |

| Матричный сумматор | 1986 |

|

SU1348824A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР | 2009 |

|

RU2417409C2 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| Арифметическое устройство | 1979 |

|

SU849206A2 |

| Арифметическое устройство | 1989 |

|

SU1647557A1 |

| Микропроцессор | 1977 |

|

SU717772A1 |

| Устройство для решения дифференциальных уравнений | 1983 |

|

SU1233149A1 |

Изобретение относится к вычислительной технике и может быть использовано в управляющих системах повышенной надежности. Цель изобретения - повышение достоверности работы матричного сумматора. Матричный сумматор содержит два коммутатора, четыре элемента ИЛИ, семь элементов И, три узла сложения, шесть регистров, два пороговых элемента, две группы элементов И, узел дешифрации, группу элементов ИЛИ, узел свертки по модулю два, элемент НЕ и блок управления. Операнды, пройдя через коммутаторы, поступают на входы первого узла сложения. Первый пороговый элемент контролирует правильность представления кодов переноса и результата первого узла сложения. При обнаружении ошибки с помощью сигналов на выходах блока управления возможно исправление аппаратурных ошибок. 1 з.п. ф-лы, 4 ил.

Изобретение относится к вычислительной технике и может быть использовано в управляющих системах повышенной надежности.

Цель изобретения - повышение достоверности работы матричного сумматора.

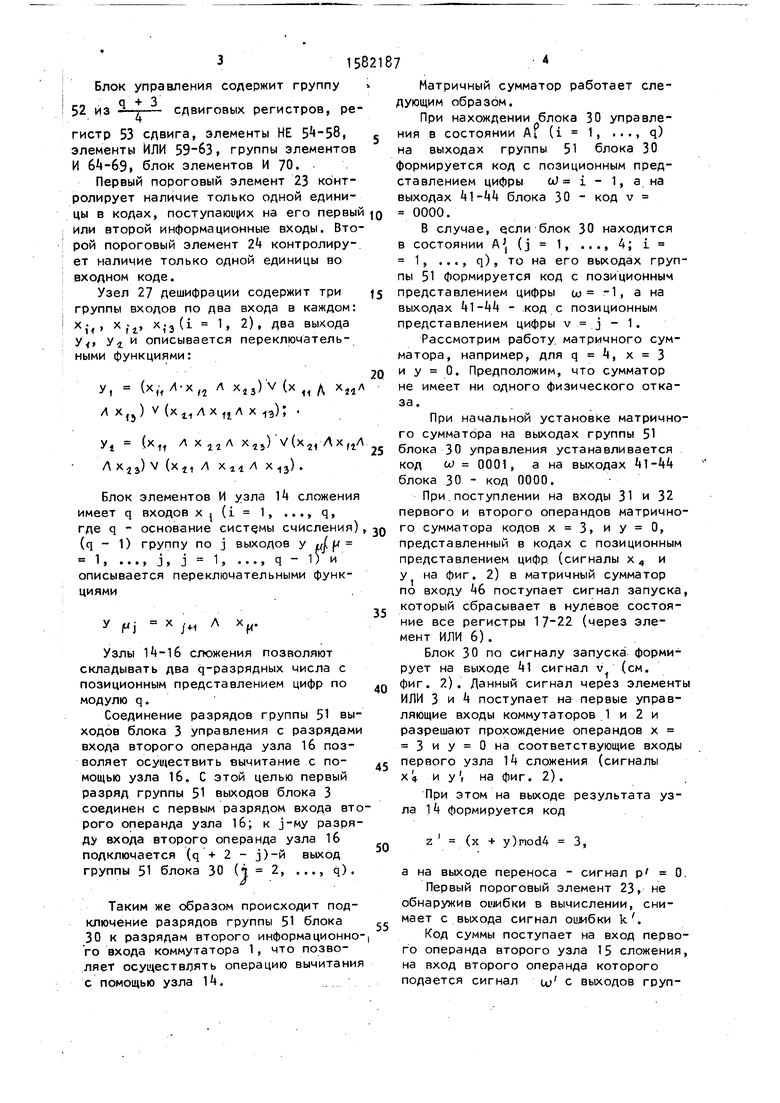

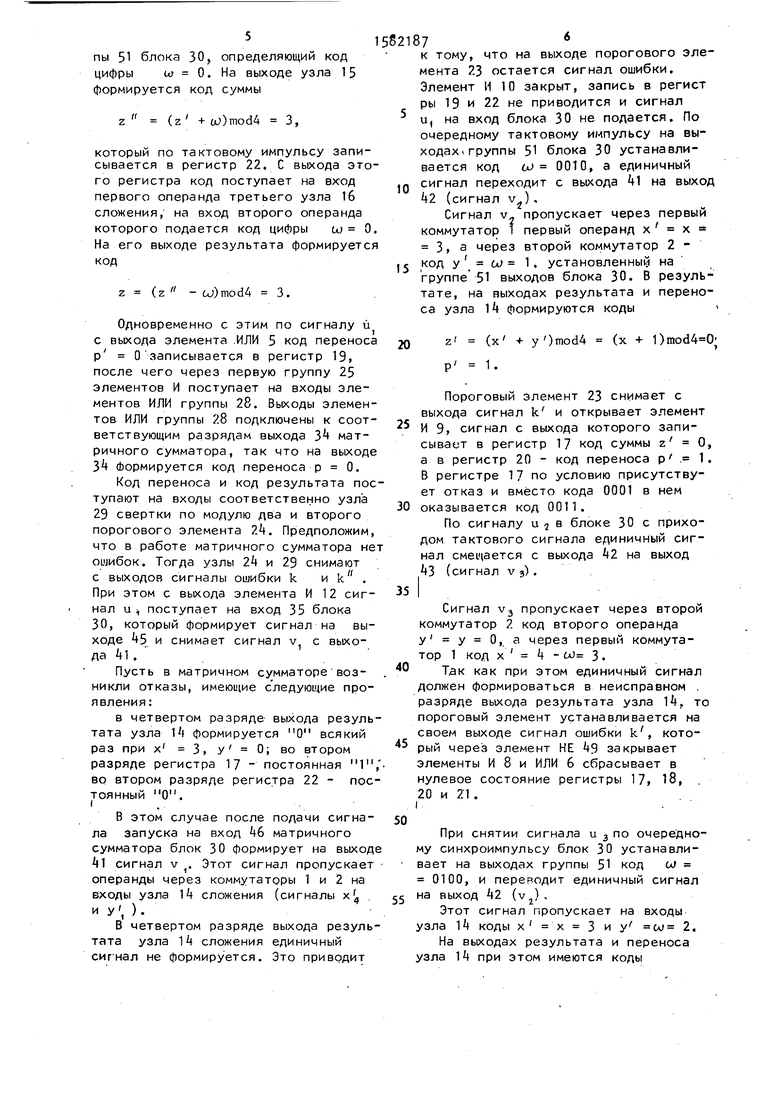

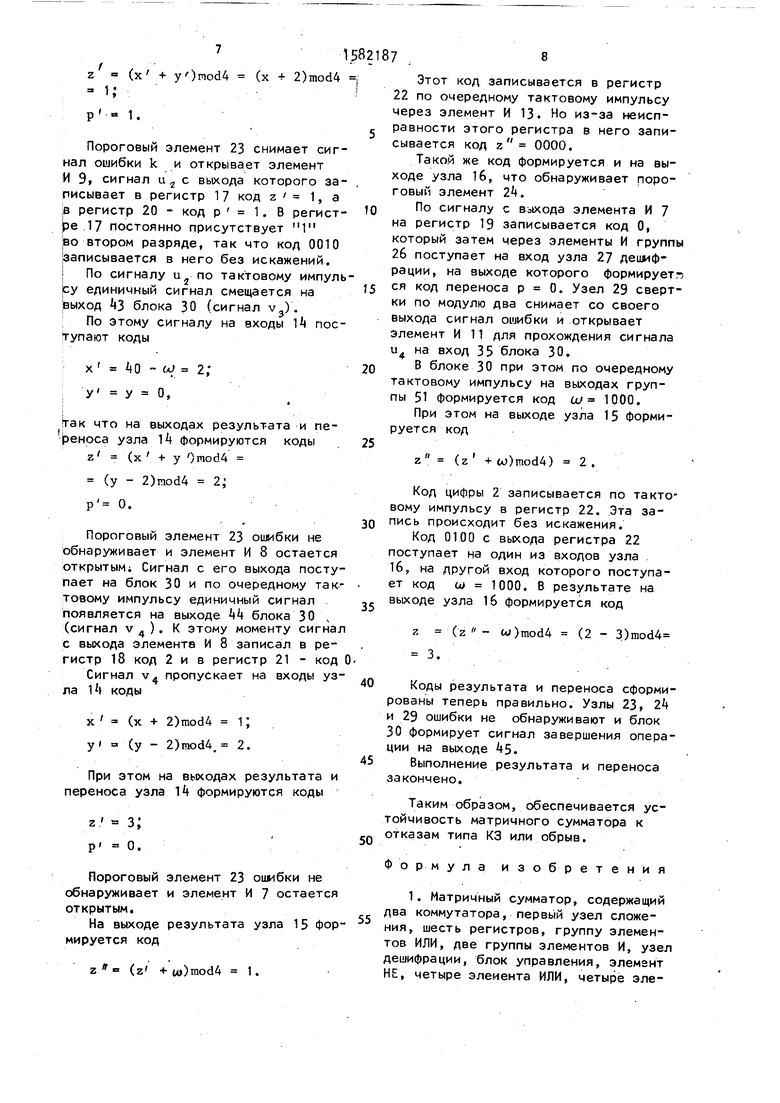

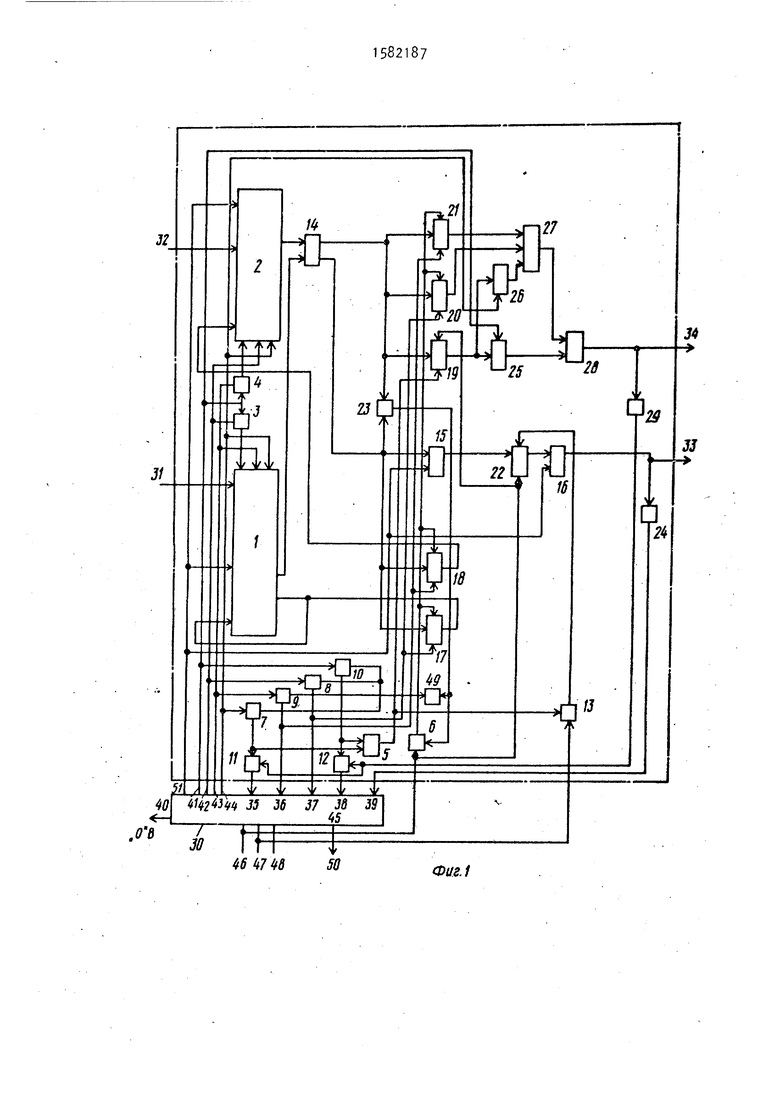

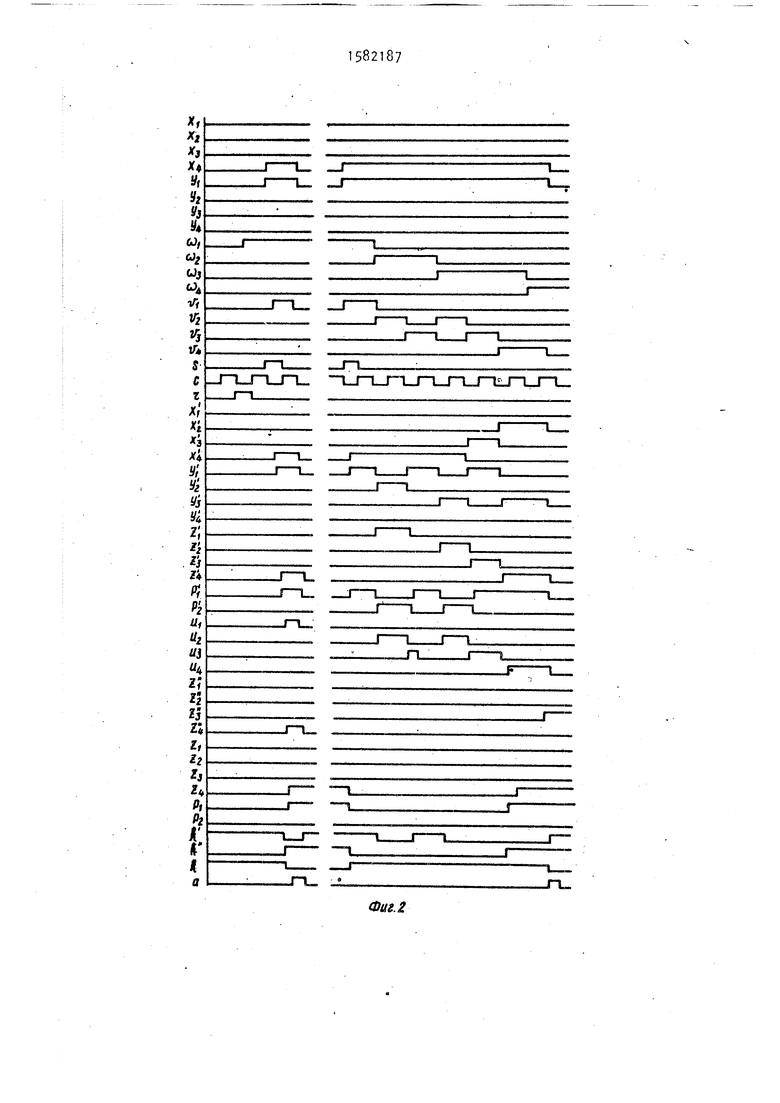

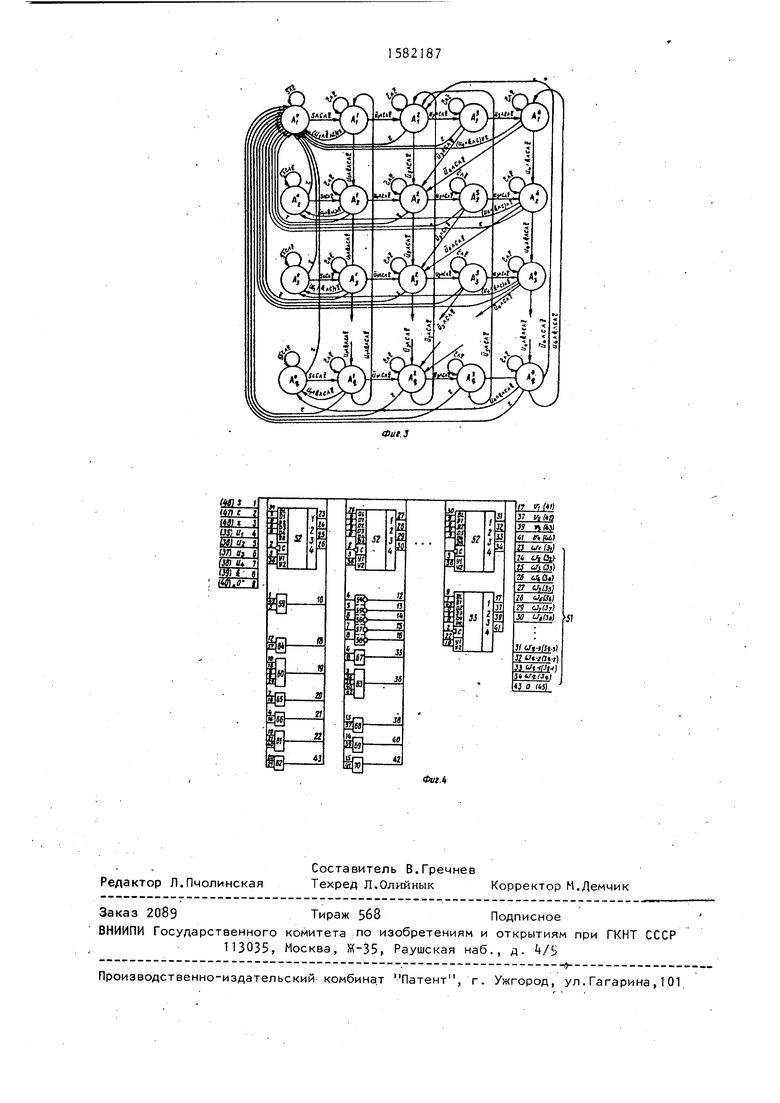

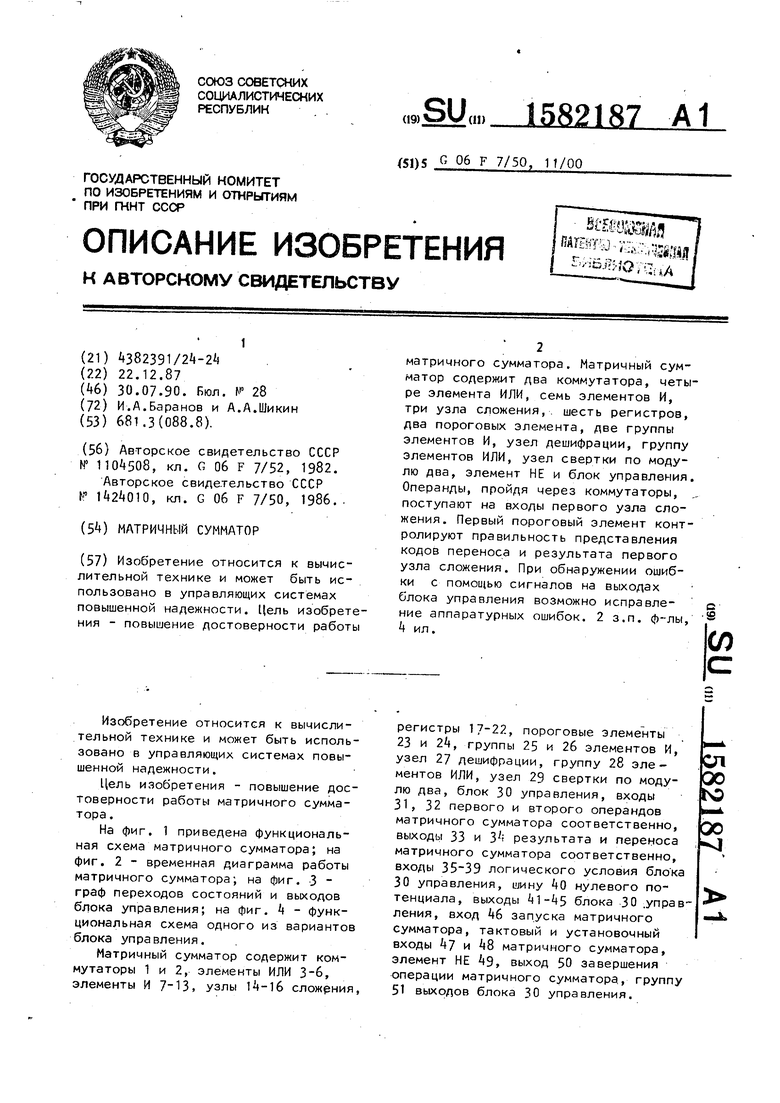

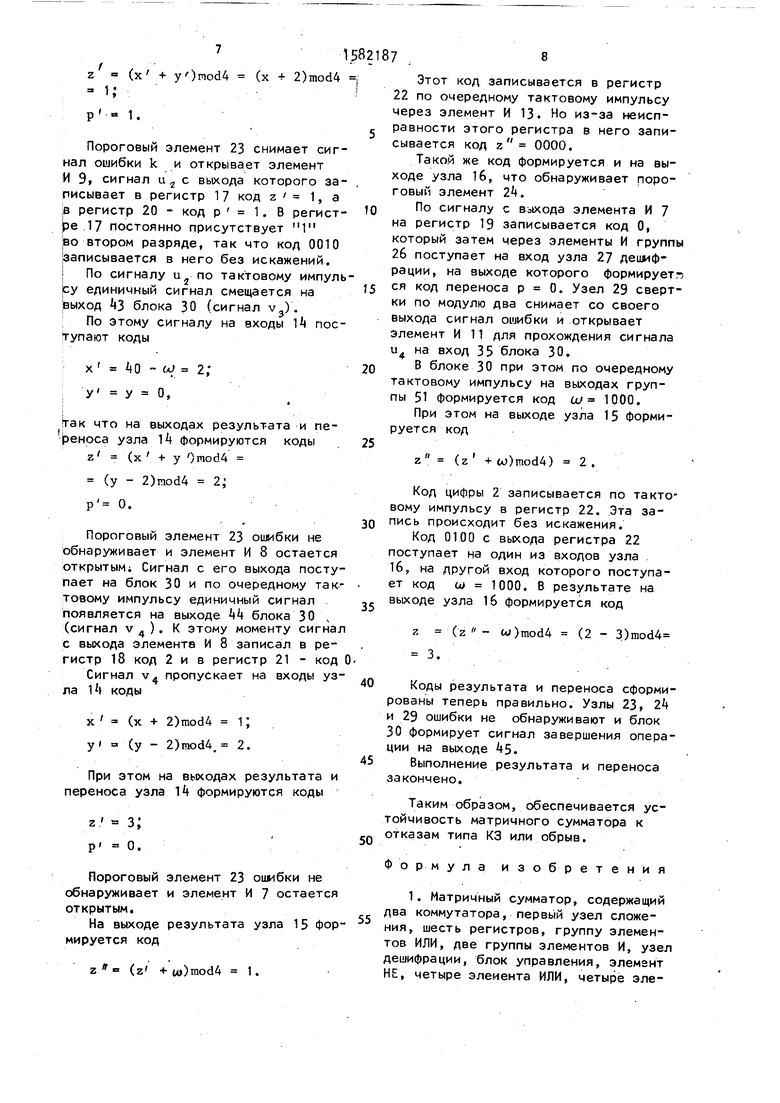

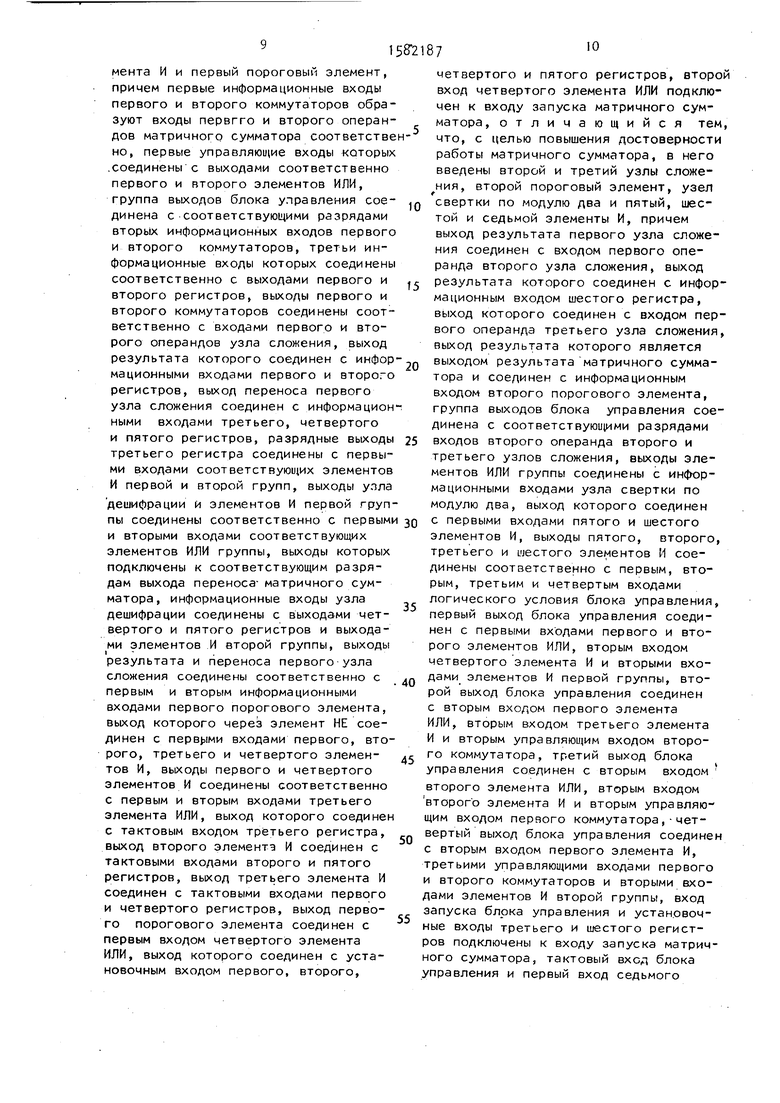

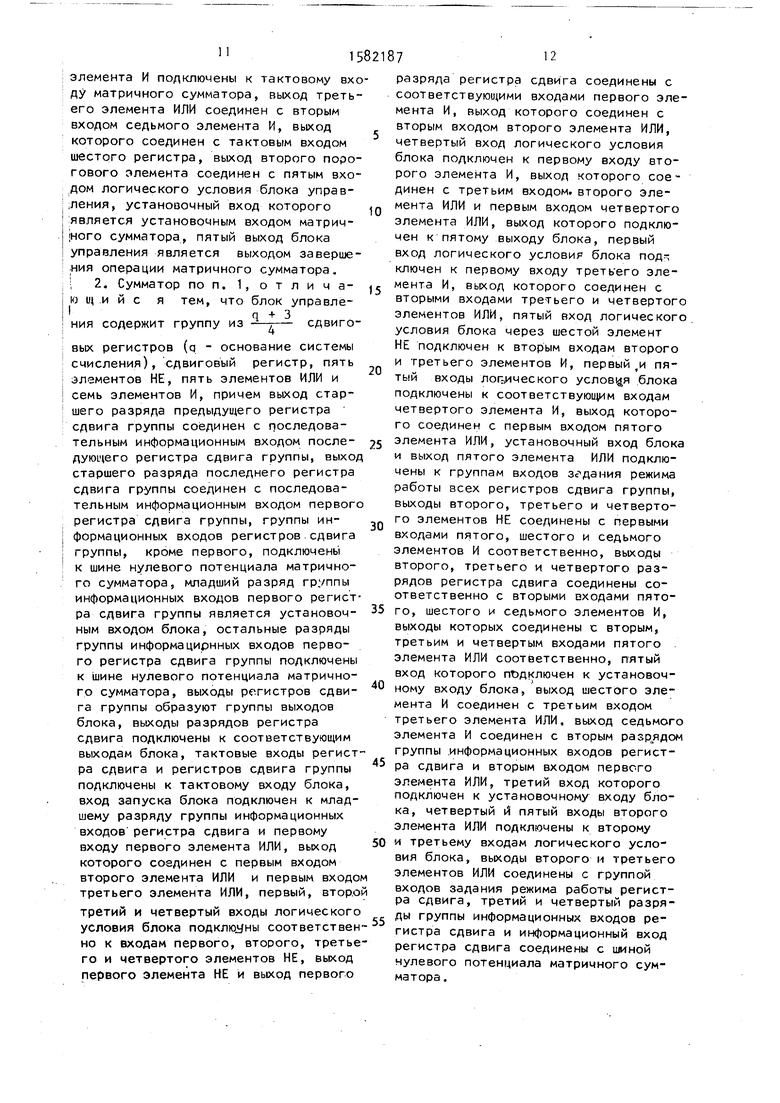

На фиг. 1 приведена функциональная схема матричного сумматора; на фиг. 2 - временная диаграмма работы матричного сумматора; на фиг. 3 граф переходов состояний и выходов блока управления; на фиг. 4 - функциональная схема одного из вариантов блока управления.

Матричный сумматор содержит коммутаторы 1 и 2, элементы ИЛИ , элементы И , узлы 14-16 сложения,

регистры 17-22, пороговые элементы 23 и 24, группы 25 и 26 элементов И, узел 27 дешифрации, группу 28 элементов ИЛИ, узел 29 свертки по модулю два, блок 30 управления, входы 31, 32 первого и второго операндов матричного сумматора соответственно, выходы 33 и 34 результата и переноса матричного сумматора соответственно, входы логического условия блока 30 управления, шину 40 нулевого потенциала, выходы 41-45 блока 30 .управления, вход 46 запуска матричного сумматора, тактовый и установочный входы 47 и 48 матричного сумматора, элемент НЕ 49, выход 50 завершения операции матричного сумматора., группу 51 выходов блока 30 управления.

Блок управления содержит группу

q + 3

52 из сдвиговых регистров, регистр 53 сдвига, элементы НЕ 54-58, элементы ИЛИ 59-63, группы элементов И 64-69, блок элементов И 70.

Первый пороговый элемент 23 контролирует наличие только одной единицы в кодах, поступающих на его первый или второй информационные входы. Второй пороговый элемент 2k контролирует наличие только одной единицы во входном коде.

Узел 27 дешифрации содержит три группы входов по два входа в каждом:

хм xfi 1 2 Ява вых°Да у г и описывается переключательными функциями:

у, (х„ И-х,4 л х13) V (х Л х,э) V (х±1лх Т1л х 13);

У xti

Л х23) V (х41

л х а2 л х

„) У(х4

/ х

1

Л X

13

Блок элементов И узла 14 сложения имеет q входов х . (i 1, ... q, где q - основание системы счисления), (q - 1) группу по j выходов у Л р

1, ... j, J 1, -.., q - 1) и описывается переключательными функциями

х J41 Л

И

Узлы 14-16 сложения позволяют складывать два q-разрядных числа с позиционным представлением цифр по модулю q.

Соединение разрядов группы 51 выходов блока 3 управления с разрядами входа второго операнда узла 16 позволяет осуществить вычитание с по- мощью узла 16. С этой целью первый разряд группы 51 выходов блока 3 соединен с первым разрядом входа второго операнда узла 16; к j-му разряду входа второго операнда узла 16 подключается (q + 2 - j)-u выход группы 51 блока 30 (j 2, ..., q).

Таким же образом происходит подключение разрядов группы 51 блока 30 к разрядам второго информационно-, го входа коммутатора 1, что позволяет осуществлять операцию вычитания с помощью узла 14.

5

Q

$

0

5

JQ

35

50

„

Матричный сумматор работает следующим образом.

При нахождении блока 30 управления в состоянии A (i 1, ..., q) на выходах группы 51 блока 30 формируется код с позиционным представлением цифры (J i - 1, а на выходах 41-44 блока 30 - код v 0000.

В случае, е.сли блок 30 находится в состоянии AJ( (j 1, ..., 4; i 1, ..., q), то на его выходах группы 51 формируется код с позиционным представлением цифры to -1, а на выходах 41-44 - код с позиционным представлением цифры v j - 1.

Рассмотрим работу матричного сумматора, например, для q 4, х 3 и у 0. Предположим, что сумматор не имеет ни одного физического отказа.

При начальной установке матричного сумматора на выходах группы 51 блока 30 управления устанавливается код w 0001, а на выходах Al-M блока 30 - код 0000.

При поступлении на входы 31 и 32 первого и второго операндов матричного сумматора кодов х 3, и у О, представленный в кодах с позиционным представлением цифр (сигналы х4 и у на фиг. 2) в матричный сумматор по входу 46 поступает сигнал запуска, который сбрасывает в нулевое состояние все регистры 17-22 (через элемент ИЛИ 6).

Блок 30 по сигналу запуска формирует на выходе k сигнал v (см. фиг. 2). Данный сигнал через элементы ИЛИ 3 и k поступает на первые управляющие входы коммутаторов 1 и 2 и разрешают прохождение операндов х 3 и у 0 на соответствующие входы первого узла 14 сложения (сигналы х 4. и у , на фиг. 2).

При этом на выходе результата узла 14 формируется код

z (х + y)mod4 3,

а на выходе переноса - сигнал р О

Первый пороговый элемент 23, не обнаружив ошибки в вычислении, снимает с выхода сигнал ошибки k/.

Код суммы поступает на вход первого операнда второго узла 15 сложения, на вход второго операнда которого подается сигнал to с выходов труппы 51 блока 30, определяющий код цифры w 0. На выходе узла 15 формируется код суммы

z (z + oo)mod4 3,

который по тактовому импульсу записывается в регистр 22. С выхода этого регистра код поступает на вход первого операнда третьего узла 16 сложения, на вход второго операнда которого подается код цифры to 0. На его выходе результата формируется код

z (z - w)mod4 3.

Одновременно с этим по сигналу и с выхода элемента ИЛИ 5 код переноса р 0 записывается в регистр 19, после чего через первую группу 25 элементов И поступает на входы элементов ИЛИ группы 28. Выходы элементов ИЛИ группы 28 подключены к соответствующим разрядам выхода 34 матричного сумматора, так что на выходе 34 Формируется код переноса р 0.

Код переноса и код результата поступают на входы соответственно узла 29 свертки по модулю два и второго порогового элемента 24. Предположим, что в работе матричного сумматора не ошибок. Тогда узлы 2k и 29 снимают с выходов сигналы ошибки k и k . При этом с выхода элемента И 12 CHI- нал и, поступает на вход 35 блока 30, который формирует сигнал на выходе 45 и снимает сигнал v1 с выхода 41 .

Пусть в матричном сумматоре возникли отказы, имеющие следующие проявления:

в четвертом разряде выхода результата узла 14 формируется О всякий

раз при х 3, у 0; во втором разряде регистра 17 - постоянная 1,. во втором разряде регистра 22 - посi

В этом случае после подачи сигнала запуска на вход 46 матричного сумматора блок 30 формирует на выходе 41 сигнал v Этот сигнал пропускает операнды через коммутаторы 1 и 2 входы узла 14 сложения (сигналы х

и У, ).

на i

4

В четвертом разряде выхода результата узла 14 сложения единичный сигнал не формируется. Это приводит

5S21876

к тому, что на выходе порогового элемента 23 остается сигнал ошибки. Элемент И 10 закрыт, запись в регист ры 19 и 22 не приводится и сигнал 5 и, на вход блока 30 не подается. По очередному тактовому импульсу на выходах группы 51 блока 30 устанавливается код (jj 0010, а единичный сигнал переходит с выхода 41 на выход

10

15

42 (сигнал v),

Сигнал v- пропускает через первый коммутатор 1 первый операнд х х 3, а через второй коммутатор 2 - код у w 1. установленный на группе 51 выходов блока 30. В результате, на выходах результата и переноса узла 14 формируются коды

20

(х 1.

+ y )mod4 (х + 1)

Пороговый элемент 23 снимает с выхода сигнал k и открывает элемент И 9, сигнал с выхода которого записывает в регистр 17 код суммы z О, а в регистр 20 - код переноса р 1. В регистре 17 по условию присутствует отказ и вместо кода 0001 в нем оказывается код 0011.

По сигналу u .J в блоке 30 с приходом тактового сигнала единичный сигнал смещается с выхода 42 на выход 43 (сигнал v э).

35

.

40

Сигнал v3 пропускает через второй коммутатор 2 код второго операнда у у 0, а через первый коммутатор 1 код х 4 - w 3.

Так как при этом единичный сигнал должен формироваться в неисправном разряде выхода результата узла 14, то пороговый элемент устанавливается на своем выходе сигнал ошибки k , кото- рый через элемент НЕ 49 закрывает элементы И 8 и ИЛИ 6 сбрасывает в нулевое состояние регистры 17, 18,

20 и 21 .

I

50

При снятии сигнала u 3 по очередному синхроимпульсу блок 30 устанавливает на выходах группы 51 код W 0100, и переводит единичный сигнал 55 на выход 42 (v ),

Этот сигнал пропускает на входы узла 14 коды х х 3 и у w 2.

На выходах результата и переноса узла 14 при этом имеются коды

i;

71582187

(x + y)mod4 (x 2)mod4 ,

Пороговый элемент 23 снимает сигнал ошибки k и открывает элемент И 9, сигнал иг с выхода которого записывает в регистр 17 код z 1, а в регистр 20 - код р 1. В регистре 17 постоянно присутствует 1 во втором разряде, так что код 0010 записывается в него без искажений. i По сигналу и по тактовому импульсу единичный сигнал смещается на выход блока 30 (сигнал v3).

По этому сигналу на входы 14 поступают коды

х 40 - 6J 2; у у О,

так что на выходах результата и переноса узла 14 формируются коды z (х + у Orood4

(у - 2)riod4 2; р 0.

Пороговый элемент 23 ошибки не обнаруживает и элемент И 8 остается открытым. Сигнал с его выхода поступает на блок 30 и по очередному тактовому импульсу единичный сигнал появляется на выходе 44 блока 30 ч (сигнал v 4). К этому моменту сигнал с выхода элемента

И 8 записал в реузгистр 18 код 2 и в регистр 21 - код Сигнал v4 пропускает на входы ла 14 коды

(х +

(у 2)mod4 : 2)mod4,

1;

При этом на выходах результата переноса узла 14 формируются коды

з;

0.

Пороговый элемент 23 ошибки не обнаруживает и элемент И 7 остается открытым.

На выходе результата узла 15 формируется код

z (z u))tnod4 1«

8

0

5

0

5

0

35

40

45

50

55

Этот код записывается в регистр 22 по очередному тактовому импульсу через элемент И 13. Но из-за неисправности этого регистра в него записывается код z 0000.

Такой же код формируется и на выходе узла 16, что обнаруживает пороговый элемент 24.

По сигналу с элемента И 7 на регистр 19 записывается код О, который затем через элементы И группы 26 поступает на вход узла 27 дешифрации, на выходе которого формируете ся код переноса р 0. Узел 29 свертки по модулю два снимает со своего выхода сигнал ошибки и открывает элемент И 11 для прохождения сигнала и4 на вход 35 блока 30.

8 блоке 30 при этом по очередному тактовому импульсу на выходах группы 51 формируется код ш 1000.

При этом на выходе узла 15 формируется код

z (z + w)mod4) 2 .

Код цифры 2 записывается по тактовому импульсу в регистр 22. Эта запись происходит без искажения.

Код 0100 с выхода регистра 22 поступает на один из входов узла 16, на другой вход которого поступает код о 1000. В результате на выходе узла 16 формируется код

z (z - w)mod4 (2 - 3)mod4 3.

Коды результата и переноса сформированы теперь правильно. Узлы 23, 24 и 29 ошибки не обнаруживают и блок 30 формирует сигнал завершения операции на выходе 45.

Выполнение результата и переноса закончено.

Таким образом, обеспечивается устойчивость матричного сумматора к отказам типа КЗ или обрыв.

Формула изобретения

у

мента И и первый пороговый элемент, причем первые информационные входы первого и второго коммутаторов образуют входы первгго и второго операндов матричного сумматора соответств но, первые управляющие входы которы соединены с выходами соответственно первого и второго элементов ИЛИ, группа выходов блока управления соединена с соответствующими разрядами вторых информационных входов первог и второго коммутаторов, третьи информационные входы которых соединен соответственно с выходами первого и второго регистров, выходы первого и второго коммутаторов соединены соответственно с входами первого и второго операндов узла сложения, выход результата которого соединен с инфомационными входами первого и второг регистров, выход переноса первого узла сложения соединен с информациоными входами третьего, четвертого и пятого регистров, разрядные выход третьего регистра соединены с первыми входами соответствующих элементо И первой и второй групп, выходы улла дешифрации и элементов И первой группы соединены соответственно с первым и вторыми входами соответствующих элементов ИЛИ группы, выходы которых подключены к соответствующим разрядам выхода переноса- матричного сумматора, информационные входы узла дешифрации соединены с выходами четвертого и пятого регистров и выходами элементов И второй группы, выходы результата и переноса первого узла сложения соединены соответственно с первым и вторым информационными входами первого порогового элемента, выход которого через элемент НЕ соединен с первыми входами первого, второго, третьего и четвертого элементов И, выходы первого и четвертого элементов И соединены соответственно с первым и вторым входами третьего элемента ИЛИ, выход которого соедине с тактовым входом третьего регистра, выход второго элемента И соединен с тактовыми входами второго и пятого регистров, выход третьего элемента И соединен с тактовыми входами первого и четвертого регистров, выход первого порогового элемента соединен с первым входом четвертого элемента ИЛИ, выход которого соединен с установочным входом первого, второго,

10

-5

10

f5

20

25

зо

35

40

45

0

5

четвертого и пятого регистров, второй вход четвертого элемента ИЛИ подключен к входу запуска матричного сумматора, отличающийся тем, что, с целью повышения достоверности работы матричного сумматора, в него введены второй и третий узлы сложения, второй пороговый элемент, узел свертки по модулю два и пятый, шестой и седьмой элементы И, причем выход результата первого узла сложения соединен с входом первого операнда второго узла сложения, выход результата которого соединен с информационным входом шестого регистра, выход которого соединен с входом первого операнда третьего узла сложения, выход результата которого является выходом результата матричного сумматора и соединен с информационным входом второго порогового элемента, группа выходов блока управления соединена с соответствующими разрядами входов второго операнда второго и третьего узлов сложения, выходы элементов ИЛИ группы соединены с информационными входами узла свертки по модулю два, выход которого соединен с первыми входами пятого и шестого элементов И, выходы пятого, второго, третьего и шестого элементов И соединены соответственно с первым, вторым, третьим и четвертым входами логического условия блока управления, первый выход блока управления соединен с первыми входами первого и второго элементов ИЛИ, вторым входом четвертого элемента И и вторыми входами элементов И первой группы, второй выход блока управления соединен с вторым входом первого элемента ИЛИ, вторым входом третьего элемента И и вторым управляющим входом второго коммутатора, третий выход блока управления соединен с вторым входом второго элемента ИЛИ, вторым входом второго элемента И и вторым управляющим входом первого коммутатора,-четвертый выход блока управления соединен с вторым входом первого элемента И, третьими управляющими входами первого и второго коммутаторов и вторыми входами элементов И второй группы, вход запуска блока управления и установочные входы третьего и шестого регистров подключены к входу запуска матричного сумматора, тактовый вход блока управления и первый вход седьмого

111582187

емента И подключены к тактовому вхоматричного сумматора, выход третьо элемента ИЛИ соединен с вторым одом седьмого элемента И, выход торого соединен с тактовым входом стого регистра, выход второго порового элемента соединен с пятым вхом логического условия блока управния, установочный вход которого ляется установочным входом матрич- го сумматора, пятый выход блока равления является выходом завершея операции матричного сумматора.

10

15

я содержит группу из

сдвигорс ме в ч бл р ди ме эл че вх кл ме вт эл ус Н и ты по че го эл и че ра вы го вх эл вт ря от го вы тр эл вх но ме тр эл гр ра эл по ка эл 50 и ви эл вх ра

вых регистров (q - основание системы счисления), сдвиговый регистр, пять элементов НЕ, пять элементов ИЛИ и семь элементов И, причем выход старшего разряда предыдущего регистра сдвига группы соединен с последовательным информационным входом последующего регистра сдвига группы, выход старшего разряда последнего регистра сдвига группы соединен с последовательным информационным входом первого регистра сдвига группы, группы информационных входов регистров сдвига группы, кроме первого, подключены к шине нулевого потенциала матричного сумматора, младший разряд группы информационных входов первого регистра сдвига группы является установочным входом блока, остальные разряды группы информацирнных входов первого регистра сдвига группы подключены к шине нулевого потенциала матричного сумматора, выходы регистров сдвига группы образуют группы выходов блока, выходы разрядов регистра сдвига подключены к соответствующим выходам блока, тактовые входы регист ра сдвига и регистров сдвига группы подключены к тактовому входу блока, вход запуска блока подключен к младшему разряду группы информационных входов регистра сдвига и первому входу первого элемента ИЛИ, выход которого соединен с первым входом второго элемента ИЛИ и первым входом третьего элемента ИЛИ, первый, второй

третий и четвертый входы логического

20

5

разряда регистра сдвига соединены с соответствующими входами первого эл мента И, выход которого соединен с вторым входом второго элемента ИЛИ, четвертый вход логического условия блока подключен к первому входу вто рого элемента И, выход которого сое динен с третьим входом, второго элемента ИЛИ и первым входом четвертог элемента ИЛИ, выход которого подклю чен к пятому выходу блока, первый вход логического условия блока подключен к первому входу третьего эле мента И, выход которого соединен с вторыми входами третьего и четверто элементов ИЛИ, пятый вход логическо условия блока через шестой элемент НЕ подключен к вторым входам второго и третьего элементов И, первый пятый входы логического условия блока подключены к соответствующим входам четвертого элемента И, выход которого соединен с первым входом пятого элемента ИЛИ, установочный вход блок и выход пятого элемента ИЛИ подключены к группам входов згдания режима работы всех регистров сдвига группы, выходы второго, третьего и четвертого элементов НЕ соединены с первыми входами пятого, шестого и седьмого элементов И соответственно, выходы второго, третьего и четвертого разрядов регистра сдвига соединены соответственно с вторыми входами пятого, шестого и седьмого элементов И, выходы которых соединены с вторым, третьим и четвертым входами пятого элемента ИЛИ соответственно, пятый вход которого подключен к установочному входу блока, выход шестого элемента И соединен с третьим входом третьего элемента ИЛИ, выход седьмог элемента И соединен с вторым разрядо группы информационных входов регистра сдвига и вторым входом первого элемента ИЛИ, третий вход которого подключен к установочному входу блока, четвертый и пятый входы второго элемента ИЛИ подключены к второму 50 и третьему входам логического условия блока, выходы второго и третьего элементов ИЛИ соединены с группой входов задания режима работы регистра сдвига, третий и четвертый разря30

35

40

45

--------- - гс ды группы информационных входов ре- условия блока ПОДКЛЮЧУ соответствен- гистра сдвига и информационный но к входам первого, второго, третьего и четвертого элементов НЕ, выход первого элемента НЕ и выход первого

регистра сдвига соединены с шиной нулевого потенциала матричного сумматора .

12

0

5

0

5

разряда регистра сдвига соединены с соответствующими входами первого элемента И, выход которого соединен с вторым входом второго элемента ИЛИ, четвертый вход логического условия блока подключен к первому входу второго элемента И, выход которого соединен с третьим входом, второго элемента ИЛИ и первым входом четвертого элемента ИЛИ, выход которого подключен к пятому выходу блока, первый вход логического условия блока подключен к первому входу третьего элемента И, выход которого соединен с вторыми входами третьего и четвертого элементов ИЛИ, пятый вход логического условия блока через шестой элемент НЕ подключен к вторым входам второго и третьего элементов И, первый пятый входы логического условия блока подключены к соответствующим входам четвертого элемента И, выход которого соединен с первым входом пятого элемента ИЛИ, установочный вход блока и выход пятого элемента ИЛИ подключены к группам входов згдания режима работы всех регистров сдвига группы, выходы второго, третьего и четвертого элементов НЕ соединены с первыми входами пятого, шестого и седьмого элементов И соответственно, выходы второго, третьего и четвертого разрядов регистра сдвига соединены соответственно с вторыми входами пятого, шестого и седьмого элементов И, выходы которых соединены с вторым, третьим и четвертым входами пятого элемента ИЛИ соответственно, пятый вход которого подключен к установочному входу блока, выход шестого элемента И соединен с третьим входом третьего элемента ИЛИ, выход седьмого элемента И соединен с вторым разрядом группы информационных входов регистра сдвига и вторым входом первого элемента ИЛИ, третий вход которого подключен к установочному входу блока, четвертый и пятый входы второго элемента ИЛИ подключены к второму 50 и третьему входам логического условия блока, выходы второго и третьего элементов ИЛИ соединены с группой входов задания режима работы регистра сдвига, третий и четвертый разря0

35

40

45

ды группы информационных входов ре- гистра сдвига и информационный

регистра сдвига соединены с шиной нулевого потенциала матричного сумматора .

у- П

30

46 47 40 50

Фиг.1

LQlZQSl

w i т t г

fffl J as и, 4

Ы1 иг I

f

l@я

JS

§

Авторы

Даты

1990-07-30—Публикация

1987-12-22—Подача