1

Изобретение относится к вычислительной технике и может быть использовано в управляющих ЦВМ объектов, к которым предъявляются повышенные требования к достоверности переработки информации.

Целью изобретения является повышение надежности путем сообщения сумматору свойства отказоустойчивости.

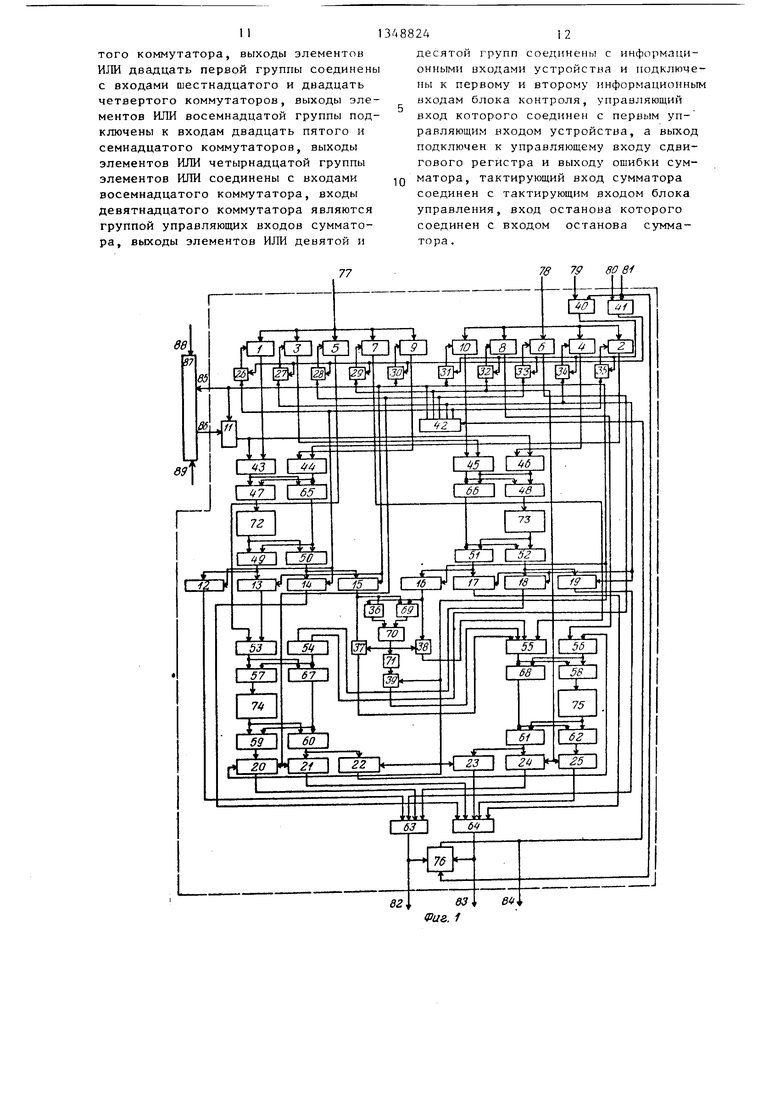

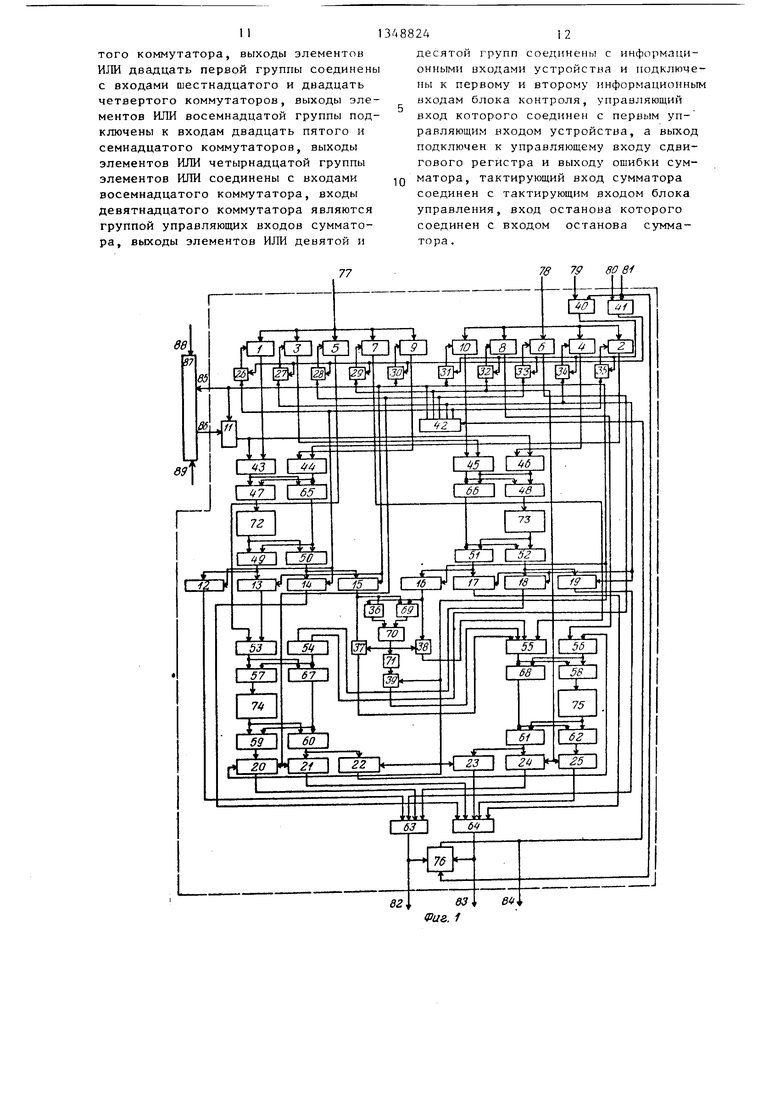

На фиг. 1 представлена функционалная схема матричного сумматора; на фиг. 2 - пример выполнения блока управления; на фиг. 3 - граф переходов состояний блока управления.

Матричный сумматор (фиг. 1) содержит коммутаторы 1-25, элементы И 26- 39, элементы ИЛИ 40, 41, сдвиговый регистр 42, группы элементов ИЛИ 43- 64, группы элементов И 65-68, элементы ИЛИ-НЕ 69, 70, элемент НЕ 71, блоки элементов И 72-75, блок 76 контроля, информационные входы 77, 78, сумматора, управляющие входы 79-81 сумматора, информационные выходы 82, 83, выход 84 ошибки, вход 85 пуска блока управления, группа выходов 86 блока управления, блок 87 управления вход 88 останова сумматора, тактовый вход 89 сумматора.

Блок управления (фиг. 2) содержит триггер 90-93, элементы И 94-96, элементы НЕ 97, 98, элемент ИЛИ 99, элемент 3-2 И-ИЛИ ЮС.

На фиг. 3 изобра ;ены состояния А блока управления, где i 1, g, g - основания системы счисления, на дугах указаны условия переходов.

Группы элементов ИЛИ 43, 44, 46, 47, 53, 54, 57, 58 имеют по две группы по g входов X , х (i 1, ...-, g), где g - основание системы счислений, g выходов у и описываются переключательными функциями У X,, V х,

Группы элемйнтов ИЛИ 49, 59, 61 имеют по g групп по j входов х (i 1 , . . . , j , j 1, ..., g), g выходов у ( P 1, ..., g) и описываются переключательными функциями Ч J

У (V V

1 i-.

.64 Я

, - р

Xg и X определены для нечет|U

р . j

а Ы и 1 удонлетворяют равенству (-i + (Ч - I )modg (

3488242

Группа элементов ИЛИ 52 имеет g+1 группу входов, из которых g групп имеют по j входов х. (i 1, ..., g j , j 1 , . . . , g) , a одна группа - g входов x,,(i 1, .. ., g), g выходов у ( ,t( 1 , . . . , g) и описывается переключательными функциями

10 r . , VXg,vx,

8л t, определены для

нечетный /j

8 -ni-I-, Y , ,

H- 1

2

a di и (3 удовлетворяют равенству

( i ч- (5-1 )modg f4 . Группы элементов ИЛИ 50, 60, 61 имеют по g групп по j входов х ( , . . , j ; j 1 , ..., g), два выхода у , у и описываются переключательными функциями:

J 412 У. ( V V X,. ) V X

1)

%

/ у (V X )V X

,.1 -

J «; t t

где { и удовлетворяют неравенству

4 -t- 1 i g -t- 1 .

Группа элементов ИЛИ 51 имеет g+1 групп входов, из которых g групп имеют по j входов х (i 1, ..., j; j 1, ..., g), a одна группа g

входов x,, (i 1, ..., g) , g выходов у ( , ...,g)и ОПИСЫ0

0

l.t) ч

5

вается переключательными функциями:

J 14 у ( V V X ) V X . 1 , 1 -1 j-- 1

J I i,,.r

где и vi удо1 летворяют неравенству

-- g + 1.

Группа элементов ИЛИ 55 имеет две групиы входов X , X , (i - 1

11. 2

8 J 1-3) и g выходов у .

Vf, , ( 3, ..., g-1),

11 ,

V- Y

У X V Х,,

х„. V X,

41Т 7

Группа элементов Ш1И 56 имеет две :руппы Бходои х , У, fi 1, .,., g, j 1, 2) и g выходов У .

УЯ ., (М ..., g),

-Л п Yvi

УГ, Х, V у,.

Группа элементов ИЛИ 45 имеет две группы по g входов х. , х,2 Ci 1, , g), g+1 выход у (j 1, ..., g+1) и описывается переключательными функциями:

/. , V -1,2, j 2. , g),

У1 11

Ус,1 f

Группа элементов ИЛИ 48 имеет две группы входов х , х, (i 1, ..., g; J 1, ., g+1), g+1 выход y (, ...,g+1)и описывается переключательными функциями У,а х V Х,.

Группа элементов ИЛИ 63 имеет четыре группы по g входов х, ( gj j 1. ). g выходов и описывается переключательными функциями

V V X t i i J

Группа элементов ИЛИ 64 имеет пять групп по два входа х (, 2, J 1, ..., 5), два выхода у и описывается переключательными функциями5

У. ,У, jГруппы элементов И 65-68 имеют по две группы по g входов х ,

(1 1, ..,, g), g выходов у

и списываются переключательными функциями

У, X,,

Ч

Блоки элементов И 72-75 имеют g входов х (1 1, ,.., g) g-1 групп по j выходов у (н 1, -, j, j 1, ..., g-1) и описываются переключательными функциями

у, Xj, л .

Блок элементов И 73 имеет g+1 вхо х (1 1, ..., g+1), g групп по j выходов у ( р 1, .. ., j; j 1 , ..., g) и описывается переключательными функциями

ц f + Блок 76 контроля имеет две группы

входов X i, , х,, (1 1 , . . . , g; j 1, 2), управляющий вход а, выход у и описывается переключательной функцией

,1 г.пп) Ч о si(.. 2)

V(x, л

Х,п)

2,г

Матричный сумматор функционирует в пяти режимах, каждый из которых оп

,

3488244

ределястгя числом отказов, содержа- игчхся в сумматоре .

Выбор того или иного режима производится блоком 76 контроля, который при обнаружении логической ошибки в кодах суммы z и переноса Р сдвигается на один разряд единицу в сдвиговом регистре 42. При этом наличие

1Q единицы в 1-м разряде (1 1, . . . ,5) сдвигового регистра 42 соответствует 1-му режиму функционирования матричного сумматора. В начальный момент времени единица устанавливается в

15 первый разряд сдвигового регистра 42 с входа начальной установки.

В первом режиме при поступлении на входы 77, 78 матричного сумматора кодов операндов х и у совместно с

2Q сигналами сопровождения на входах 79, 80 и признаком операции на входе 81 коды операндов через коммутаторы 1 и 10 поступают на первые группы входов групп элементов ИЛИ 43, 44. При

25 этом на выходах группы элементов ИЛИ 49 будет сформирован код числа

Z (x+y)raodg,

а на выходах группы элементов ИЛИ 50 код числа

30 р 1 Р + У g

1 при X + у g

Коды этих чисел z и Р через коммутаторы 12, 14 и группы элементов ИЛИ 63, 64 поступают на выходы 82,

83 матричного сумматора, где они контролируются блоком 76 контроля.

При получении неискаженных кодов суммы z и Р блок 76 контроля не формирует сигнал на своем выходе и crfrнал ошибки на выход 84 не поступает. В противном случае сигнал ошибки сдвигает единицу из первого разряда сдвигового регистра 42 в его второй разряд, что соответствует переключению сумматора во второй режим. В этом режиме открытыми окажутся коммутаторы 2, 8, 17 и 19. Коды операндов х и у через входные клапаны 2 и 8 поступают на первые группы входов групп элементов ИЛИ 45, 46. При этом коды суммы и переноса Р будут получены соответственно на выходах групп элементов ЛИ 52, 51 и через открытые коммутаторы 17, 19 и группы элементов ИЛИ

63, 64 -поступят на выходы 83, 82 матричного сумматора.

При обнаружении блоком 76 контроя в полученных во втором режиме ко

дах z и Р ошибки единица в сдвиговом регистре 42 сдвигается из второго в третий разряд. В третьем режиме для кодов входных операндов х и у будут открыты коммутаторы 5 и 6, выход которых подключены к первым группам входов групп элементов ИЛИ 53 и 54 соответственно. В результате данного изменения режима работы матричного сумматора коды суммы z и переноса Р будут получены на выходах групп элементов ИЛИ 59, 60 и через открытые коммутаторы 20, 21 и группы элементов ИЛИ 63, 64 поступят на выходы 82 83 матричного сумматора.

Обнаружение блоком 76 контроля ошибки в кодах z и Р в третьем режим приводит к сдвигу единицы из третьго в четвертый разряд сдвигового регистра 42, что соответствует переключению матричного сумматора из третьего в четвертый режим. В этом режиме открытыми оказываются коммутаторы 4, 7, 24 и 25. При этом коды операндов X и у через входные коммутаторы 4 и 7 поступают на первые группы входов групп элементов ИЛИ 55, 56, а коды суммы z и Р - на выходы 82, 83 матричного сумматора с выходов групп элементе.i ИЛИ 62, 61 через коммутаторы 25, 24 и гругты элементов ИЛИ 63,6

В том случае, если блок 76 контроля обнаружит ошибку в кодах чисел z и Р, сигнал с его чыхода переведет матричный сумматор из четвертого режима в пятый. Этот режим характеризуется совместной работой всех групп элементов ИЛИ 43-46, групп элементов И 65-68 и блоком элементов И 72-75.

В пятом режиме код операнда х через коммутатор 9 поступает на вторые группы входов группы элементов ИЛИ 44, а код операнда у через коммутатор 2 - на вторые группы входов группы элементов ИЛИ 45. Кроме того, через коммутатор 11 на вторые группы входов групп э.пементов ИЛИ 43, 46 потупает код управляющего операнда U. Формирование этих кодов производится с помощью блока 87, построенного на основе регистра с перемещаемой единице ft .

Функции розбуждения блока 87, как это показано на фиг. 3, построены на одном логическом ллеме.нте 3-2И-И11И, одном логическс м элементе ИЛИ на g

входов, g торных.

элементах 2 И и двух инвегры,

13488246

Внешними сигналами блока 87 являются сигнал пуска, поступаюа(ий с выхода матричного сумматора, а также сиг

тупающие соответственно на входы 88 и 89.

Таким образом, на выходах блока 87 последовательно формируются коды управляющих операндов U i - О, 1,2, ..., g-1. О, 1, 2, ..., g-1, ...

Коды этих операндов через группу элементов ИЛИ 43 поступают на первые входы группы элементов ИЛИ 47 и группы элементов И 65 в прямом виде, т.е. на выходах группы элементов ИЛИ 43 формируются коды чисел U .

Т - II

Ц - и,- ,

и через группу элементов ИЛИ 46 - на первые входы группы элементов ИЛИ 48 и группы элементов И 66 в инверсном виде. В- результате, на выходах группы элементов ИЛИ 46 формируются коды чисел и,

I g - и - ° 1 Такое представление управляющего

операнда позволяет получить на выходах групп элементов ИЛИ 49, 50 коды сумм z с сигналами Z. (х

Р

1

а на выходах элементов коды разностей г

Z. (у

Р

и) modg,

0при у - и, 7, 0

1при у

- и 0.

Коды чисел z

и z через коммутаторы 13 и 18 поступают на вторые группы входов групп элементов ИЛИ 53, 54. При этом на выходы 82 матричного сумматора через коммутатор 20 и группу элементов ИЛИ 63 поступают коды сумм z z (z + z ) modg ((x + + U, ) modg (y - Ц ) modg)modg (x -t- y) modg 7.. I

Кроме Toi o, на вторую группу вхо;ioH группы элементов ИЛИ 56 поступа- код переноса

I О при ( )modg+(y - р LI, ) raodg V g;

I 1 при (х + i , ) modg -ь - (у - L ) niodg , g ,

Сиг иалы, соотнстствующие позиции едикиць: в коплх цифр р , р| , через

коммутаторы 15 и 16 поступают на соответствующие входы элементов И 36- 38 и элемента ИЛИ-НЕ 69. В том случае, если оба эти сигнала равны О или 1, на выходе элемента ИЛИ-НЕ 70 будет нулевой сигнал, а на выходе элемента И 39 - единичный. При этом на выходе группы элементов ИЛИ 55 будет получен код числа 0.

В том случае, если единичный сигнал присутствует только на выходе коммутатора 15, открытым окажется элемент И 37. При этом на выходе группы элементов ИЛИ 55 получен код 1. При наличии единичного сигнала лишь на выходе коммутатора 16 сигнал с его выхода через элемент И 38 формирует на выходе группы элементов ИЛИ 55 ко числа g-1.

Таким образом, данное представление цифр Р. и Р на выходах группы элементов ИЛИ 55 позволяет получить на выходах группы элементов ИЛИ 61 код переноса Р

+ Р

- Р

Р

производится до тех пор 76 контроля не снимет сигкоторый через коммутатор 23 и группу элементов ИЛИ 6А поступает на выходы 83 матричного сумматора.

Получение на выходах 82 и 83 кодов чисел Z и Р; пока блок нал ошибки с выхода 84.

Таким образом, введенные функциональные элементы и их связи позволяют получать неискаженный код суммы на выходах матричного сумматора при наличии в нем не менее четырех отказов. Это обеспечивается за счет изменения управляющего операнда, или иными словами, за счет изменения представления операндов х и у, что приводит к задействованию после каждого такого изменения других элементов и шин сумматора, а следовательно, и к парированию их отказов.

Как показывают результаты анализа предлагаемого технического решения, среднее число отказов в данном сумматоре, после которого последний считается не работоспособным для g 2, ,, соответственно равно 5, 12, 19 и 26.

Формула изобретения

Матричный сумматор, содержащий два элемента ИЛИ, первый, второй, третий и четвертый коммутаторы, первую груп

5

0

5

0

5

0

5

0

5

пу элементов ИШ1, первую группу элементов И и первый блок элементов И, причем первый управляющий вход сумматора соединен с первыми входами первого и второго элементов ИЛИ, вторые входы которых соединены соответственно с вторым и третьим управляющими входами сумматора, информационные входы первого и второго коммутаторов соединены соответственно с первым и вторым входами сумматора, выходы элементов ИЛИ первой группы соединены соответственно с входами первого блока элементов И, отличающийся тем, что, с целью повышения надежности, в него введены коммутаторы с пятого по двадцать пятый, четырнадцать элементов И, сдвиговый регистр, группы элементов ИЛИ с второй по двадцать вторую, группы элементов И с второй по четвертую, два элемента ИЛИ-НЕ, элемент НЕ, блок управления, блоки элементов И с второго по пятый и блок контроля, причем первые информационные входы сумматора подключены к информационным входам третьего, четвертого, пятого и шестого коммутаторов, второй информационный вход сумматора подключен к информационным входам седьмого, восьмого, девятого и десятого коммутаторов, управляющие входы коммутаторов с первого по десятый соединены с выходами соответственно с первого по десятый элементов И, первые входы элементов И с первого по пятый и с шестого по десятый подключены к выходам соответственно первого и второго элементов ИЛИ, вторые входы i-x элементов И (i 1, 3, 5, 7, 9) соединены соответственно с (1+1)/2-ми выходами сдвигового регистра, а вторые входы j-x элементов И (j 2, 4, 6, 8, 10) соединены соответственно с i/2-ми выходами сдвигового регистра, первый выход сдвигового регистра подключен к управляющим входам одиннадцатого, двенадцатого коммутаторов, второй выход сдвигового регистра подключен к управляющим входам тринадцатого и четырнадцатого коммутаторов, третий выход сдвигового регистра подключен к управляющим входам пятнадцатого и шестнадцатого коммутаторов, четвертый выход сдвигового регистра подключен к управляющим входам семнадцатого и восемнадцатого коммутаторов, пятый выход сдвигового регистра подключрн

9

к управляющим входам девятнадцатого, двадцатого, двадцать первого, двадцать второго, двадцать третьего,двадцать четвертого, двадцать пятого коммутаторов, к первому входу одиннадцатого элемента И и входу пуска блока управления, выходы первого, второго, третьего, седьмого, четвертого, восьмого, пятого, девятого коммутаторов соединены с первыми входами элементов ИЛИ соответственно с первой по восьмую группу, выходы шестого и десятого коммутаторов соединены с вторыми входами элементов ИЛИ соответственно третьей и четвертой групп, выходы девятнадцатого коммутатора соединены с вторыми входами элементов ИЛИ первой и четвертой групп, выходы одиннадцатого коммутатора подключены к первым входам элементов ИЛИ девятой группы, выходы двадцатого коммутатора соединены с вторыми входами элементов ИЛИ пятой группы, выходы двадцатого коммутатора подключены к первым входам элементов ИЛИ десятой группы, выход двадцать первого коммутатора соединен с первыми входами двенадцатого, тринадцатого элементов И, первого элемента ИЛИ-НЕ выход двадцать второго коммутатора подключен к первому входу четырнадцатого элемента И и вторым входам тринадцатого элемента И и первого элемента ИЛИ-НЕ, выходь тринадцатого коммутатора соединены с вторыми входами элементов ИЛИ десятой группы, выходы двадцатО третьего коммутатора подключены к вторым входам элементов ИЛИ шестой группы, выходы четырнадцатого коммутатора соединены с вторыми входами элементов ИЛИ девятой группы, выходы пятнадцатого коммутатора подключены к третьим входам элементов ИЛИ девятой группы, выходы шестнадцатого коммутатора соединены с третьими входами элементов ИЛИ десятой группы, выходы двадцать четвертого коммутатора подключены к вторым входам элементов ИЛИ восьмой группы, выходы двадцать пятого коммутатора соединены с четвертыми входами элементов ИЛИ десятой группы, выходы семнадцатого коммутатора подключены к чет вертым входам элементов ИЛИ девятой группы, выходы восемнадцатого коммутатора соединены с пятыми входами элементов ИЛИ десятой группы, выходы тринадцатого элемента И и первого

0

4882410

элемента ИЛИ-НЕ через второй элемент ИЛИ-НЕ подключены к вторым входам двенадцатого и четырнадцатого элементов И и входу элемента НЕ, выход которого через одиннадцатый элемент И подключен к первому входу второй группы входов элементов ИЛИ седьмой группы, второй и третий входы второй групQ пы входов которой соединены с выходами двенадцатого и четырнадцатого элементов И соответственно, выходы элементов ИЛИ первой группы подключены к первым входам элементов И первой

g группы и элементов ИЛИ одиннадцатой группы, вторые входы которых соединены с выходами элементов ИЛИ второй группы, выходы элементов ИЛИ третьей группы подключены к первым входам элементов И второй группы и элементов ИЛИ двенадцатой группы, вторые входы которых соединены с выходами элементов ИЛИ четвертой группы, выходы элементов ИЛИ пятой группы подключены к

5 первым входам элементов ИЛИ тринадцатой группы и элементов И третьей группы, вторые группы входов которых соединены с выходами элементов ИЛИ шестой группы, выходы элементов ИЛИ седьмой группы подключены к первым входам элементов И четвертой группы и элементов И-ЛИ четырнадцатой группы, вторые входы которых соединены с выходами элементов ИЛИ восьмой группы, выходы элементов И с первой по четвертую групп соединены с первыми входами элементов ИЛИ соответственно пятнадцатой, шестнадцатой, семнадцатой и восемнадцатой групп и соответственно девятнадцатой, двадцатой, двадцать первой, четырнадцатой групп, вторые входы которых соединены с выходами блоков элементов И соответственно с первого по четвертый, входы второго, третьего, четвертого блоков элементов И соединены с выходами элементов ИЛИ соответственно двенадцатой, тринадцатой, двадцать второй групп, выходы элементов ИЛИ пятнадцатой, девятна;-;цатой, шестнадцатой, двадцатой групп соединены с информа- ционнь :-п: входами соответственнс один- над ;н1 ::1Го, ;,евятнадиатого, десятого и Л -пятого коммутаторов, с ннформа- (инымн входами соответственно двад- и.чтого, одиннадцатого, девятнадцатого, десятого коммутаторов, выходы элемен- TCJB ИЛИ семнадцатой гр/ппы подключены к информационм41м 1 ходам пятиадца0

5

0

5

0

Ь

того коммутатора, выходы элементов ИЛИ двадцать первой группы соединены с входами шестнадцатого и двадцать четвертого коммутаторов, выходы элементов ИЛИ восемнадцатой группы подключены к входам двадцать пятого и семнадцатого коммутаторов, выходы элементов ИЛИ четырнадцатой группы элементов ИЛИ соединены с входами восемнадцатого коммутатора, входы девятнадцатого коммутатора являются группой управляющих входов сумматора, выходы элементов ИЛИ девятой и

1348824

десятой групп соединены с информационными входами устройства и подключены к первому и второму информационным входам блока контроля, управляющий вход которого соединен с первым уп- равляющим входом устройства, а выход подключен к управляющему входу сдвигового регистра и выходу ошибки сумматора, тактирующий вход сумматора соединен с тактирующим входом блока управления, вход останова которого соединен с входом останова сумматора .

78 79 80 8-f

Фив. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричный сумматор | 1987 |

|

SU1582187A1 |

| Матричный сумматор | 1986 |

|

SU1424010A1 |

| Устройство для вычитания | 1987 |

|

SU1418703A1 |

| Устройство для вычисления функций в модулярном коде | 1985 |

|

SU1278839A1 |

| Матричный сумматор | 1987 |

|

SU1545217A1 |

| Вычислительное устройство | 1981 |

|

SU1136147A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU911519A1 |

| Вычислительное устройство | 1983 |

|

SU1080135A1 |

| Устройство для умножения | 1988 |

|

SU1615706A1 |

| Матричное вычислительное устройство | 1978 |

|

SU750485A1 |

Изобретение относится к цифровой вычислительной технике. Цель изобретения - повышение надежности матричного сумматора. С этой целью матричный сумматор содержит два элемента ИЛИ, группы элементов ИЛИ, группы элементов И, блоки элементов И, элемент НЕ, коммутаторы, регистр сдвига, блок контроля, блок управления, 3 ил. 00. 00 оо ND 4

86-(ji

Редактор Н.Слободяник

Составитель М.Есенина Техред А. Крчзчук Корректор М.Демчик

Заказ 5191/48Тираж 670 Подписное

ВНИИПИ Государственного i-омитета СССР

по делам изобре :ч ь пи и открытий 113035, Москва, Ж--35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

Фиг. 3

| Журавлев Ю.П | |||

| и контроль ЭВМ | |||

| М | |||

| с | |||

| Двухколейная подвесная дорога | 1919 |

|

SU151A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Матричный сумматор-умножитель | 1978 |

|

SU767759A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| и др | |||

| Надежность Сов | |||

| радио, 1978, | |||

Авторы

Даты

1987-10-30—Публикация

1986-03-03—Подача