4 Ю

4

00

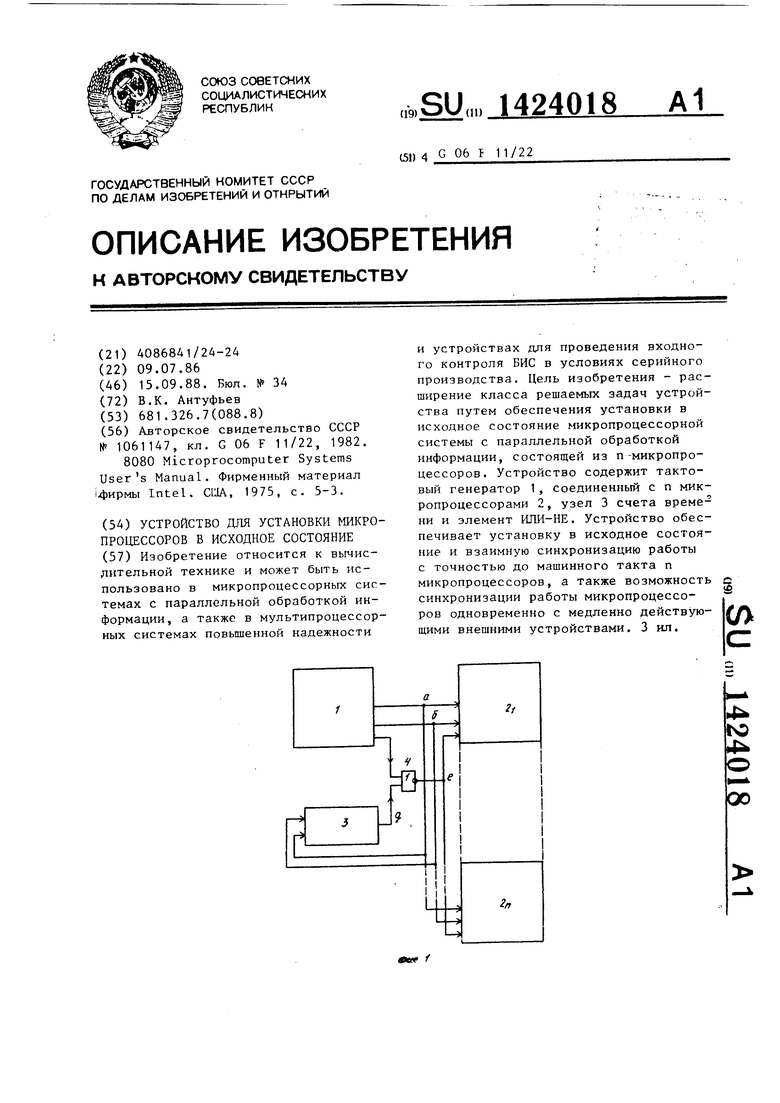

Изобретение относится к вычислительной технике и может быть использовано, например, в многопроцессорных системах с параллельной обработкой информации, построенных на базе микропроцессоров серии 580.

Цель изобретения - расширение класса решаемых задач путем обеспечения одновременной установки группы микропроцессоров.

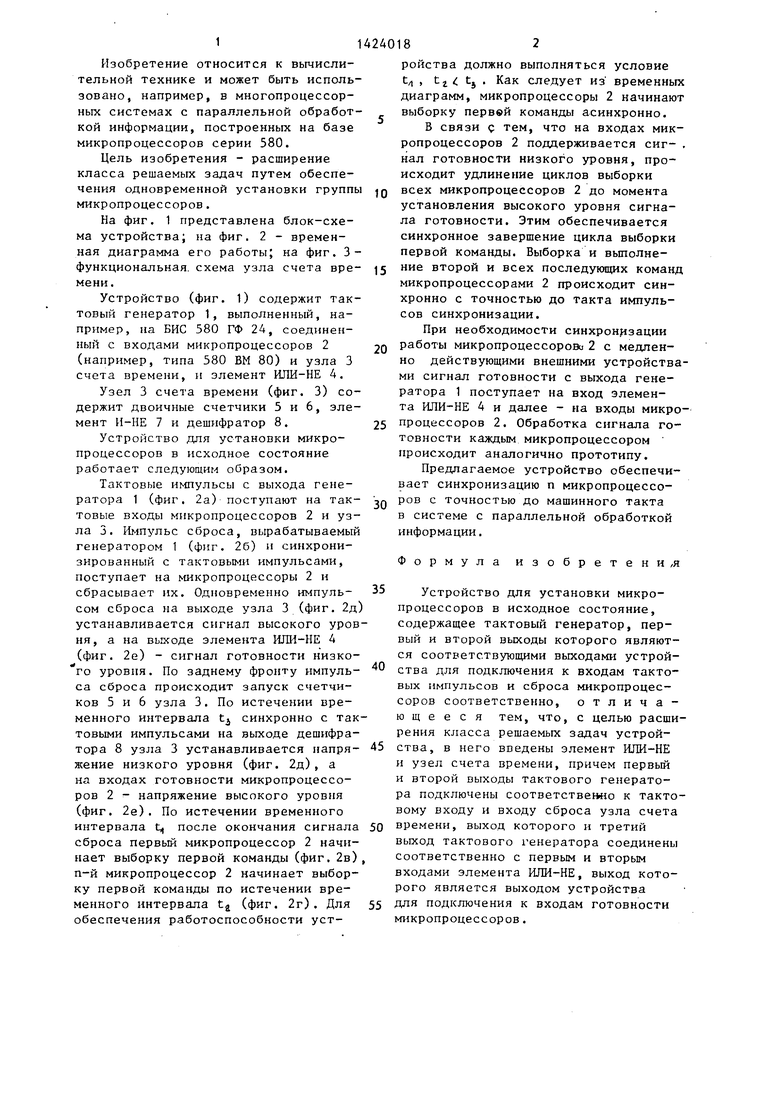

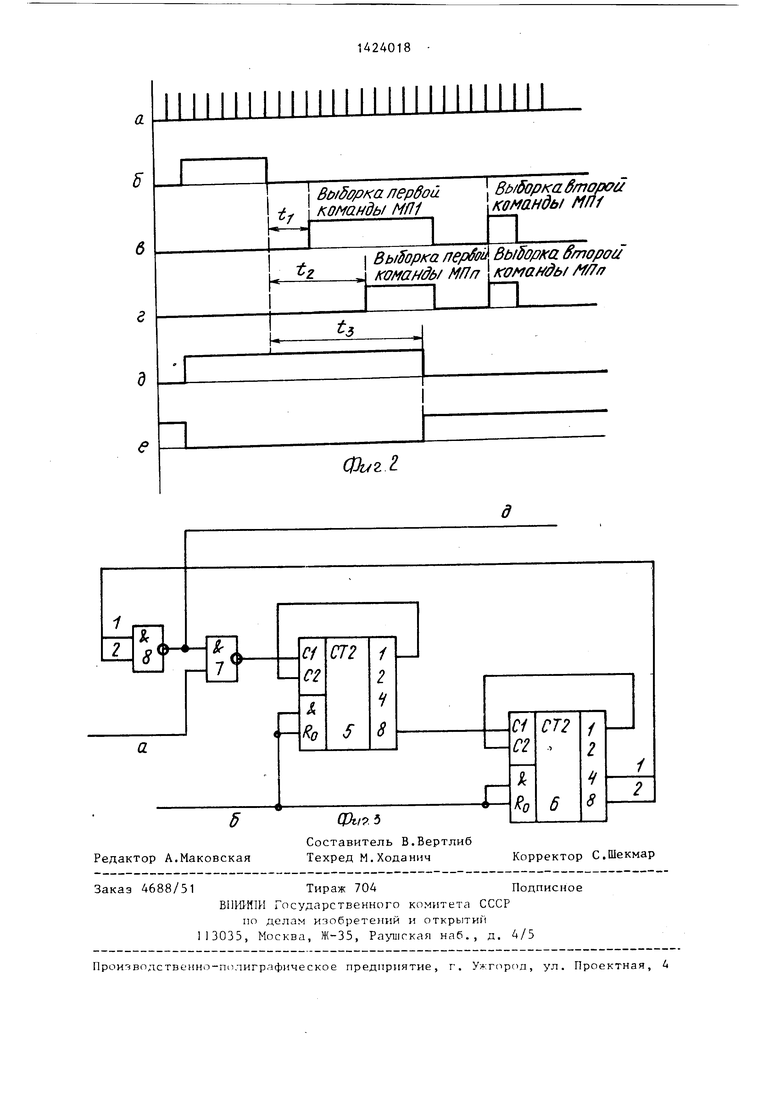

На фиг. 1 представлена блок-схема устройства; на фиг. 2 - временная диаграмма его работы; на фиг. 3- функциональная. схема узла счета времени.

Устройство (фиг. 1) содержит тактовый генератор 1, выполненный, например, на БИС 580 ГФ 24, соединенный с входами микропроцессоров 2 (например, типа 580 ВМ 80) и узла 3 счета времени, и элемент ИЛИ-НЕ 4.

Узел 3 счета времени (фиг. 3) содержит двоичные счетчики 5 и 6, элемент Н-НЕ 7 и дешифратор 8.

Устройство для установки микропроцессоров в исходное состояние работает следующим образом.

Тактовые импульсы с выхода генератора 1 (фиг. 2а) поступают на тактовые входы микропроцессоров 2 и узла 3. Импульс сброса, вырабатываемый генератором 1 (фиг. 26) и синхронизированный с тактовыми импульсами, поступает на микропроцессоры 2 и сбрасывает их. Одновременно импульсом сброса на выходе узла 3 (фиг. 2д устанавливается сигнал высокого уровня, а на выходе элемента ИЛИ-НЕ 4 (фиг. 2е) - сигнал готовности низко- го уровня. По заднему фронту импульса сброса происходит запуск счетчиков 5 и 6 узла 3. По истечении временного интервала t синхронно с тактовыми импульсами на выходе дешифратора 8 узла 3 устанавливается иапря- жение низкого уровня (фиг. 2д), а на входах готовности микропроцессоров 2 - напряжение высокого уровня (фиг. 2е). По истечении временного интервала ц после окончания сигнала сброса первьш микропроцессор 2 начинает выборку первой команды (фиг. 2в) п-й микропроцессор 2 начинает выборку первой команды по истечении временного интервала tj (фиг. 2г). Для обеспечения работоспособности уст

0

5

0

5

5 0 5

0

5

0

роиства должно выполняться условие t/t tj . Как следует из временных диаграмм, микропроцессоры 2 начинают выборку перввй команды асинхронно.

В связи Q тем, что на входах микропроцессоров 2 поддерживается сиг- . нал готовности низкого уровня, происходит удлинение циклов выборки всех микропроцессоров 2 до момента установления высокого уровня сигнала готовности. Этим обеспечивается синхронное завершение цикла выборки первой команды. Выборка и выполнение второй и всех последующих команд микропроцессорами 2 происходит синхронно с точностью до такта импульсов синхронизации.

При необходимости синхрон 1зации работы микропроцессорово 2 с медленно действующими внешними устройствами сигнал готовности с выхода генератора 1 поступает на вход элемента ИЛИ-НЕ 4 и далее - на входы микропроцессоров 2. Обработка сигнала готовности каждым микропроцессором происходит аналогично прототипу.

Предлагаемое устройство обеспечивает синхронизацию п микропроцессоров с точностью до машинного такта в системе с параллельной обработкой информации.

Формула изобретени/я

Устройство для установки микропроцессоров в исходное состояние, содержащее тактовый генератор, первый и второй выходы которого являются соответствующими выходами устройства для подключения к входам тактовых импульсов и сброса микропроцессоров соответственно, отличающееся тем, что, с целью расширения класса решаемых задач устройства, в него введены элемент ИЛИ-НЕ и узел счета времени, причем первый и второй выходы тактового генератора подключены соответственно к тактовому входу и входу сброса узла счета времени, выход которого и третий выход тактового генератора соединены соответственно с первьм и вторым входами элемента ИЛИ-НЕ, выход которого является выходом устройства для подключения к входам готовности микропроцессоров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения с микропроцессором | 1983 |

|

SU1109730A1 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

| Устройство для сопряжения микропроцессора с М периферийными блоками | 1987 |

|

SU1434442A1 |

| Система для отладки программ | 1987 |

|

SU1481774A1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ МНОГОЛУЧЕВЫХ РАДИОСИГНАЛОВ | 1992 |

|

RU2042195C1 |

| Система для обмена информацией | 1985 |

|

SU1298760A1 |

| Устройство для сопряжения датчика информации с электронной вычислительной машиной | 1983 |

|

SU1133590A1 |

| Устройство для связи микропроцессора с внешними устройствами | 1986 |

|

SU1372330A1 |

| Система для программного управления технологическим оборудованием | 1989 |

|

SU1674062A1 |

| Устройство для управления памятью | 1983 |

|

SU1151975A1 |

Изобретение относится к вычислительной технике и может быть использовано в микропроцессорных системах с параллельной обработкой информации, а также в мультипроцессорных системах повышенной надежности и устройствах для проведения входного контроля БИС в условиях серийного производства. Цель изобретения - расширение класса решаемых задач устройства путем обеспечения установки в исходное состояние микропроцессорной системы с параллельной обработкой информации, состоящей из п-микропроцессоров. Устройство содержит тактовый генератор 1, соединенный с п микропроцессорами 2, узел 3 счета времени и элемент ИЛИ-НЕ. Устройство обеспечивает установку в исходное состояние и взаимную синхронизацию работы с точностью до машинного такта п микропроцессоров, а также возможность синхронизации работы микропроцессоров одновременно с медленно действующими внешними устройствами. 3 ил. (Л

| Устройство для включения и перезапуска микропроцессора при сбоях питания | 1982 |

|

SU1061147A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Ручная косилка | 1926 |

|

SU8080A1 |

| Паровоз для отопления неспекающейся каменноугольной мелочью | 1916 |

|

SU14A1 |

| США, 1975, с | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1988-09-15—Публикация

1986-07-09—Подача