Изобретение относится к автоматике и вычислительной технике и может быть использовано для связи между периферийными устройствами в микропроцессорной системе.

Цель изобретения - повышение быстродействия устройства и сокращение аппаратурных затрат.

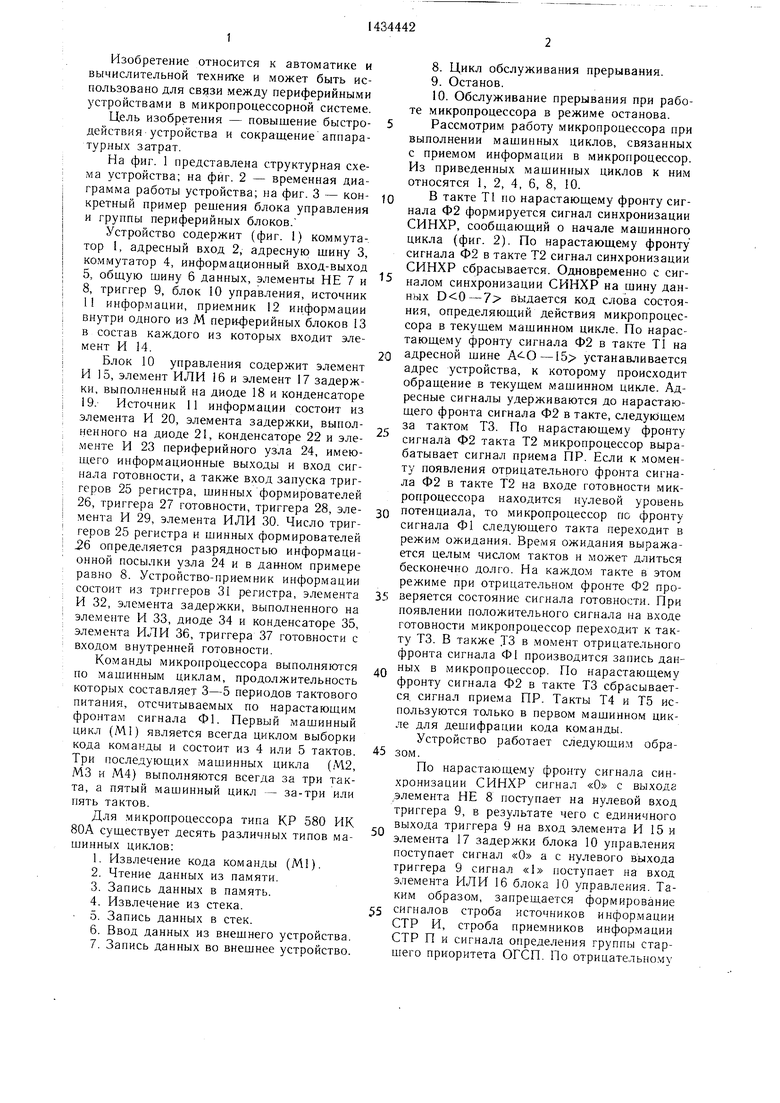

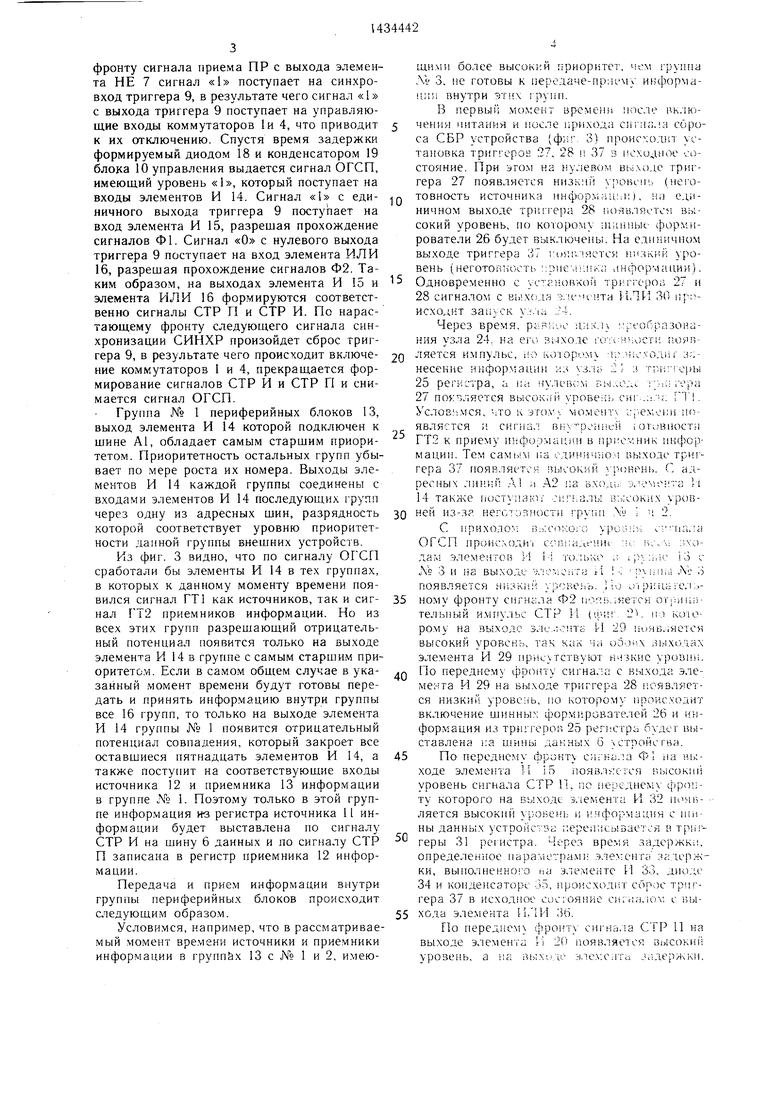

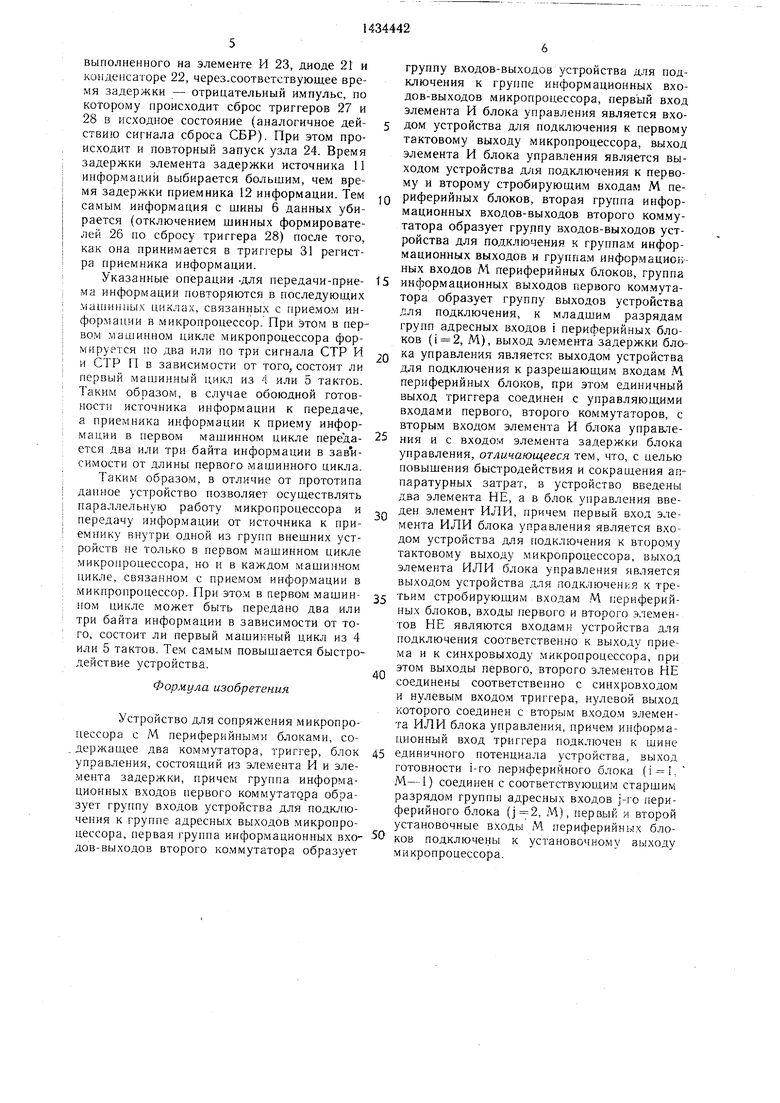

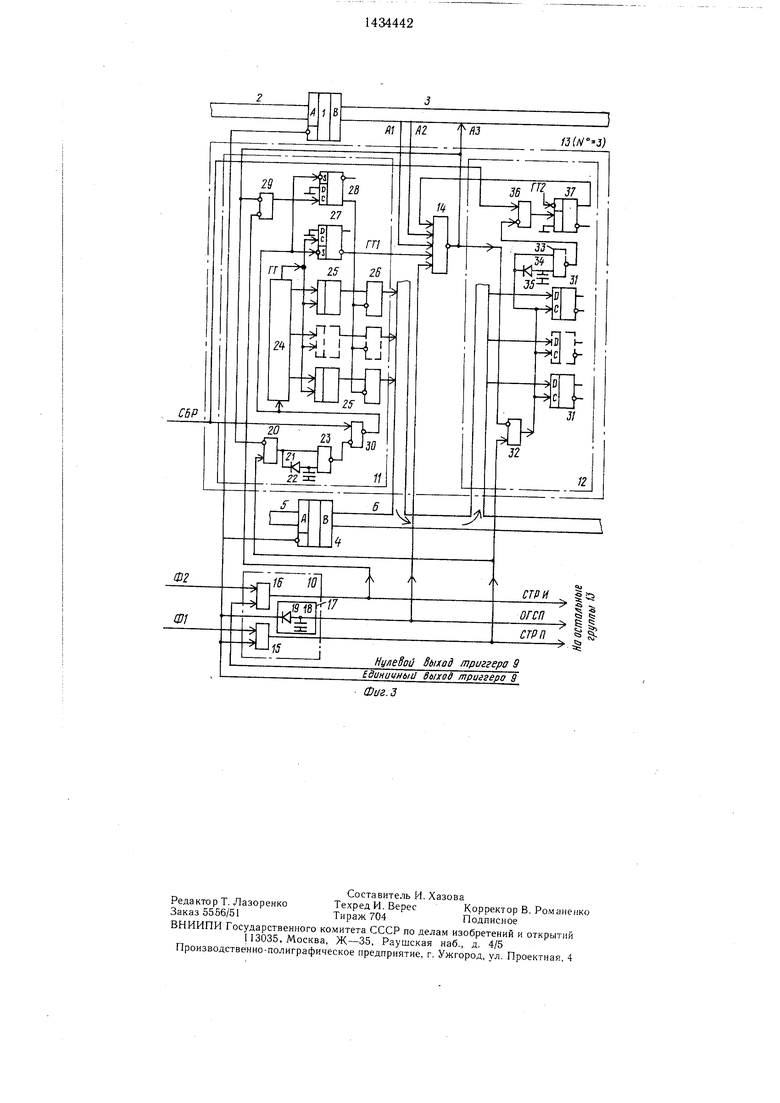

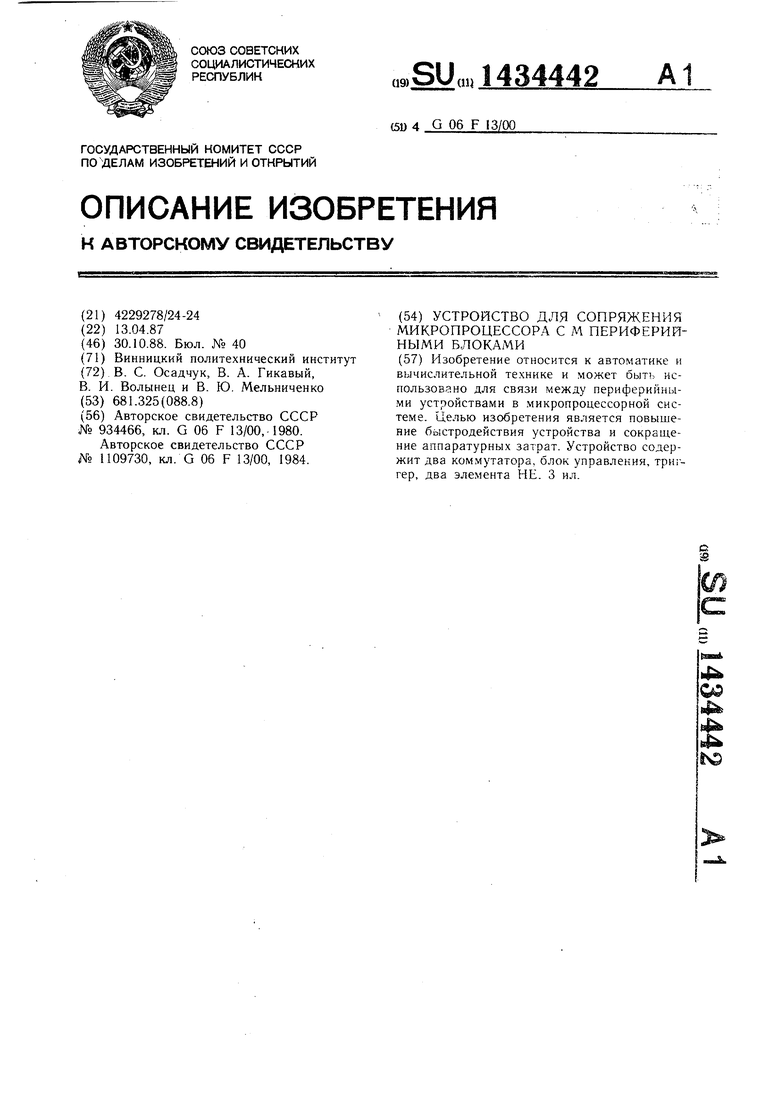

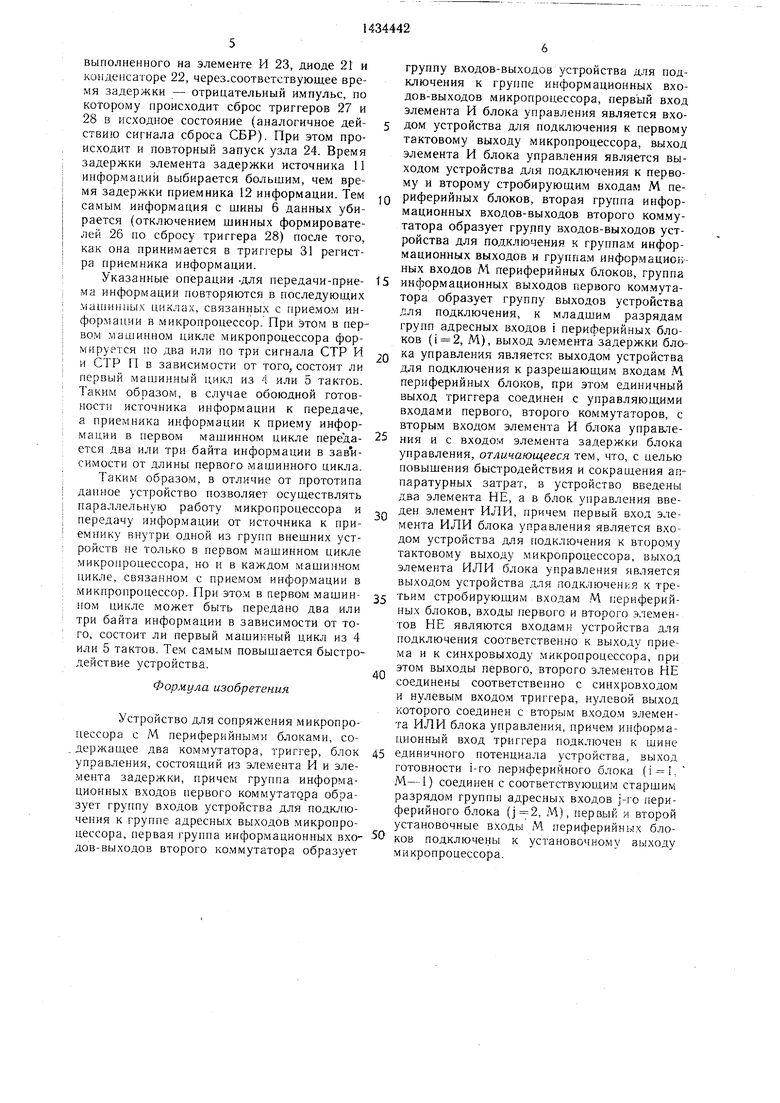

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - временная диаграмма работы устройства; па фиг. 3 - конкретный пример решения блока управления и группы периферийных блоков.

Устройство содержит (фиг. I) коммутатор I, адресный вход 2, адресную шину 3, коммутатор 4, информационный вход-выход 5, общую шину 6 данных, элементы НЕ 7 и 8, триггер 9, блок 10 управления, источник 1 инфор.мации, приемник 12 информации внутри одного из М периферийных блоков 13 в состав каждого из которых входит элемент И 14.

Блок 10 управления содержит элемент И 15, элемент ИЛИ 16 и элемент 17 задержки, выполненный на диоде 18 и конденсаторе 19. Источник 11 информации состоит из элемента И 20, элемента задержки, выполненного на диоде 21, конденсаторе 22 и элементе И 23 периферийного узла 24, имеющего информационные выходы и вход сигнала готовности, а также вход запуска триггеров 25 регистра, шинных формирователей 26, триггера 27 готовности, триггера 28, элемента И 29, элемента ИЛИ 30. Число триггеров 25 регистра и шинных формирователей 6 определяется разрядностью информационной посылки узла 24 и в данном примере равно 8. Устройство-приемник информации состоит из триггеров 31 регистра, элемента И 32, элемента задержки, выполненного на элементе И 33, диоде 34 и конденсаторе 35, элемента ИЛИ 36, триггера 37 готовности с входом внутренней готовности.

Команды микропроцессора выполняются по машинным циклам, продолжительность которых составляет 3-5 периодов тактового питания, отсчитываемых по нарастающим фронтам сигнала Ф1. Первый машинный цикл (Ml) является всегда циклом выборки кода команды и состоит из 4 или 5 тактов. Три последующих машинных цикла (М2, МЗ и М4) выполняются всегда за три такта, а пятый машинный цикл - за-три или пять тактов.

Для .микропроцессора типа КР 580 ИК 80А существует десять различных типов машинных циклов;

1.Извлечение кода команды (Ml).

2.Чтение данных из памяти.

3.Запись данных в память.

4.Извлечение из стека.

5.Запись данных в стек.

6.Ввод данных из внешнего устройства.

7.Запись данных во внешнее устройство.

5

8.Цикл обслуживания прерывания.

9.Останов.

10.Обслуживание прерывания при работе микропроцессора в режиме останова.

Рассмотрим работу микропроцессора при

выполнении машинных циклов, связанных с приемом информации в микропроцессор. Из приведенных машинных циклов к ним относятся 1, 2, 4, 6, 8, 10.

В такте Т1 по нарастающему фронту сигнала Ф2 формируется сигнал синхронизации СИНХР, сообщающий о начале машинного цикла (фиг. 2). По нарастающему фронту сигнала Ф2 в такте Т2 сигнал синхронизации СИНХР сбрасывается. Одновременно с сиг5 налом синхронизации СИНХР на шину данных выдается код слова состояния, определяющий действия микропроцессора в текущем машинном цикле. По нарастающему фронту сигнала Ф2 в такте Т1 на

0 адресной шине устанавливается адрес устройства, к которому происходит обращение в текущем машинном цикле. Адресные сигналы удерживаются до нарастающего фронта сигнала Ф2 в такте, следующем за тактом ТЗ. По нарастающему фронту сигнала Ф2 такта Т2 .микропроцессор вырабатывает сигнал приема ПР. Если к моменту появления отрицательного фронта сигнала Ф2 в такте Т2 на входе готовности микропроцессора находится нулевой уровень

0 потенциала, то микропроцессор по фронту сигнала Ф1 следующего такта переходит в режим ожидания. Время ожидания выражается целым числом тактов н может длиться бесконечно долго. На каждо.м такте в этом режиме при отрицательном фронте Ф2 про5 веряется состояние сигнала готовности. При появлении положительного сигнала на входе готовности микропроцессор переходит к такту ТЗ. В также ТЗ в .мо.мент отрицательного фронта сигнала Ф1 производится запись дан-

,Q ных в микропроцессор. По нарастающему фронту сигнала Ф2 в такте ТЗ сбрасывается, сигнал приема ПР. Такты Т4 и Т5 используются только в первом машинном цикле для дешифрации кода команды.

Устройство работает следующи.м обра5 зом.

По нарастающему фронту сигнала синхронизации СИНХР сигнал «О с выхода элемента НЕ 8 поступает на нулевой вход триггера 9, в результате чего с единичного выхода триггера 9 на вход элемента И 15 и элемента 17 задержки блока 10 управления поступает сигнал «О а с нулевого выхода триггера 9 сигнал «1 поступает на вход элемента ИЛИ 16 блока 10 управления. Таким образом, запрещается формирование

5 сигналов строба источников инфор.мации СТР И, строба прие.мников информации СТР П и сигнала определения группы старшего приоритета ОГСП. По отрицательному

0

фронту сигнала приема ПР с выхода элемента НЕ 7 сигнал «1 поступает на синхро- вход триггера 9, в результате чего сигнал «1 с выхода триггера 9 поступает на управляющие входы коммутаторов 1и 4, что приводит к их отключению. Спустя время задержки формируемый диодом 18 и конденсатором 19 блока 10 управления выдается сигнал ОГСП, имеющий уровень «1, который поступает на входы элементов И 14. Сигнал «1 с единичного выхода триггера 9 поступает на вход элемента И 15, разрешая прохождение сигналов Ф1. Сигнал «О с нулевого выхода триггера 9 поступает на вход элемента ИЛИ 16, разрешая прохождение сигналов Ф2. Таким образом, на выходах элемента И 15 и элемента ИЛИ 16 формируются соответственно сигналы СТР П и СТР И. По нарастающему фронту следующего сигнала синхронизации СИНХР произойдет сброс триггера 9, в результате чего происходит включение коммутаторов 1 и 4, прекращается формирование сигналов СТР И и СТР П и снимается сигнал ОГСП.

Группа № 1 периферийных блоков 13, выход элемента И 14 которой подключен к шине А1, обладает самым старшим приоритетом. Приоритетность остальных групп убывает по мере роста их номера. Выходы элементов И 14 каждой группы соединены с входами эле.ментов И 14 последующих групп через одну из адресных шин, разрядность которой соответствует уровню приоритетности дайной группы внешних устройств.

Из фиг. 3 видно, что по сигналу ОГСП сработали бы элементы И 14 в тех группах, в которых к данному моменту времени появился сигнал ГТ1 как источников, так и сигнал ГТ2 приемников информации. Но из всех этих групп разрешаюший отрицательный потенциал появится только на выходе эле.мента И 14 в группе с самым старшим при- оритето.м. Если в самом общем случае в указанный момент времени будут готовы передать и принять инфор.мацию внутри группы все 16 групп, то только на выходе элемента И 14 группы № 1 появится отрицательный потенциал совпадения, который закроет все оставшиеся пятнадцать эле.ментов И 14, а также постугшт на соответствующие входы источника 12 и приемника 13 информации в группе № 1. Поэтому только в этой группе информация ив регистра источника 11 информации будет выставлена по сигналу СТР И на шину 6 данных и по сигналу СТР П записана в регистр приемника 12 информации.

Передача и прием инфор.мации внутри группы периферийных блоков происходит следующим образом.

Условимся, например, что в рассматриваемый момент вре.мени источники и приемники информации в групп&х 13 с jY9 1 и 2, имеющими более высокий Г1риоритет, ie группа Ль 3. не готовы к передаче-ормемх ньч.х) JUi:-; внутри этих ipyini.

В первый момент врсмен.м :i;ic.ie . IHJчения п.итания и после ири.чода c ii :i.ia соро- са СВР устройства {ф;;г- 3) происходг.т установка триггеров 27, 28 и 37 з исходное состояние. 11ри этом на нулевом выходе триггера 27 появляется низкий у;) (Hei oтовность источника инфор.мац:; :), ма e.ui- ничном выходе трг. тера 28 ноянлястсн высокий уровень, по которому пшапыс формирователи 26 будет выключены. На ели ичном выходе триггера 37 ГОЯР-ПЯСТСИ ии.чкяй уровень (неготовность :;зпемк1 ка анформацин.

Одновременно с vc aiiORKt) триггеров 27 и 28 сигналом с вы.хемя ч.н чс лта ИЛИ 30 исходит запуск y:;.-ia .

Через время, paRн..c цил.1 ;;реобразона- ння уз.ла 24. на его выходе гоч-снкйсп; нояг;ляетея импульс, но которому U.MicNoaiir занесение ннфор ;ацин из з. 1а 2 .- з тр|;ггс)ь: 25 регистра, а на iiy.icBOM . туи; гсра 27 по5-: ляется высокл vnosei-ib cni-..ал;; I Tl.

Услов:-:мся, -iTO к это. момеят ;;.ev.ci;ii пп5

является

сигнал BHV pciUicH ;о1 жноста

ГТ2 к приему Н11форма11ин в npi OMHUK информации. Тем па единичном выходе трш - гера 37 появляется высокий -р(нень. С адресных линий А и А2 :а BX(r,u;: э.ч мента li 14 также )ст иак1: сигкалы высоких уров0 ней из-з. негсл ;),1оети rpysHi у i ; 2.

С приходе-; ;в;5;соко; 0 уроан;; cv- Ha.ia ОГСП происходи C iii;a:ifunc ас iic..: дая элементов 1-1 М только а i р аас 3 с Ль 3 и на выходе .:c%iC iTa И - мпшил Ле ii появляется низк1 Й ровеьг). По oipiniai e. ному фронту сигнала Ф2 .;«eTCH orpiiiia- тельный и.мнульс СТР 11 (tpar . по ко ю- рому на выходе злс.. 1-1 29 инв..яется высокий уровень, так как ча выходах элемента И 29 npvicvTCTBVtOT HHJKSI.C ypoBHCi.

Q По переднему фронту сигнала с выхода элемента И 29 на выходе триггера 28 оявляет- ся низкий уровеаъ, по которому происходит включение шинных формифователей 26 и информация из триггеров 25 регистра бч дег выставлена i;a шины данных 6 стройсгва.

5 По переднему фронту сигна.а Ф1 на иь;- ходе эле.мента И 15 появл :ется пысокнй уровень сигнала СТР П, по нере;и1ем фро;;-- ту которого на э.емента И 32 HOHII- - ляетея высокий уровень и нформация с Н1и- ны данных устройстза ;;ере;1;;сь зается в Tpin геры 31 pci истра. Через время задержки, определенное параметрами 3.ie :eirra зачерж- ки, выполненно о на элементе И 33, диоде 34 и конденсаторе 35, нроисход1 Т сор-ос триггера 37 в исходное состояние ciirt a. с ны5 хода элемента П, 1И 36.

По переднему фронту сигна.ча СТР П на выходе элемента li 20 Г1оявляетея зыеокиГ- уровень, а на пыхочо эле :е;гга задержки.

выполненного на элементе И 23, диоде 21 и конденсаторе 22, через.соответствующее время задержки - отрицательный импульс, по которому происходит сброс триггеров 27 и 28 в исходное состояние (аналогичное действию сигнала сброса СВР). При этом происходит и повторный запуск узла 24. Время задержки элемента задержки источника 1 информации выбирается большим, чем время задержки приемника 12 информации. Тем самым информация с шины 6 данных убирается (отключением шинных формирователей 26 по сбросу триггера 28) после того, как она принимается в триггеры 31 регистра приемника информации.

Указанные операции -для передачи-приема информации повторяются в последуюадих машинных циклах, связанных с приемом информации в микропроцессор. При этом в первом машинном цикле микропроцессора формируется по два или по три сигнала СТР И и СТР П в зависимости от того, состоит ли первый машинный цикл из 4 или 5 тактов. Таким образом, в случае обоюдной готовности источника информации к передаче, а приемника информации к приему информации в первом машинном цикле передается два или три байта информации в зав и- симости от длины первого машинного цикла.

Таким образом, в отличие от прототипа данное устройство позволяет осуществлять параллельную работу микропроцессора и передачу информации от источника к приемнику внутри одной из групп внешних устройств не только в первом машинном цикле микропроцессора, но и в каждом машинном цикле, связанном с приемом информации в микпропроцессор. При этом в первом машин- iioM цикле может быть передано два или три байта информации в зависимости от того, состоит ли первый машинный цикл из 4 или 5 тактов. Тем самым повышается быстродействие устройства.

Формула изобретения

Устройство для сопряжения микропроцессора с М периферийными блоками, со- , держашее два коммутатора, триггер, блок управления, состоящий из элемента И и элемента задержки, причем группа информационных входов первого коммутатора образует группу входов устройства для подключения к группе адресных выходов микропро цессора, первая группа информационных вхо дов-выходов второго коммутатора образует

со

группу входов-выходов устройства для подключения к группе информационных входов-выходов микропроцессора, первый вход элемента И блока управления является вхо5 дом устройства д/1я подключения к первому тактовому выходу микропроцессора, выход элемента И блока управления является выходом устройства для подключения к первому и второму стробирующи.м входам М риферийных блоков, вторая группа информационных входов-выходов второго коммутатора образует группу входов-выходов устройства для подключения к группам информационных выходов и группам информационных входов М периферийных блоков, группа

15 информационных выходов первого ком.мута- тора образует группу выходов устройства для подключения, к младши.м разрядам групп адресных в.ходов i периферийных блоков (1 2, М), выход элемента задержки бло

Q ка управления является выходом устройства для подключения к разрешающим входам М периферийных блоков, при этом единичный выход триггера соединен с управляющи.ми входами первого, второго коммутаторов, с вторым входом элемента И блока упрааде25 НИН и с входом элемента задержки блока управления, отличающееся тем, что, с целью повышения быстродействия и сокращения аппаратурных затрат, в устройство введены два элемента НЕ, а в блок управления вве,,, ден элемент ИЛИ, причем первый вход элемента ИЛИ блока управления является входом устройства для подключения к второму тактовому выходу .микропроцессора, выход элемента ИЛИ блока управления является выходом устройства для подключенкя к тре35 тьим стробирующим входам .М периферийных блоков, входы первого и второго элементов НЕ являются входами устройства для подключения соответственно к выходу приема и к синхровыходу .микропроцессора, при этом выходы первого, второго элементов НЕ соединены соответственно с синхровходом и нулевым входо.м триггера, нулевой выход которого соединен с вторым входом элемента ИЛИ блока управления, причем информационный вход триггера подключен к шине

45 единичного потенциала устройства, выход готовности i-ro периферийного блока (i l, М-1) соединен с соответствующи.м старшим разрядом группы адресных входов j -ro периферийного блока (, М), первый и второй установочные входы М периферийных бло40

50

ков подключены к установоч.чому выходу .микропроцессора.

dJus.Z

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения с микропроцессором | 1983 |

|

SU1109730A1 |

| Устройство для сопряжения микропроцессора с периферийными устройствами | 1987 |

|

SU1434440A1 |

| Устройство микропроцессорной связи | 1983 |

|

SU1124275A1 |

| Устройство для связи микропроцессора с внешними устройствами | 1986 |

|

SU1372330A1 |

| Устройство микропроцессорной связи | 1978 |

|

SU734657A1 |

| Устройство микропроцессорной связи | 1986 |

|

SU1361568A2 |

| Процессор для мультипроцессорной системы | 1987 |

|

SU1517035A1 |

| Устройство для управления памятью | 1983 |

|

SU1151975A1 |

| Устройство для объема информацией между ЭВМ и периферийными устройствами | 1989 |

|

SU1679497A1 |

| Устройство для проверки выполнения последовательности команд микропроцессора | 1984 |

|

SU1247874A1 |

Изобретение относится к автоматике и вычислительной технике и мо.жет быть использовано для связи между периферийными устройствами в .микропроцессорной системе. Целью изобретения является повышение быстродействия устройства и сокращение аппаратурных затрат. Устройство содержит два коммутатора, блок управления, триггер, два элемента НЕ. 3 ил.

| Устройство микропроцессорной связи | 1981 |

|

SU934466A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения с микропроцессором | 1983 |

|

SU1109730A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-10-30—Публикация

1987-04-13—Подача