11

4

N

С СП

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах различиого назначения.

Целью изобретения является сокращение аппаратурных затрат.

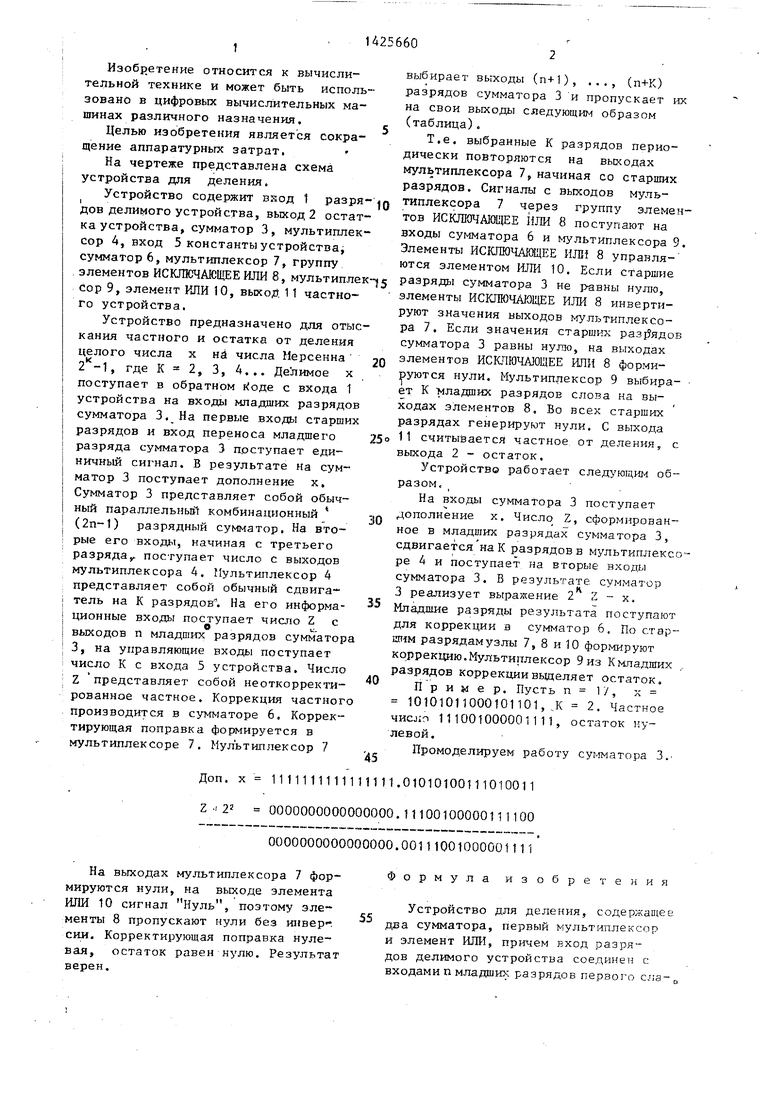

На чертеже представлена схема устройства для деления.

Устройство содержит вкод 1 разря дов делимого устройства, выход 2 остатка устройства, сумматор 3, мультиплексор 4, вход 5 константы устройства сумма тор 6, мультиплексор 7, группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 8, мультипле сор 9, элемент ИЛИ 10, выхоД 1 1 частного устройства.

Устройство предназначено для отыскания частного и остатка от деления целого числа х ни числа Мерсенна 2 -1, где К 2, 3, 4... Делимое х поступает в обратном с входа 1 устройства на входы младших разрядов сумматора 3. На первые входы старших разрядов и вход переноса младшего разряда сумматора 3 поступает единичный сигнал. В результате на сумматор 3 поступает дополнение х. Сумматор 3 представляет собой обычный параллельный комбинационный (2п-1) разрядный сумматор. На вторые его входы, начиная с третьего разряда поступает число с выходов мультиплексора 4. Мультиплексор 4 представляет собой обычный сдвига- тель на К разрядов. На его информа- ционные входы поступает число Z с выходов п младших разрядов сумматора 3, на управляющие входы поступает число К с входа 5 устройства. Число Z представляет собой неоткорректи- рованное частное. Коррекция частного производится в сумматоре 6, Корректирующая поправка формируется в

мультиплексоре 7. Мультиплексор 7

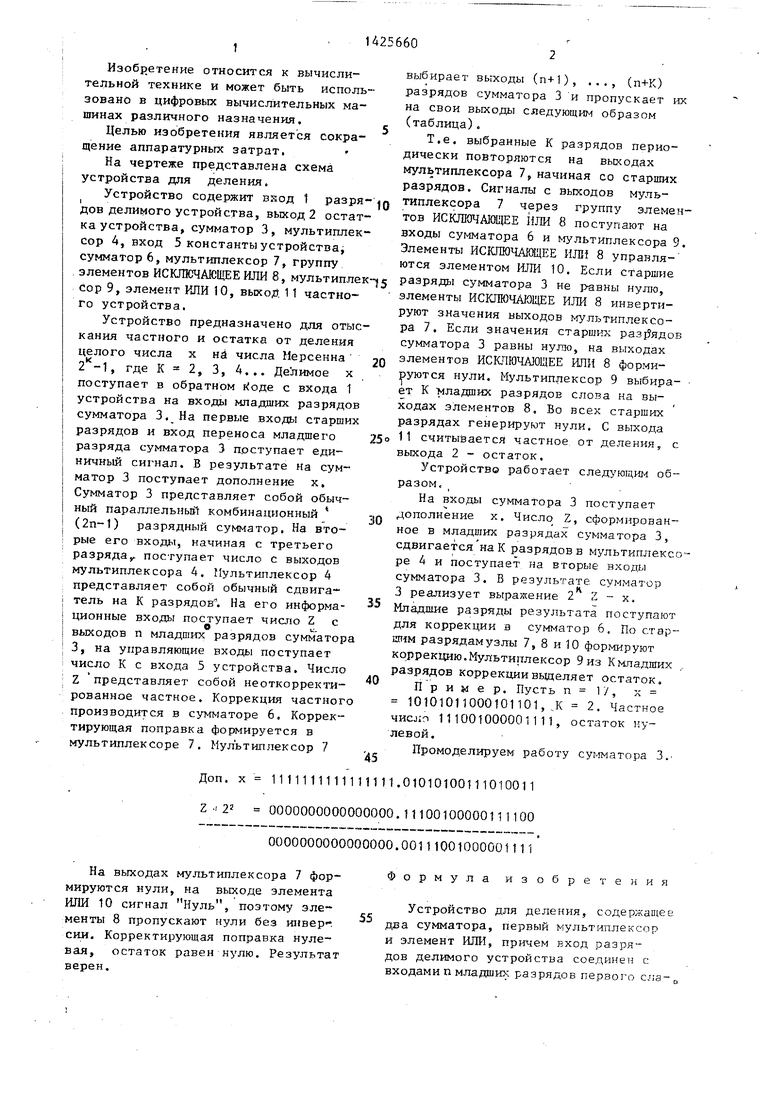

выбирает выходы (n-t-l), ..., (п+К) разрядов сумматора 3 и пропускает их на свои выходы следующим образом (таблица).

Т.е. выбранные К разрядов периодически повторяются на выходах мультиплексора 7, начиная со старших разрядов. Сигналы с выходов мультиплексора 7 через группу элементов ИСКЛЮЧАЩЕЕ 1{ЛИ 8 поступают на входы сумматора 6 и мультиплексора 9 Элементы ИСКЛЮЧАМЦЕЕ ИЛИ 8 управля- ются элементом ИЛИ 10. Если старшие разряды сумматора 3 не равны нулю, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 8 инвертируют значения выходов мультиплексора 7. Если значения старших сумматора 3 равны нулю, на выходах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 8 формируются нули. Мультиплексор 9 выбира- ет К младших разрядов слова на выходах элементов 8. Во всех старших разрядах генерируют нули. С выхода 11 считывается частное, от деления, с выхода 2 - остаток.

Устройство работает следующим образом,

На входы сумматора 3 поступает дополнение х. Число Z, сформированное в младших разрядах сумматора 3, сдвигается на К разрядов в мультиплексре 4 и поступает на вторые входы сумматора 3. В результате сумматор 3 реализует выражение 2 Z - х. Младшие разряды результата поступают для коррекции в сумматор 6. По стар OTiM разрядам узлы 7, 8 и 10 формируют коррек1щю.Мультиплексор 9 из Кмладших разрядов коррекции выделяет остаток.

Пример. Пусть п Г/, х 10101011000101101, Д 2, Частное число 111001000001111, остаток кулевой.

Промоделируем работу суг матора З.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления последовательных чисел | 1987 |

|

SU1462298A1 |

| Устройство для деления чисел с фиксированной запятой | 1986 |

|

SU1417009A1 |

| Устройство для деления | 1989 |

|

SU1619256A1 |

| Устройство для деления чисел на константу 2 @ + 1 | 1990 |

|

SU1730624A1 |

| Устройство для деления | 1988 |

|

SU1517026A1 |

| Устройство для деления | 1990 |

|

SU1783522A1 |

| Устройство для умножения | 1986 |

|

SU1432506A1 |

| Устройство для деления | 1986 |

|

SU1361545A1 |

| Ячейка однородной структуры | 1990 |

|

SU1805461A1 |

| Устройство для деления | 1978 |

|

SU802962A1 |

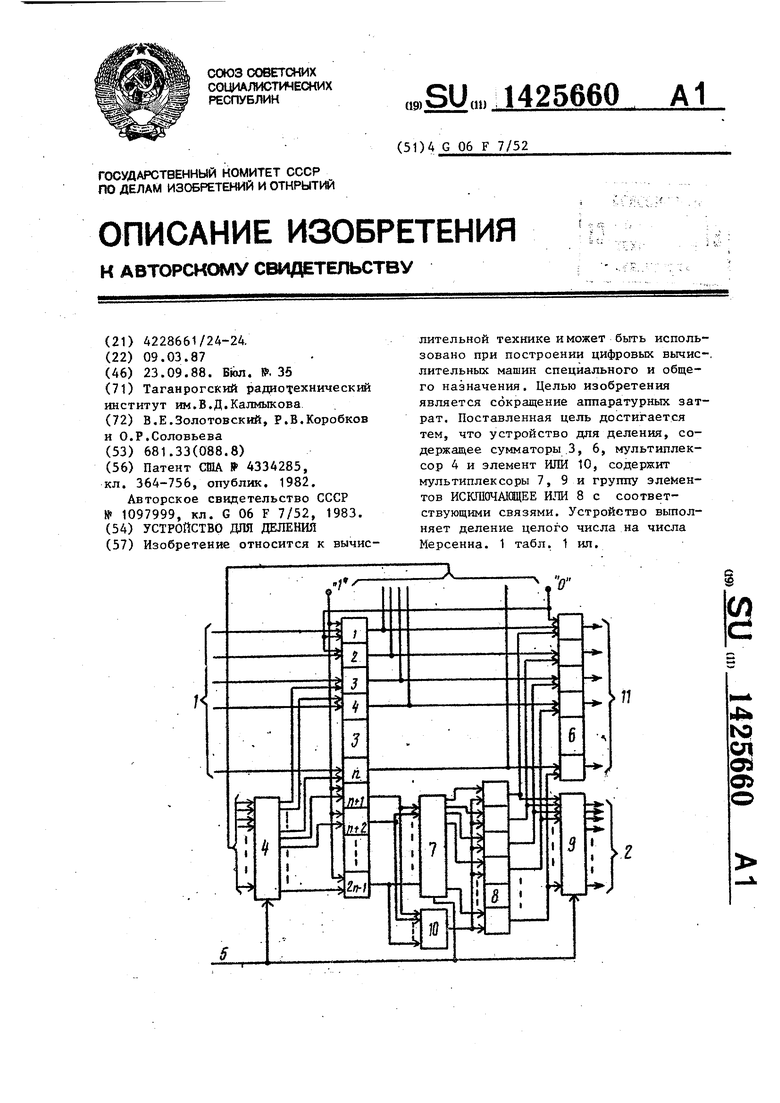

Изобретение относится к вычислительной технике и может быть использовано при построении цифровых вычислительных машин специального и общего назначения. Целью изобретения является сокращение аппаратурных затрат. Поставленная цель достигается тем, что устройство для деления, содержащее сумматоры.3, 6, мультиплексор 4 и элемент ИЛИ 10, содержит мультиплексоры 7, 9 и группу элементов ИСКШОЧАЩЕЕ ИЛИ 8 с соответствующими связями. Устройство вьтол- няет деление целого числа на числа Мерсенна. 1 табл. 1 ил.

Доп. х 1111111111111111.01010100111010011 Z 22 0000000000000000.11100100000111100

0000000000000000.00111001000001111

На выходах мультиплексора 7 формируются нули, на выходе элемента ИЛИ 10 сигнал Нуль, поэтому элементы 8 пропускают нули без ипвер-. сии. Корректирующая поправка нулевая, остаток равен нулю. Результат верен.

Формула изобретения

Устройство для деления, содержащее сумматора, первый мультиплексор и элемент ИЛИ, причем вход разрядов делимого устройства соединен с входами п младших разрядов первого снагаемого первого сумматора, вход переноса и входь (n-l)-ro старшего разряда первого слагаемого которого соединены с входом единичного потенциала устройства, вход константы которо- го соединен с управляющим входом первого мультиплексора, выходы (n-l)-ro старшего разряда первого сумматора соединены соответственно с входами элемента ИЛИ (п-разрядность делимого), отличающееся тем, что, с целью сокращения аппаратурных затрат, оно содержит второй и третий мультиплексоры, группу элементов ИСКЛЮЧАКЛЦЕЕ 11ПИ, причем выходы п младших разрядов первог о сумматора соединены с входами соответствующих

15 вторые входы которых объединены и соединены с выходом элемента ИЛИ, выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы соединены с соответствующими информационными входами третьего

разрядов первого слагаемого второго

сумматора и с соответствующими инфор- 2о .мультиплексора и входами разрядов

мационными входами первого мульти- второго слагаемого сумматора, выход

плексора, выходы разрядов которого соединены соответственно с входами разрядов с третьего по (2п-1)-й: второго слагаемого первого сумматора, входы

первого и второго разрядов второго слагаемого которого и вход переноса второго сумматора соединены с входом нулевого потенциала устройства, вход константы которого соединен с управляющими входами второго и третье.го мультиплексоров, выходы (п-1)-го старшего разряда первого сумматора

соединены соответственно с информационными входами второго мультиплексора, входы разрядов которого сое/ди- нены с первыми входами соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИШ1 группы,

вторые входы которых объединены и соединены с выходом элемента ИЛИ, выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы соединены с соответствующими информационными входами третьего

которого является выходом частного устройства, выход третьего мультиплексора является выходом остатка 25 устройства.

| Патент США 4334285, кл | |||

| Способ получения мыла | 1920 |

|

SU364A1 |

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

| Авторское свидетельство СССР № 1097999, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-09-23—Публикация

1987-03-09—Подача