8S8S

4:аь Ю СП

Oi 00

Изобретение относится к вычислительной технике и может,быть использовано для отладки программных и аппаратных средств и тестирования микропроцессорных систем (МПС).

Целью изобретения является расширение функциональных возможностей устройства за счет отладки программ в реальных условиях.

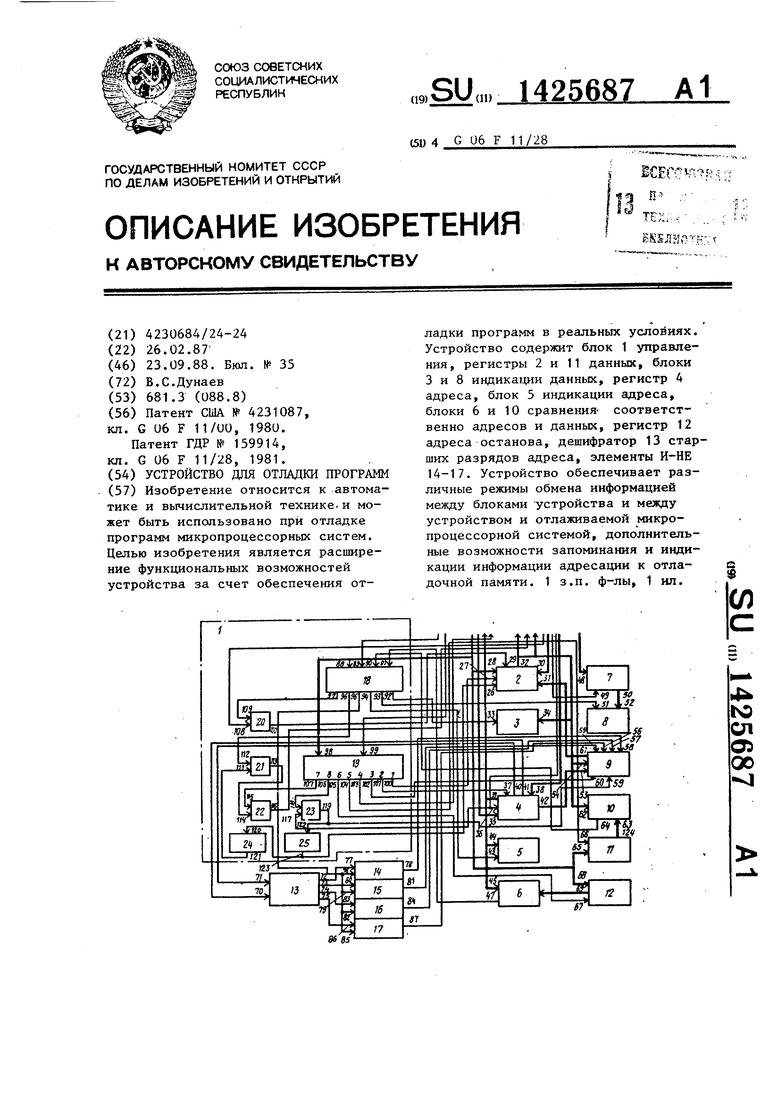

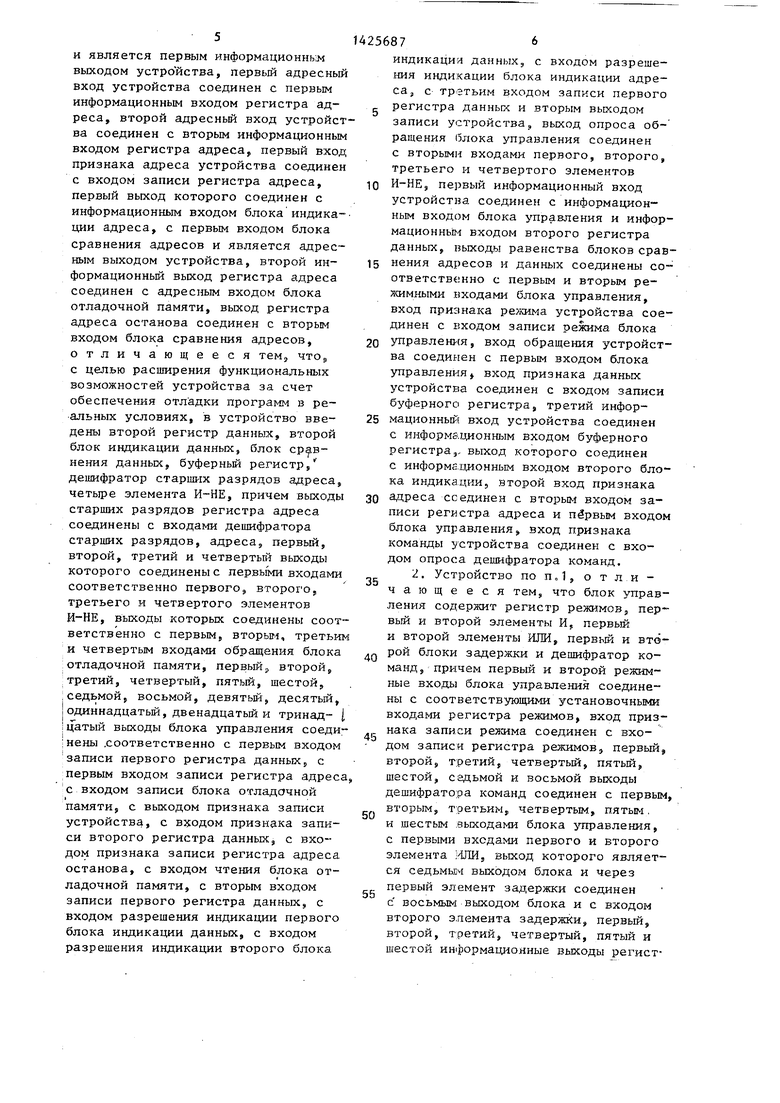

На чертеже изображена структурная схема устройства для отладки программ. Схема .содержит блок 1 управления, первый регистр 2 данных, первый блок 3 индикации данных, регистр 4 адреса, блок 5 индикации адреса, блок 6 сравнения адресов, регистр 7 данных, второй блок 8 индикации данных, блок 9 отладочной па.мяти, блок

10сравнения данных, второй регистр

11данных, регистр 12 адреса остано ва, дешифратор 13 ста1)й1их разрядов адреса, элементы И-НЕ lA-l, регистр 18 режимов, дешифратор 19 команд блока управления, элементы И 20 и 21, элементы ИЛИ 22 и 23, блоки 24

и 25 задержки.

Кроме того, на чертеже показаны входы-выходы 26-124.

Устройство работает следуюЕр1м образом.

: При записи информации в блок 9 отладочной памяти в регистр 2 данных и регистр 4 адреса предваритель- I но заносятся данные и адрес, причем : на первый вход данных регистра. 2 Сданных от устройства ввода поступают Сданные по сигналу, приходящему на вход записи регистра 2 данных, а I на первый адресньш вход регистра 4 адреса поступает адрес от устройства ввода по сигналу на вход записи регистра 4 адреса с выхода дешифратора 19 команд. Управляюи(ие сигналы вырабатываются блоком 1 управления при поступлении от устройства ввода информации на вход, данных и признак команды на входах дешифратора 19 команд. С выходовфегистра 2 данных на информационный вход блока 9 отладочной памяти поступает код и записывается по сигналу, поступающему на вход записи блока 9 отладочной памяти, по адресу, поступившему на адресный -вход блока 9 с выхода регистра 4 адреса. Обращение с целью записи или чтения производится к 8- разрядной ячейке блока 9, если на входы элементов И-НЕ соответственно

0

5

0

5

0

5

0

5

0

5

14-17 поступает сигнал уровня логической единицы. В случае при поступлении с одного из выходов дешифратора 13 старших разрядов сигнала уровня логической нуля на вход одного из элементов И-НЕ 14, 15, 16 и 17, на выходе соответствующего элемента появится сигнал логической единицы. Обращение производится к 24-разрядной ячейке памяти. Если на входы элементов И-НЕ 14-17 поступают нулевые потенциалы, при чтении из блока 9 по команде, поступающей от устройства ввода, запись адреса в регистр 4 адреса производится таким же образом, как и при записи в блок 9 отладочной памяти. Считьшание из блока 9 отладочной памяти производится по сигналу, поступившему на вход чтения с выхода элемента ИЛИ 23. Сигнал на выходе элемента ИЛИ 23 появляется при поступлении сигнала на его вход с выхода дешифратора 19 команд..

Информация с выхода блока 9 отладочной памяти поступает на информационный вход регистра 2 данных и : заносится в него по сигналу, поступившему на его вход записи- с выхода блока 2 задержки. Блок 2 задержки служит для задержки на время чтения из блока 9 отладочной памяти, поэтому сигнал записи в регистр 2 данных поступает на его вход записи после того, как данные в блоке 9 отладочной памяти появляются на выходе. Информация с выхода регистра- 2 данных поступает для индикации на вход данных блока 3 индикации данньк Сигнал, поступающий на управляющий вход этого блока индикации, запрещает или разрешает индикацию в зависимости от его уровня. При каждом обмене информацией между блоками устройства для отладки программ с отлаживаемой микропроцессорной системы юте с устройством ввода-вывода в регистр 18 режимов предварительно загружается код, который интерпретируется блоком 1 управления и определяет направление и режим обмена. Код поступает на информационный вход регистра 18 ре- iMOB от устройства ввода-вьгоода по сигналу, поступающему на вход записи регистра режимов 18 от устройства ввода-вывода. -Данные из блока 9 отладочной памяти могут быть переданы через регистр L данных к устройству ввода-вывода и от него, например в ЭВМ с целью их анализа и контроля Адрес с выхода регистра 4 адреса также может быть передан через устройство ввода-вывода во внешнюю среду. Кроме того, адрес может индицироваться в блоке ,5 индикации.

Возможны различные режимы отладки. В режиме непрерывного выполнения программы МПС по сигналу, поступающему от МПС на вход записи регистра 4 адреса 5 на его информационный вход поступает адрес, а с его выхода поступает на адресньй вход блока 9 отладочной памяти. Управляю- ощй сигнал от МПС поступает на вход элемента ИЛИ 23, с выхода которого сигнал чтения поступает на вход блока 9 отладочной памяти. После задержки на время чтения, осуществляемой блоком 25 задержки, данные по сигналу, поступающему с выхода блока 25 задержки, заносятся в регистр 2 данных. Блок 24 задержки осуществляет временную задержку выдачи сигнала готовности данных на время записи данных в регистр 2 данных. С выхода регистра 2 данных данные передаются к МПС по управляющему сигналу , поступающему к МПС с выхода элемента ИЛИ 22. Если эти данные являются командой, то она вьшолняется процессором МПС. Управляющий сигнал с выхода элемента ИЛИ 22 вьфабаты- вается с учетом состояния регистра 18 режимов. При положительном уровне сигнала, поступающего на вход элемента И 21, на второй вход этого элемента поступает также сигнал положительного уровня с выхода блока 24 задержки. При этом с выхода элемента И 21 поступает сигнал на вход элемента ИЛИ 22, В шаговом режиме отладки на вход элемента И 21 с выхода регистра 18 режимов поступает сигнал низкого уровня, который запрещает прохождение сигнала с выхода элемента И 21 на вход элемента ИЛИ 2 Управляющий сигнал на выходе элемента ИЛИ 22 формируется при поступле- 1ии сигнала с выхода дешифратора 19 команд на вход элемента.ИЛИ 22. Сигнал на выходе дешифратора 19 команд формируется при поступлении на его вход соответствующего кода от устройства ввода-вывода по сигналу, поступающему на вход признака коман

5

0

5

0

5

ды дешифратора 19 команд от устройства ввода-вывода. Таким образом, управление шаговым режимом -отладки осуществляется оператором с помощью устройства ввода информации.

При непрерывном выполнении программы МПС устройством анализируются адреса выполняемых команд и информации, являющаяся командой или операндом, или содержимым регистра состояния. Эта информация сравнивается в блоках 6 и 10 соответственно с содержимым регистра 12 адреса останова и регистра 1 1 данньгх. При совпадении с выходов блоков 6 или 10 на входы регистра 18 режимов поступают сигналы, которые переводят устройство в режим отладки по щагам. Информация в регистры 11, 12 заносится с их информационных входов от устройства ввода-вывода при поступлении на их входы записи управляющих сигналов .

При выполнении прог раммы МПС промежуточные результаты вычислений, для контроля правильности вьшолнения программы .МПС, могут быть занесены в регистр 7 данных от МПС (по сигналу записи), содержимое которого поступает на блок 8 индикации. Индикация может быть разрешена или запрещена по сигналу, поступающему на вход блока 8.

Формула изобретения

1 .Устройство для отладки программ, содержащее блок управления, первый регистр данных, регистр адреса, блок индикации адреса, блок сравнения адресов, блок отладочной памяти, регистр адреса останова и первый блок индикации данных, причем первый информационный вход устройства соединен с первым информационным входом первого регистра данных и информационным входом регистра адреса останова, второй информационньй вход устройства соединен с вторым информационным входом регистра данных, информационньй выход блока отладочной памяти соединен с третьим ин- . формационным входом первого регистра

данных, выход которого соединен с информационным входом первого блока индикации, с первым информационным входом блока отладочной.памяти, с первым входом блока сравнения данных

и является первым информационньм выходом устройства, первый адресный вход устройства соединен с первьм информационным входом регистра адреса, второй адресньй вход устройства соединен с вторым информационным входом регистра адреса, первый вход признака адреса устройства соединен с входом записи регистра адреса, первый выход которого соединен с информационным входом блока индика1Д1И адреса, с первым входом блока сравнения адресов и является адресным выходом устройства, второй ин- формационньй выход регистра адреса соединен с адресным входом блока отладочной памяти, выход регистра адреса останова соединен с вторым входом блока сравнения адресов, отличающееся TeMj что с целью расширения функциональных возможностей устройства за счет обеспечения отладки программ в реальных условиях, в устройство вве- дены второй регистр данньпс, второй блок индикации данных, блок нения данных, буферньй регистр, дешифратор старших разрядов адреса, четыре элемента И-НЕ, причем выходы старших разрядов регистра адреса соединены с входами дешифратора старших разрядов, адреса, первый, второй, третий и четвертьм выходы которого соединены с первьгми входами соответственно первого, второго, третьего и четвертого элементов И-НЕ, выходы которых соединены соответственно с первым, вторым, треты-т и четвертьм входами обращения блока :отладочной памяти, первый второй, третий, четвертый, пятый, шестой, ;седьмой, восьмой, девятьй, десятый, Iодиннадцатьй, двенадцатьй и тринад- Iцатый выходы блока управления соеди :нены .соответственно с первым входом записи первого регистра данных, с первым входом записи регистра адрес с входом записи блока отладочной памяти, с выходом признака записи устройства, с входом признака записи второго регистра данных, с входом признака записи регистра адреса останова, с входом чтения блока отладочной памяти, с вторым входом записи первого регистра данных, с входом разрешения индикации первого блока индикации данных, с входом разрешения индикации второго блока

о Q

5

5

5

индикации данных, с входом разрешения индикации блока индикации адреса, с третьим входом записи первого регистра данных и вторым выходом записи устройства, выход опроса обращения блока управления соединен с вторыми входами первого, второго, третьего и четвертого элементов И-НЕ, первый информационный вход устройства соединен с информационным входом блока з.гправления и инфор- мационнь1М входом второго регистра данных, выходы равенства блоков сравнения адресов и данных соединены соответственно с первым и вторым режимными входами блока управления, вход признака режима устройства соединен с входом записи режима блока управления, вход обращения устройства соединен с первым входом блока управления, вход признака данных устройства соединен с входом записи буферного регистра, третий инфор- мационньй вход устройства соединен с информационным входом буферного регистра,, выход которого соединен с информахдионным входом второго блока индика.ции5 второй вход признака адреса соединен с вторым входом записи регистра адреса и первым входом блока управления, вход признака команды устройства соединен с входом опроса дешифратора команд,

2. Устройство по n.lj, о т л.и - чающееся тем, что блок управления содержит регистр режимов, первый и второй элементы И, первьзй и второй элементы ИЛИ, первьш и второй блоки задержки и дешифратор команд, причем первый и второй режим- Hbje входы блока управления соединены с соответствующими установочными входами регистра режимов, вход признака записи режима соединен с входом записи регистра режимов, первый, второй, третий, четвертый, пятый, шестой, сэдьмой и восьмой выходы дешифратора команд соединен с первым, вторым., третьим, четвертым, пятым, и шестым выходами блока зтгравления, с первыми входами первого и второго элемента к1ПИ, вьжод которого является седьмы выходом блока и через первый элемент за,цержки соединен с восьмым выходом блока и с входом второго элемента задержки, первый, второй, третий, четвертый, пятый и шестой информационные выходы регист7 14256878

pa режимов являются соответственноэлемента ИЛИ и первого элемента И,

девятым, десятым, одиннадцатым вы-выход первого элемента И Является

ходами блока управления и соединеныдвенадцатым выходом блока, выход

с выходом опроса обращения блокавторого элемента задержки соединен

управления, с первыми входами соот-с вторым входом второго элемента И,

ветственно первого и второго эле-выход которого соединен с вторым

ментов И, первый и второй входывходом первого элемента И, выход

блока управления соединены с вторы-которого является тринадцатым выми входами соответственно второгоIQ ходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Устройство для отладки программ | 1988 |

|

SU1608673A1 |

| Устройство для отладки программ | 1982 |

|

SU1100627A1 |

| МНОГОФУНКЦИОНАЛЬНОЕ ОТЛАДОЧНОЕ УСТРОЙСТВО ДЛЯ МИКРОПРОЦЕССОРНЫХ СИСТЕМ | 2016 |

|

RU2634197C1 |

| Устройство для откладки программ | 1987 |

|

SU1474656A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для отладки программ | 1985 |

|

SU1297064A1 |

| Устройство для отладки программ | 1987 |

|

SU1462327A1 |

| Устройство для отладки программ | 1986 |

|

SU1327112A1 |

| Устройство для отладки программ | 1983 |

|

SU1104521A1 |

Изобретение относится к автоматике и вычислительной технике-и может быть использовано при отладке программ микропроцессорных систем. Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения отладки программ в реальных условиях. Устройство содержит блок 1 управления, регистры 2 и 11 данных, блоки 3 и 8 индикатдии данных, регистр 4 адреса, блок 5 индикации адреса, блоки 6 и 10 сравнения- соответственно адресов и данных, регистр 12 адреса останова, дешифратор 13 старших разрядов адреса, элементы И-НЕ 14-17. Устройство обеспечивает различные режимы обмена информацией между блоками устройства и между устройством и отлаживаемой микропроцессорной системой, дополнительные возможности запоминания и индикации информации адресации к отладочной памяти. 1 з.п. ф-лы, 1 нл. (Л

| Патент США № 4231087, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| 0 |

|

SU159914A1 | |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-09-23—Публикация

1987-02-26—Подача