/С cuHKpotfttfpo1

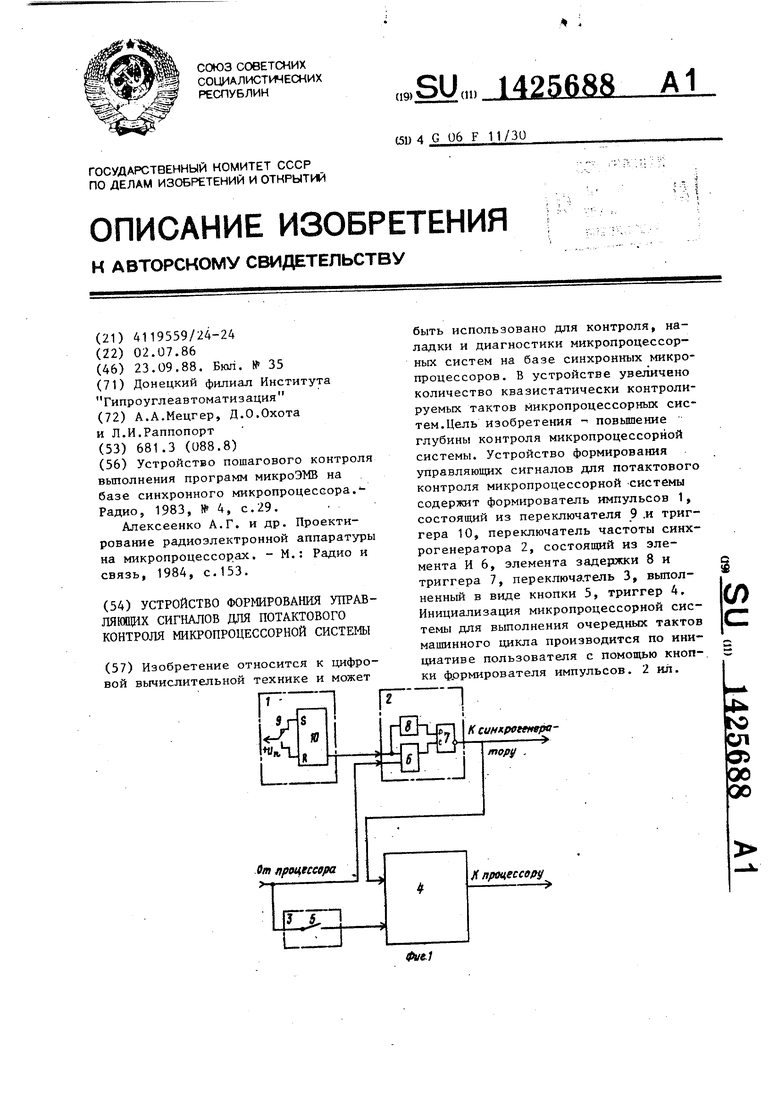

Изобретение относится к вычислительной технике и может быть использовано для контроля,, наладки и диагностики микропроцессорных систем на базе синхронных микропроцессоров.

Цель изобретения повышение глубины контроля микропроцессорной системы за счет возможности ее контроля в любом такте машинного цикла.

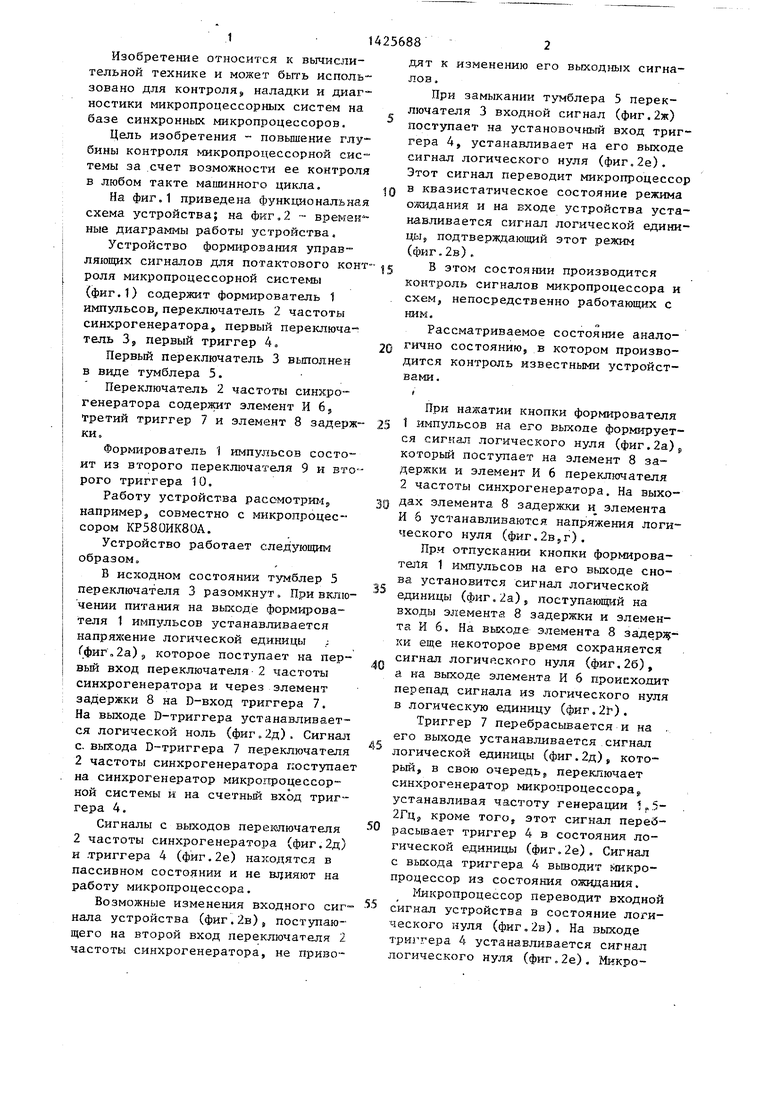

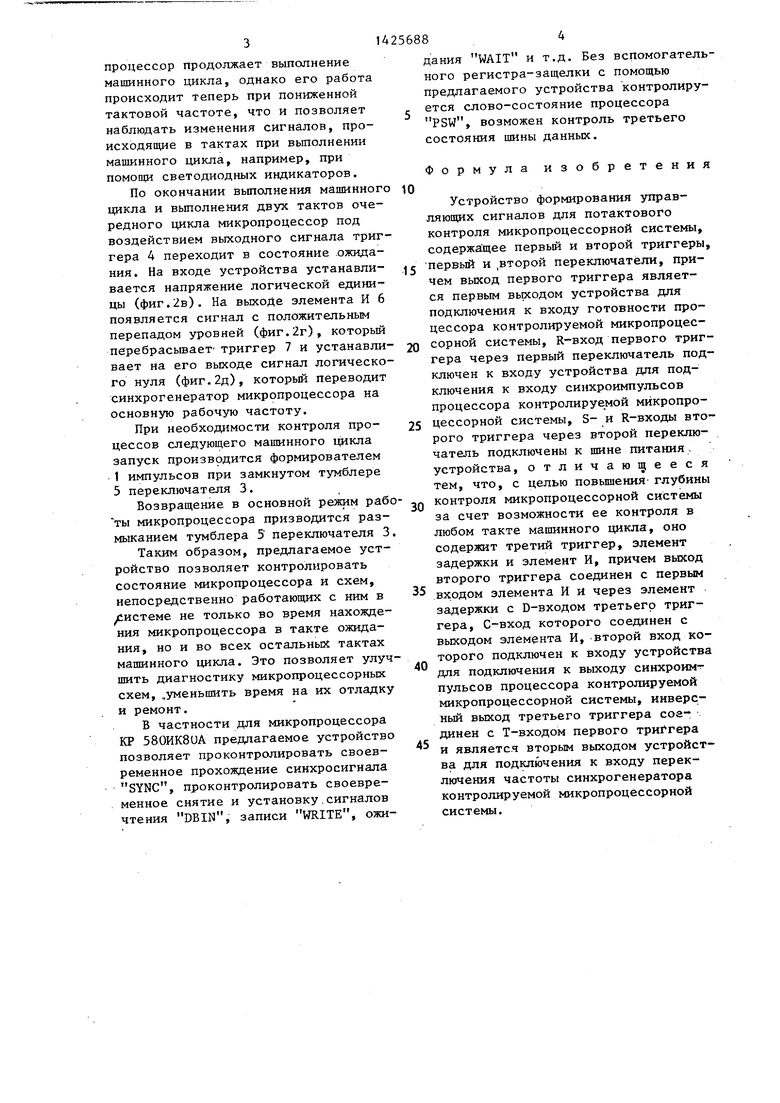

На фиг.1 приведена функциональная схема устройства; на фкг,2 - времен ные диаграммы работы устройства.

Устройство формирования управляющих сигналов для потактового конт роля микропроцессорной системы (фиг.1) содержит формирователь 1 импульсов, переключатель 2 частоты синхрогенератора, первый переключа

тель 3, первый триггер 4

Первый переключатель 3 выполнен в виде тумблера 5.

Переключатель 2 частоты синхро-- генератора содержит элемент И 6, третий триггер 7 и элемент 8 задержки.

Формирователь 1 импульсов состоит из второго переключателя 9 и второго триггера 10,

Работу устройства расомотрш р например, совместно с микропроцессором КР580ИК80А.

Устройство работает следующш образом,

В исходном состоянии тумблер 5 переключателя 3 разомкнут. При включении питания на выходе формирователя 1 импульсов устанавливается напрях ение логической единицы : ()э которое поступает на первый вход переключателя 2 частоты синхрогенератора и через элемент задержки 8 на D-вход триггера 7. На выходе D-триггера устанавливается логической ноль (фиг.2д). Сигнал с. выхода D-триггера 7 переключателя 2 частоты синхрогенератора поступае на синхрогенератор микропроцессорной системы и на счетный вход триггера 4,

Сигналы с выходов переключателя 2 частоты синхрогенератора (фиг.2д) и .триггера 4 (фиг.2е) находятся в пассивном состоянии и не влияют на работу микропроцессора.

Возможные изменения входного сигнала устройства (фиг.2в), поступающего на второй вход переключателя 2 частоты синхрогенератора, не привоQ

0

5

0

5

0

5

0

5

дят к изменению его вькодных сигналов.

При замыкании тумблера 5 переключателя 3 входной сигнал (фиг.2ж) поступает на установочный вход триггера 4j устанавливает на его выходе сигнал логического нуля (фиг.2е). Этот сигнал переводит микропроцессор в квазистатическое состояние режима ожидания и на входе устройства устанавливается сигнал логической единицы, пoдтвepщ aющий этот режим (фиг.2в).

В этом состоянии производится контроль сигналов микропроцессора и схем, непосредственно работающих с ним.

Рассматриваемое состояние аналогично состоянию, в котором производится контроль известными устройствами. I

При нажатии кнопки формирователя

1импульсов на его выходе формируется сигнал логического нуля (фиг,2а)5 который поступает на элемент 8 задержки и элемент И 6 переключателя

2частоты синхрогенератора. На выходах элемента 8 задержки и элемента

И б устанавливаются напряжения логического нуля (фиг.2в5г).

При отпускании кнопки формирователя 1 импульсов на его вькоде снова установится сигнал логической единицы (фиг.2а)5 поступающий на входы элемента 8 задержки и элемента И б . На выходе элемента 8 задерг - ки еще некоторое время сохраняется сигнал логического нуля (фиг.26), а на выходе элемента И 6 происходит перепад сигнала из логического нуля в логическую единицу (фиг,2).

Триггер 7 перебрасьшается и на , его выходе устанавливается сигнал логической единицы (фиг.2д), который, в свою очередьJ переключает синхрогенератор микропроцессора устанавливал частоту генерации 1р5- 2Гц5 кроме того, этот сигнал перебрасывает триггер 4 в состояния логической единицы (фиг.2е). Сигнал с выхода триггера 4 вьшодит микропроцессор из состояния ожидания.

Шкропроцессор переводит входной сигнал устройства в состояние логического нуля (фиг,2в). На выходе триг гера 4 устанавливается сигнал логического нуля (фиг.2е). Микропроцессор продолжает выполнение машинного цикла, однако его работа происходит теперь при пониженной тактовой частоте, что и позволяет наблюдать изменения сигналов, происходящие в тактах при вьшолнении машинного цикла, например, при помощи светодиодных индикаторов.

По окончании выполнения машинного цикла и выполнения двух тактов очередного цикла микропроцессор под воздействием выходного сигнала триггера 4 переходит в состояние .ожидания. На входе устройства устанавливается напряжение логической единицы (фиг.2в). На выходе элемента И 6 появляется сигнал с положительным перепадом уровней (фиг.2г), который перебрасьгоает триггер 7 и устанавливает на его выходе сигнал логического нуля (фиг.2д), которьй переводит синхрогенератор микропроцессора на основную рабочую частоту.

При необходимости контроля процессов следующего машинного цикла запуск производится формирователем 1 импульсов при замкнутом тумблере 5 переключателя 3.

Возвращение в основной режим рабо ты микропроцессора призводится размыканием тумблера 5 переключателя 3.

Таким образом, предлагаемое устройство позволяет контролировать состояние микропроцессора и схем, непосредственно работающих с ним в истеме не только во время нахождения микропроцессора в такте ожидания, но и во всех остальных тактах машинного цикла. Это позволяет улучшить диагностику микропроцессорных схем, ,уменьшить время на их отладку и ремонт.

В частности для микропроцессора КР 580ИК8иА предлагаемое устройство позволяет проконтролировать своевременное прохождение синхросигнала SYNC, проконтролировать своевременное снятие и установку.сигналов чтения DBIN, записи WRITE, ожидания WAIT и т.д. Без вспомогательного регистра-защелки с помощью предлагаемого устройства контролируется слово-состояние процессора PSW, возможен контроль третьего состояния шины данных.

Формула изобретения

10

Устройство формирования управляющих сигналов для потактового контроля микропроцессорной системы, содержа:щее первый и второй триггеры,

первый и .второй переключатели, причем выход первого триггера является первым вьрсодом устройства для подключения к входу готовности процессора контролируемой микропроцессорной системы, R-вход первого триггера через первый переключатель подключен к входу устройства для подключения к входу синхроимпульсов процессора контролируемой мйкропроцессорной системы, S- и R-входы второго триггера через второй переключатель подключены к шине питания ,

0

5

устройства,

о т л и ч а

ю q

е е с я

тем, что, с целью повьш1ения глубины Q контроля микропроцессорной системы за счет возможности ее контроля в любом такте машинного цикла, оно содержит третий триггер, элемент задержки и злемент И, причем выход второго триггера соединен с первым входом элемента И и через элемент задержки с D-входом третьего триггера, С-вход которого соединен с выходом элемента И, второй вход которого подключен к входу устройства для подключения к выходу синхроим- пульсов процессора контролируемой микропроцессорной системы, инверс- ньш выход третьего триггера соединен с Т-входом первого и является вторым выходом устройства для подключения к входу переключения частоты синхрогенератора контролируемой микропроцессорной системы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема информации в частотном коде | 1986 |

|

SU1394458A1 |

| Программируемый формирователь временных интервалов | 1987 |

|

SU1499439A1 |

| Устройство приоритета | 1990 |

|

SU1829033A1 |

| Устройство микропроцессорного управления и обработки информации | 1979 |

|

SU947867A1 |

| Устройство для установки микропроцессоров в исходное состояние | 1986 |

|

SU1424018A1 |

| Система для проведения испытаний турбины | 1989 |

|

SU1636706A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1737453A1 |

| Устройство для сопряжения микропроцессорной системы с внешними устройствами с контролем | 1984 |

|

SU1242956A1 |

| Устройство для поиска перемежающихся неисправностей | 1986 |

|

SU1381511A1 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1545221A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано для контроля, наладки и диагностики микропроцессор- ных систем на базе синхронных микропроцессоров. В устройстве увеличено количество квазистатически контролируемых тактов микропроцессорных систем.Цель изобретения - повышение глубины контроля микропроцессорной системы. Устройство формирования управляющих сигналов для потактового контроля микропроцессорной Системы содержит формирователь импульсов 1, состоящий из переключателя 9 .и триггера 10, переключатель частоты синх- рогенератора 2, состоящий из элемента И 6, элемента задероиси 8 и триггера 7, переключэ,тель 3, вьтол- ненный в виде кнопки 5, триггер 4. Инициализация микропроцессорной системы для выполнения очередных тактов машинного цикла производится по инициативе пользователя с помощью кноп-. ки фррмирователя импульсов. 2 ил. С/)

| Устройство пошагового контроля выполнения программ микроЭМВ на базе синхронного микропроцессора.- Радио, 1983, № 4, с.29 | |||

| Алексеенко А.Г | |||

| и др | |||

| Проектирование радиоэлектронной аппаратуры на микропроцессорах | |||

| - М.: Радио и связь, 1984, с.153. |

Авторы

Даты

1988-09-23—Публикация

1986-07-02—Подача