оо

00

оо оо ю оо

Изобретение относится к вычислительной технике и может быть использовано в блоках задержки цифровой информации.

Цель изобретения - повышение достоверности задержанной информации.

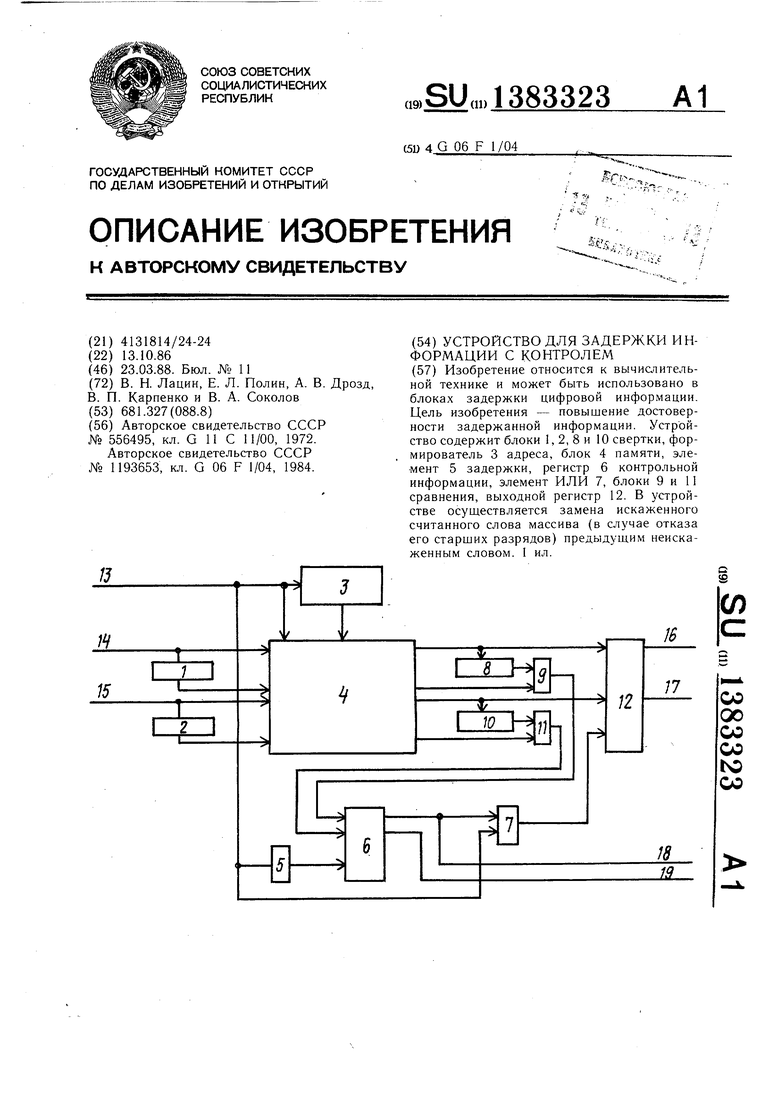

На чертеже представлена структурная схема устройства для задержки информации с контролем.

Устройство содержит первый 1 и второй 2 блоки свертки, формирователь 3 адреса,

те на выходе выходного регистра 12 сохраняется значение предыдущего считанного слова, которое для данного класса описываемых задерживаемым массивом функций незначительно отличается от истинного значения искаженного слова. Чем меньше максимально возможная скорость изменения описываемых массивом функций, тем точнее заменено искаженное слово, т.е. тем больше уменьшена максимально возможная погрешФормула изобретения

блок 4 памяти, элемент 5 задержки, регистр 10 ность в случае отказа старших разрядов 6 контрольной информации, элемент ИЛИ 7,слова,

третий блок 8 свертки, первый блок 9 сравнения, четвертый блок 10 свертки, второй блок 11 сравнения, выходной регистр 12, вход 13 синхронизации устройства, информационный вход 14 старших разрядов, информационный вход 15 младших разрядов, информационный выход 16 старших разрядов, информационный выход 17 младших разрядов, выход 18 наличия ошибки в стар15

Устройство для задержки информации с контролем, содержаш.ее формирователь адреса, блок памяти и выходной регистр, причем выходы старших и младших информационных разрядов блока памяти подключены к информационным входам выходного

ших разрядах, выход 19 наличия ошибки в 20 регистра, выходы которого являются информладших разрядах.

Устройство работает следующим образом.

В начальный момент времени происходит обнуление всех регистров устройства. Цепи обнуления условно не показаны. Далее на входы 14 и 15 устройства начинают поступать слова задерживаемого массива, сопровождаемые синхроимпульсами типа меандр на входе 13 синхронизации устройства. Причем во время первой половины

25

мационными выходами устройства, выход формирователя адреса подключен к адресному входу блока памяти, информационные входы старших и младших разрядов блока памяти являются информационными входами устройства, отличющееся тем, что, с целью повышения достоверности задержанной информации, в него введены с первого по четвертый блоки свертки, первый и второй блоки сравнения, элемент задержки.

такта происходит чтение информации из о регистр контрольной информации и эле- ячейки, адрес которой установлен форми- „..

рователем 3, а во время второй половины - запись информации в эту же ячейку. Формирователь 3 последовательно перебирает адреса ячеек. Коэффициент пересчета его определяет величину задержки массива. Информационные разряды (старшие и младшие) записывают в блок 4 вместе с соответствующими контрольными разрядами, вычисленными блоками 1 и 2 свертки. При чтении снова происходит вычисление контрольных разрядов для старшей и младшей частей числа и сравнение их с оответствующими контрольными разрядами, считанными из блока памяти. Результат сравнения фиксируется в регистре 6. В случае совпадения в регистр 6 записывается код «00, свидемент ИЛИ, причем синхровод формирователя адреса, вход записи-чтения блока памяти, вход элемента задержки и первый вход элемента ИЛИ объединены и являются входом синхронизации устройства, входы пер- ос вого и второго блоков свертки подключены к информационным входам старших и младших разрядов блока памяти, выходы первого и второго блоков свертки подключены к первому и второму входам контрольных разрядов блока памяти, информационные входы старших и младших разрядов блока памяти подключены соответственно к входам третьего и четвертого блоков свертки, выходы которых подключены к первым входам первого и второго блоков сравнения, выходы первого и второго конт40

тельствующий о нормальной работе устрой- рольных разрядов блока памяти подключе- ства. При этом элемент ИЛИ 7 пропуска-ны к вторым входам первого и второго блоет задний фронт синхроимпульса с входа 13 синхронизации на синхровход выходного регистра 12, занося в него считанное в данном такте информационное слово. Аналогично происходит прием в выходной регистр 12, если обнаружено искажение в младщей части считанного числа (код в регистре 6 «01), так как это приводит к незначительной погрещности представления данного слова. В случае искажения старшей части (код в регистре 6 «10) или старшей и младшей частей (код «11) происходит блокировка приема в выходной регистр 12 значительно искаженного слова, и в данном так50

55

ков сравнения соответственно, выходы первого и второго блоков сравнения подключены к первому и второму информационным входам регистра контрольной информации, синхровход которого соединен с выходом элемента задержки, первый и второй выходы регистра контрольной информации являются соответственно выходами наличия ошибки в старших и младших разрядах устройства соответственно, второй вход элемента ИЛИ подключен к первому выходу регистра контрольной информации, выход элемента ИЛИ соединен с входом синхронизации выходного регистра.

те на выходе выходного регистра 12 сохраняется значение предыдущего считанного слова, которое для данного класса описываемых задерживаемым массивом функций незначительно отличается от истинного значения искаженного слова. Чем меньше максимально возможная скорость изменения описываемых массивом функций, тем точнее заменено искаженное слово, т.е. тем больше уменьшена максимально возможная погреш ность в случае отказа старших разрядов слова,

Формула изобретения

Устройство для задержки информации с контролем, содержаш.ее формирователь адреса, блок памяти и выходной регистр, причем выходы старших и младших информационных разрядов блока памяти подключены к информационным входам выходного

регистра, выходы которого являются инфор

мационными выходами устройства, выход формирователя адреса подключен к адресному входу блока памяти, информационные входы старших и младших разрядов блока памяти являются информационными входами устройства, отличющееся тем, что, с целью повышения достоверности задержанной информации, в него введены с первого по четвертый блоки свертки, первый и второй блоки сравнения, элемент задержки.

регистр контрольной информации и эле- „..

регистр контрольной информации и эле- „..

мент ИЛИ, причем синхровод формирователя адреса, вход записи-чтения блока памяти, вход элемента задержки и первый вход элемента ИЛИ объединены и являются входом синхронизации устройства, входы пер- вого и второго блоков свертки подключены к информационным входам старших и младших разрядов блока памяти, выходы первого и второго блоков свертки подключены к первому и второму входам контрольных разрядов блока памяти, информационные входы старших и младших разрядов блока памяти подключены соответственно к входам третьего и четвертого блоков свертки, выходы которых подключены к первым входам первого и второго блоков сравнения, выходы первого и второго конт

рольных разрядов блока памяти подключе- ны к вторым входам первого и второго бло0

5

ков сравнения соответственно, выходы первого и второго блоков сравнения подключены к первому и второму информационным входам регистра контрольной информации, синхровход которого соединен с выходом элемента задержки, первый и второй выходы регистра контрольной информации являются соответственно выходами наличия ошибки в старших и младших разрядах устройства соответственно, второй вход элемента ИЛИ подключен к первому выходу регистра контрольной информации, выход элемента ИЛИ соединен с входом синхронизации выходного регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для задержки цифровой информации | 1986 |

|

SU1383327A1 |

| Устройство для задержки информации с контролем | 1990 |

|

SU1795442A1 |

| Устройство для задержки цифровой информации с контролем | 1987 |

|

SU1462424A1 |

| Устройство для контроля информационного тракта "запоминающее устройство команд-процессор | 1980 |

|

SU1005060A2 |

| Устройство для контроля динамических блоков памяти | 1985 |

|

SU1282221A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для сопряжения вычислительной машины с магистралью обмена | 1986 |

|

SU1381519A1 |

| Устройство сопряжения между процессором верхнего уровня и группой процессоров нижнего уровня иерархической мультипроцессорной системы | 1990 |

|

SU1789988A1 |

| Устройство для задержки цифровой информации с самоконтролем | 1986 |

|

SU1429174A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

Изобретение относится к вычислительной технике и может быть использовано в блоках задержки цифровой информации. Цель изобретения - повышение достоверности задержанной информации. Устройство содержит блоки 1, 2, 8 и 10 свертки, формирователь 3 адреса, блок 4 памяти, элемент 5 задержки, регистр 6 контрольной информации, элемент ИЛИ 7, блоки 9 и 11 сравнения, выходной регистр 12. В устройстве осуществляется замена искаженного считанного слова массива (в случае отказа его старших разрядов) предыдущим неискаженным словом. I ил.

| Запоминающее устройство | 1975 |

|

SU556495A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для программируемой задержки информации | 1984 |

|

SU1193653A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-03-23—Публикация

1986-10-13—Подача