(61) 1246379

(21)4231561/24-24

(22)23.03,87

(46) 23.09.88. Бюл, № 35

(71)Московское отделение Центрального научно-исследовательского института связи

(72)К.М. Муссель, В,А. Минаев, Е.Л. Горн и В.Н. Гритченко

(53)621.378.58(088.8)

(56)Авторское свидетельство СССР № 1246379, кл. Н 03 М 3/02, 1984.

(54)АДАПТИВНЫЙ ДЕЛЬТА-МОДУЛЯТОР

(57)Изобретение относится к электросвязи и может использоваться в системах передачи информации. Изобретение позволяет повысить достоверность

,//

дельта-модулятора за счет введения блока 12 начальной установки, обнуляющего счетчик 5 после включения источника питания при появлении сигналов разрешения счета на выходе счетчика 4 и импульса переполнения счетчика 5. Адаптивный дельта-модулятор содержит компаратор 1, .гер 2, полусумматор 3, счетчик 4 задержки, реверсивный счетчик 5, управляемые ключи 6, резистивную матрицу 7,, интегратор 8, информационный вход 9, выход 10, тактовый вход 11 и блок 12 начальной установки5 выполненный на формирователе 13 импульса, RS-триг- гере 14, элементах И-НЕ 15, 16, элементе ИЛИ 17 и элементе задержки 18, 2 ил.

и

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обучения чтению | 1989 |

|

SU1665401A1 |

| "Устройство для декодирования кода "Манчестер-2" | 1990 |

|

SU1809536A1 |

| Устройство для цифровой записи воспроизведения речевой информации | 1988 |

|

SU1573470A1 |

| Адаптивный дельта-модулятор | 1984 |

|

SU1246379A1 |

| Дельта-модулятор | 1990 |

|

SU1709531A2 |

| Дельта-модулятор | 1985 |

|

SU1257849A1 |

| Адаптивный восстанавливающий фильтр в дельта-модуляторе с двойным интегрированием | 1990 |

|

SU1795553A1 |

| Устройство слежения за дорожкой дискового носителя информации | 1987 |

|

SU1614031A1 |

| Цифровой синтезатор частот | 1986 |

|

SU1497704A1 |

| УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ РЕЧЕВОЙ ИНФОРМАЦИИ | 1992 |

|

RU2008728C1 |

ф1/е.1

Изобретение относится к электросвязи и может использоваться для передачи аналоговых сигналов по циф- poBbw каналам, а также в системах передачи речевых сообщений и является усовершенствованием устройства по авт.св.; № 1246379.

Целью изобретения является повышение достоверности дельта-модуля- тора„

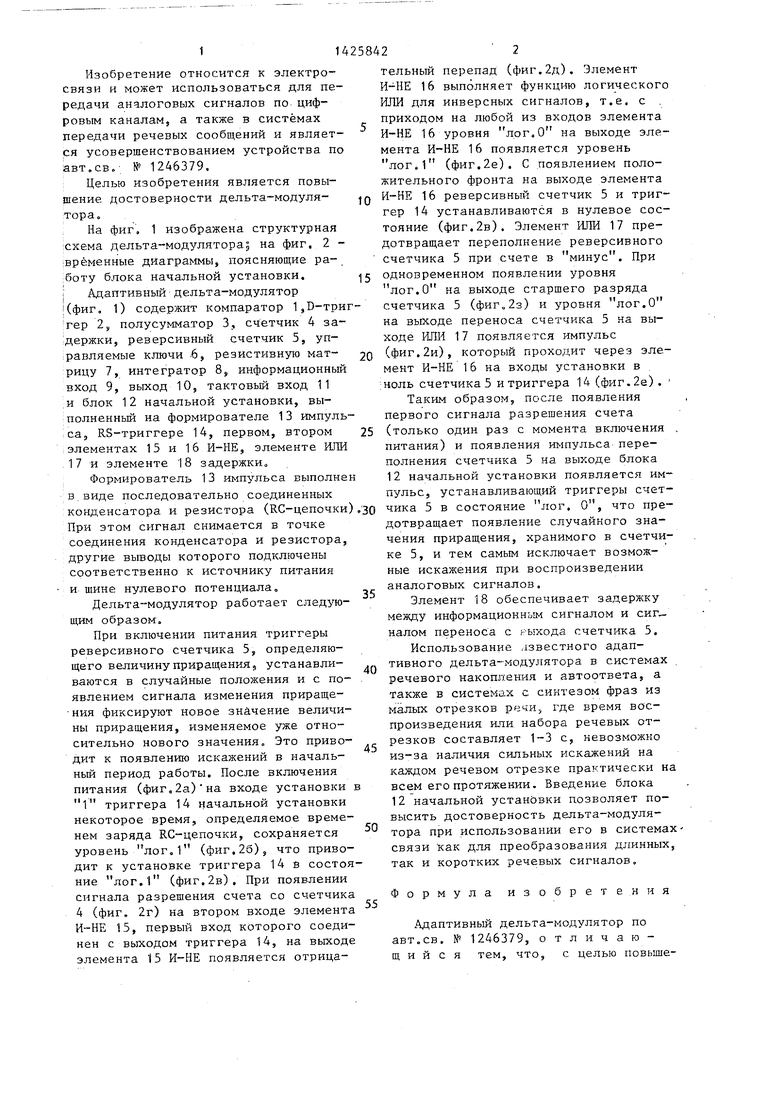

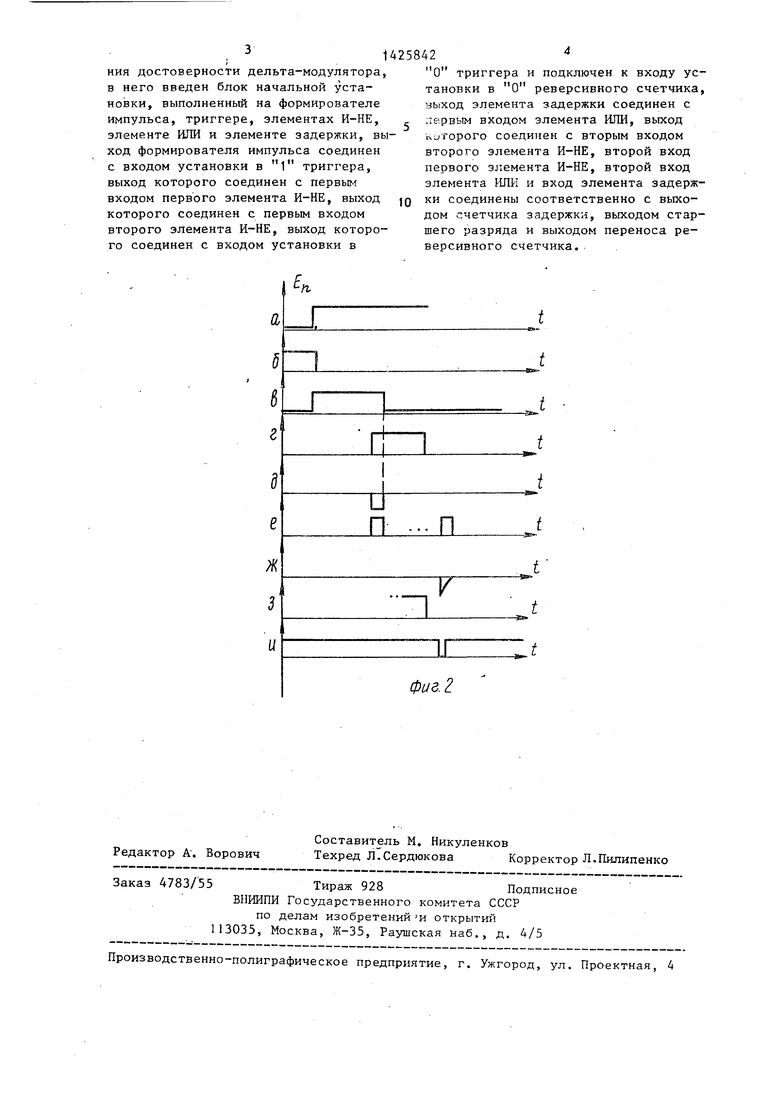

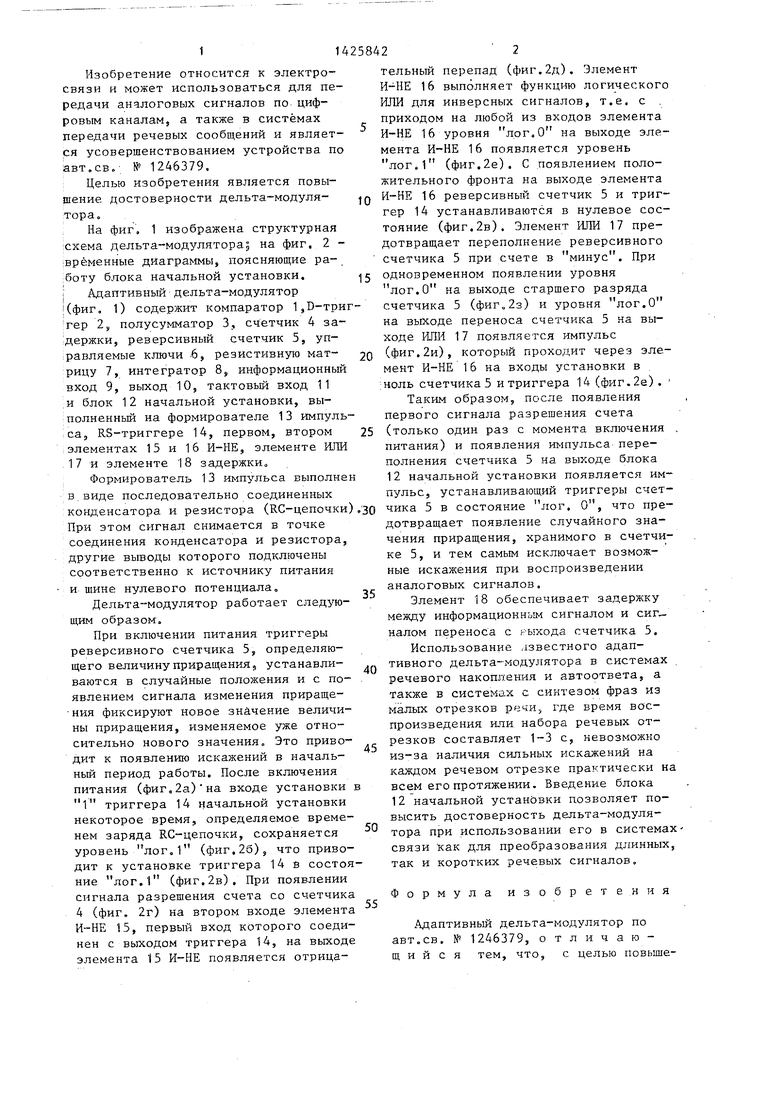

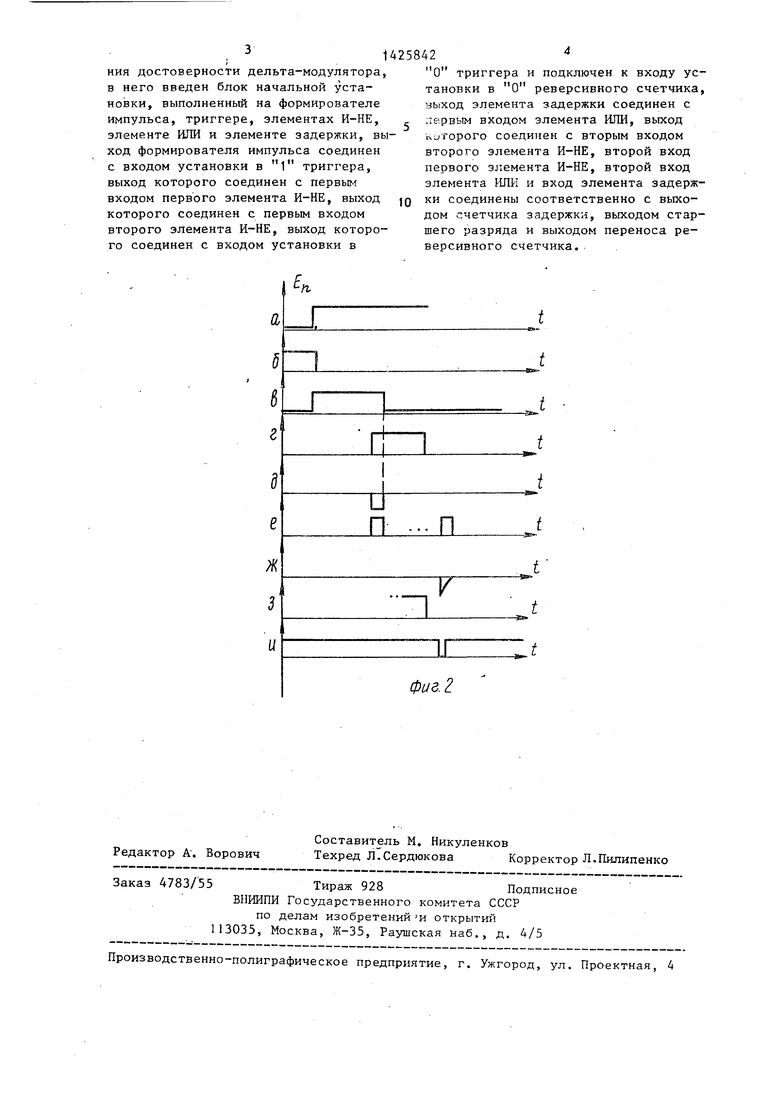

На фиг, 1 изображена структурная схема дельта-модулятора5 на фиг, 2 - временные диаграммы, поясняющие ра- ;6оту блока начальной установки. j Адаптивный дельта-модулятор Кфиг, 1) содержит компаратор 1,В-три ;гер 2 к полусумматор 3, счетчик 4 за- держки, реверсивный счетчик 5, управляемые ключи 6, резистивную мат- рицу 7, интегратор 8, информадионньй вход 9, выход 10, тактовый вход 11 ,и блок 12 начальной установки, вы- полненньш на формирователе 13 импуль :са, RS-триггере 14, первом, втором элементах 15 и 16 И-НЕ, элементе ИЛИ ,17 и элементе 18 задержки.

Формирователь 13 импульса выполне в.виде последовательно соединенных

конденсатора и резистора (RC-цепочки) . ЗО чика 5 в состояние лог. О, что преПри этом сигнал снимается в точке соединения конденсатора и резистора, другие выводы которого подключены соответственно к источнику питания и шине нулевого потенциала.

Дельта-модулятор работает следующим образом.

При включении питания триггеры реверсивного счетчика 5, определяющего величину приращения5 устанавливаются в случайные положения и с появлением сигнала изменения прираще- ния фиксируют новое значение величины приращения, изменяемое уже относительно нового значения„ Это приводит к появлению искажений в начальный период работы. После включения питания (фиг,2а) на входе установки 1 триггера 14 начальной установки некоторое время, определяемое временем заряда RC-цепочки, сохраняется уровень лог,1 (фиг,26), что приводит к установке триггера 14 s состояние лог.1 (фиг.2в). При появлении сигнала разрешения счета со счетчика 4 (фиг. 2г) на втором входе элемента 15, первый вход которого соединен с выходом триггера 14, на выходе элемента 15 И-НЕ появляется отрицательный перепад (фиг.2д). Элемент И-НЕ 16 выполняет функцию логического ИЛИ для инверсных сигналов, т.е. с приходом на любой из входов элемента И-НЕ 16 уровня лог.О на выходе элемента И-НЕ 16 появляется уровень лог.1 (фиг.2е). С появлением положительного фронта на выходе элемента И-НЕ 16 реверсивный счетчик 5 и триггер 14 устанавливаются в нулевое состояние (фиг.2в). Элемент ИЛИ 17 предотвращает переполнение реверсивного счетчика 5 при счете в минус. При одновременном появлении уровня лог.О на выходе старшего разряда счетчика 5 (фиг„2з) и уровня лог.О на выходе переноса счетчика 5 на выходе ИШ1 17 появляется импульс (фиг.2и), который проходит через элемент И-НЕ 16 на входы установки в :ноль счетчика 5 и триггера 14 (фиг.2е).

Таким образом, после появления первого сигнала разрешения счета (только один раз с момента включения питания) и появления импульса переполнения счетчика 5 на выходе блока 12 начальной установки появляется импульс, устанавливающий триггеры счет5

0

Гэ

0

5

дотвращает появление случайного значения приращения, хранимого в счетчике 5, и тем самым исключает возможные искажения при воспроизведении аналоговых сигналов.

Элемент 18 обеспечивает задержку между информационнь м сигналом и сиг- налом переноса с рыхода счетчика 5.

Использование известного адаптивного дельта-модулятора в системах речевого накопления и автоответа, а также в системах с синтезом фраз из малых отрезков речи, где время воспроизведения или набора речевых отрезков составляет 1-3 с, невозможно из-за наличия сильных искажений на каждом речевом отрезке практически на всем его протяжении. Введение блока 12 начальной установки позволяет повысить достоверность дельта-модулятора при использовании его в системах- связи как для преобразования длинных, так и коротких речевых сигналов.

Формула изобретения

Адаптивный дельта-модулятор по авт.св. № 1246379, отличающийся тем, что, с целью повыше;.

ния достоверности дельта-модулятора,

в него введен блок начальной установки, выполненный на формирователе импульса, триггере, элементах И-НЕ, элементе ИЛИ и элементе задержки, вы ход формирователя импульса соединен с входом установки в 1 триггера, выход которого соединен с первым входом первого элемента И-НЕ, выход которого соединен с первым входом второго элемента И-НЕ, выход которого соединен с входом установки в

П

ж 3 и

триггера и подключен к входу ус- 0

25842 О

тановки в U реверсивного счетчика, выход элемента задержки соединен с J- лервым входом элемента ИЛИ, выход

KLifoporo соединен с вторым входом второго элемента И-НЕ, второй вход первого элемента И-НЕ, второй вход элемента ИЛИ и вход элемента задерж- 10 ки соединены соответственно с выходом счетчика задержки, выходом старшего разряда и выходом переноса реверсивного счетчика.

п ... п

фиг. г

Авторы

Даты

1988-09-23—Публикация

1987-03-23—Подача