I. Изобретение относится к области цифровой вычислительной техники и может бьпь.,исголь- зовано при построении устройств преобразования информации. Известен преобразователь двоичного кода в двоично-десятичный, содержащий двоичные ком бинационные сумматоры весов двоично-десятичньгх разрядов, выполне1гаь е на двоичных полусумматорах и блоках переносов 1. Недостатком известного устройства является .боль шой объем необходимой аппаратуры. Наиболее близким решением данной техлической задачи является преобразователь двоичного кода в двоично-десятичный, содержащий ярусы суммирующих блоков, выходы суммирующих блоков каждого яруса соединены со входами суммирующих блоков соседнего старщего яруса, а входы суммирующих блоков младщего яруса соединены с нишами входного кода 2. Недостатком известного устройства является его относительно большая сложность и низкая надежность. Целью предлагаемого устройства является упрощение преобразователя и повыщение его надежности.... ,,..i.,, . ,, Это достигается тем, что i-й (i 1-4- ) ярус, где п - число разрядов двоичного кода, содержит (п-3i) сумматоров по модулю десять, первые входы которых имеют вес 2, второй и третий входы имеют вес 2, четвертый вход имеет вес 2, выходы переноса трех старших сумматоров по модулю десять i.-ro яруса соединены с четвертым, вторым и первым входами старшего сумматора по модулю дес51ть t+l)-ro яруса соответственно, выходы перен с остальных сумматоров по модулю десять, за исключением младщего, -го яруса соединены с первыми входами соответствующих сумматоров по модулю десять (i+l)-ro яруса, четвертый и второй входы старшего сумматора по модулю десять первого яруса соединены с щшшми входного кода с весами 2 и 2 соответственно, первые входы остальных сумматоров по модулю десять первого яруса соединены с соответствующими шинами входного кода, первый вь1ход, имеющий вес

2, сумматора по модулю десять соединен с четвертым входом соседнего младшего сумматора цр модулю десять того же яруса, второй и третий выходы, имеюшие вес 2, сумматора по модулю соединены с одноименнь1ми входами соседнего младшего сумматора по модУлю десять того же яруса, выходы младших сумматоров по модулю десять все;с ярусов и выходы Переноса сумматороб по модулю, десять старшего яруса соединены с выходными шннамй. Кроме того, предноженйое устройство отличается тем, что в нем сумматор ло модулю десять содержит шесть эйЬмейтбв И-НЕ и три элемента ИЛИ-НЕ, выходы пбрBWX трбх элементов И-НЕ соединены с инверсными входгвии четвертого, пятогои шестого элементов И-НЕ соответственно, первый ВХОД первого элемента ЙЛИ-НЕ соединен с 1шверсным входом Первого цемента И-НЕ и с выходом Элемента И-НЕ, второй вход - с выходом nepBCfto элемента И-НЕ, с перйым входом второго элемента ИЛИ-НЕ к с nepBbiM входом шестого элемента И-НЕ, а выход первого элемента ИЛИ-НЕ явлйется выходом йереноса сумматора по модулю десять, первь1й вхой которого соединен с первыми входами второго, третьего и nkroro элементов И-НЕ, второй вход соединен с первым входом первого элемента И-НЕ и первым входом четвертого э лемента И-НЕ, третий вход умматора модули десять соединен со вторым входом третьего элемента И-НЕ и первый входом третьего элемента ИЖ-НЕ, второй вход которого соединен со вторь м входом второго элемента ИЛИ-НЕ, выходЪм Шестого элемента И-Н& и вторым выходом сумматора по модулю десять, третий вход третьего элемента ИЛИ-НЕ соединен с выходом четвертого элемента И-НЕ, а выход является первым выходом сумматора по модулю десять, третий ыход, которого соединен с выходом вМрого элемента HJW(-HE, 1фетий вход которого с выходом пятого элеме гта И-НЕ, четверть1Й вход сумматора по МоДул десяти соединен со вторыми входами первого, второго и шестого элементов И-НЕ.

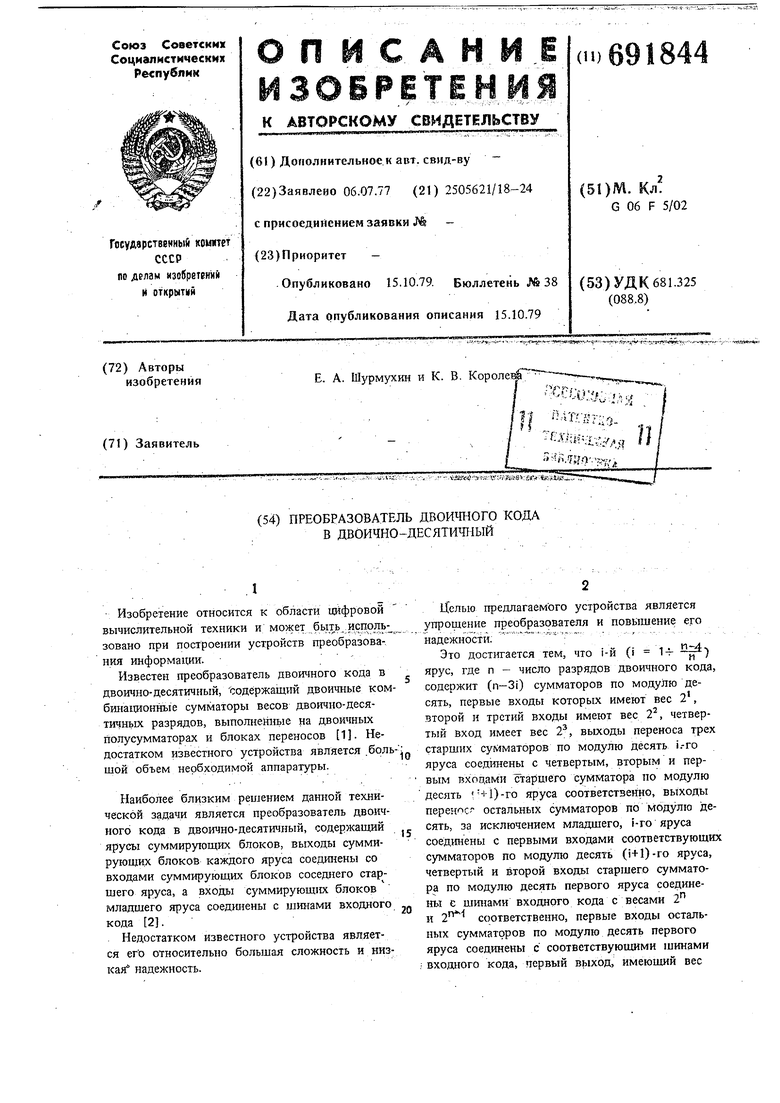

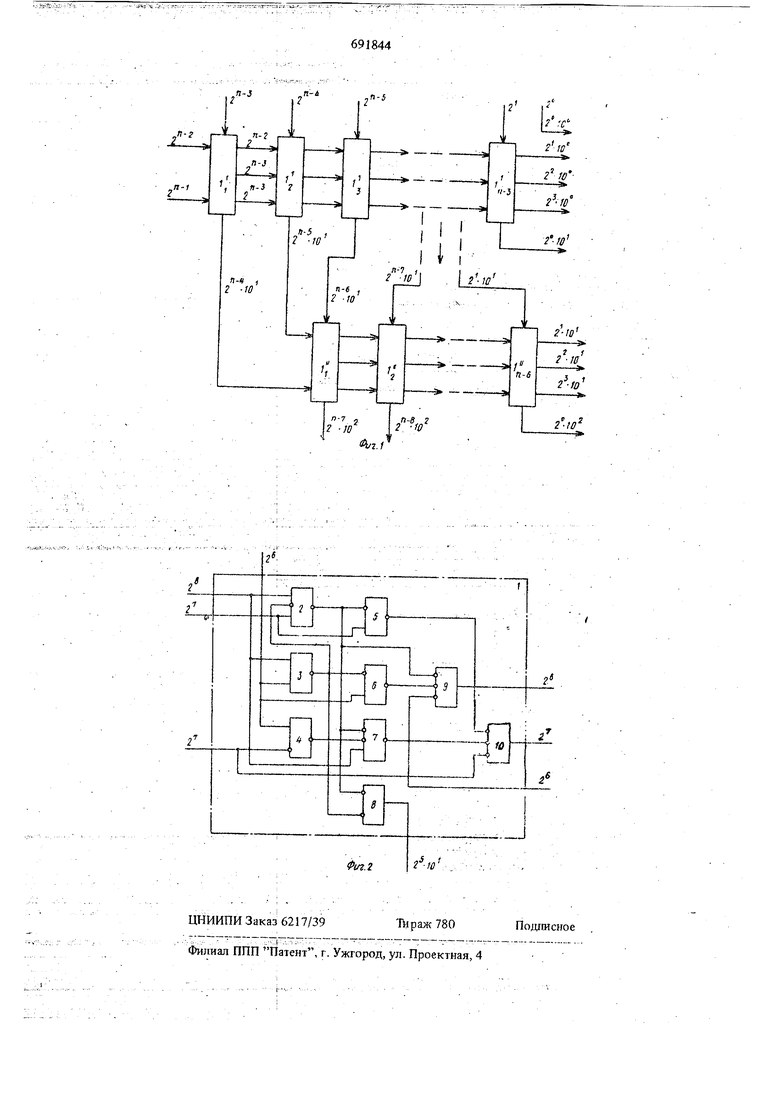

На фиг. 1 представлена структурная схема преобразователя./

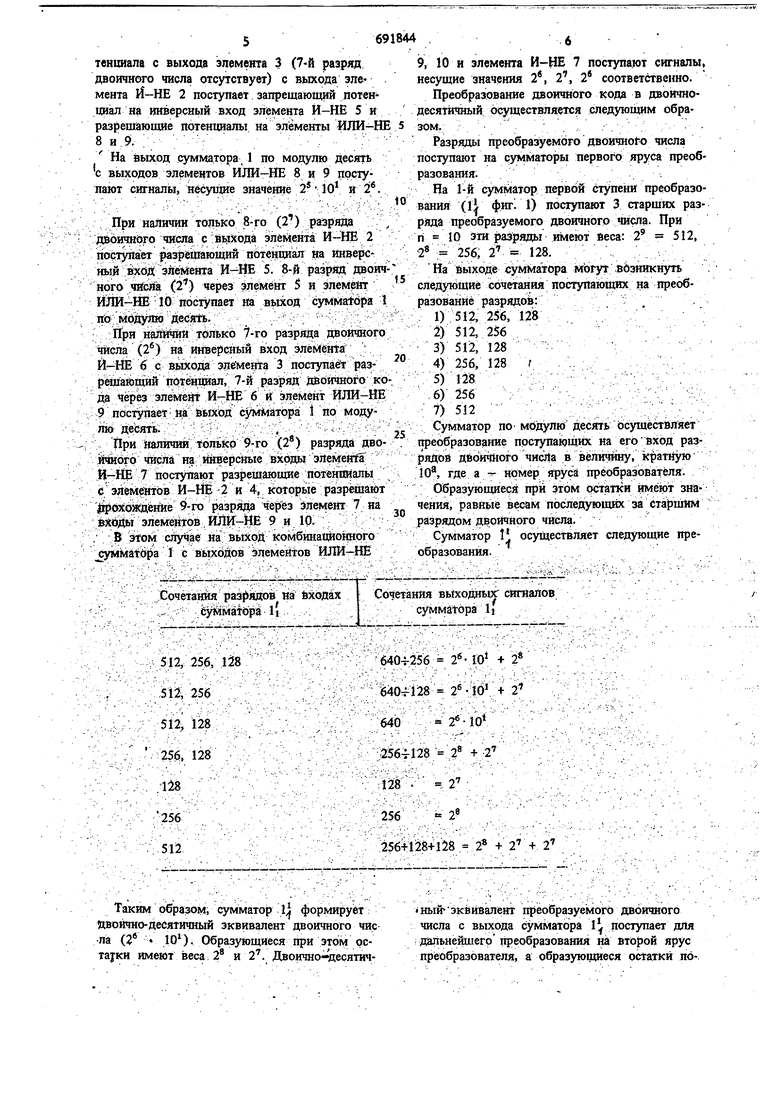

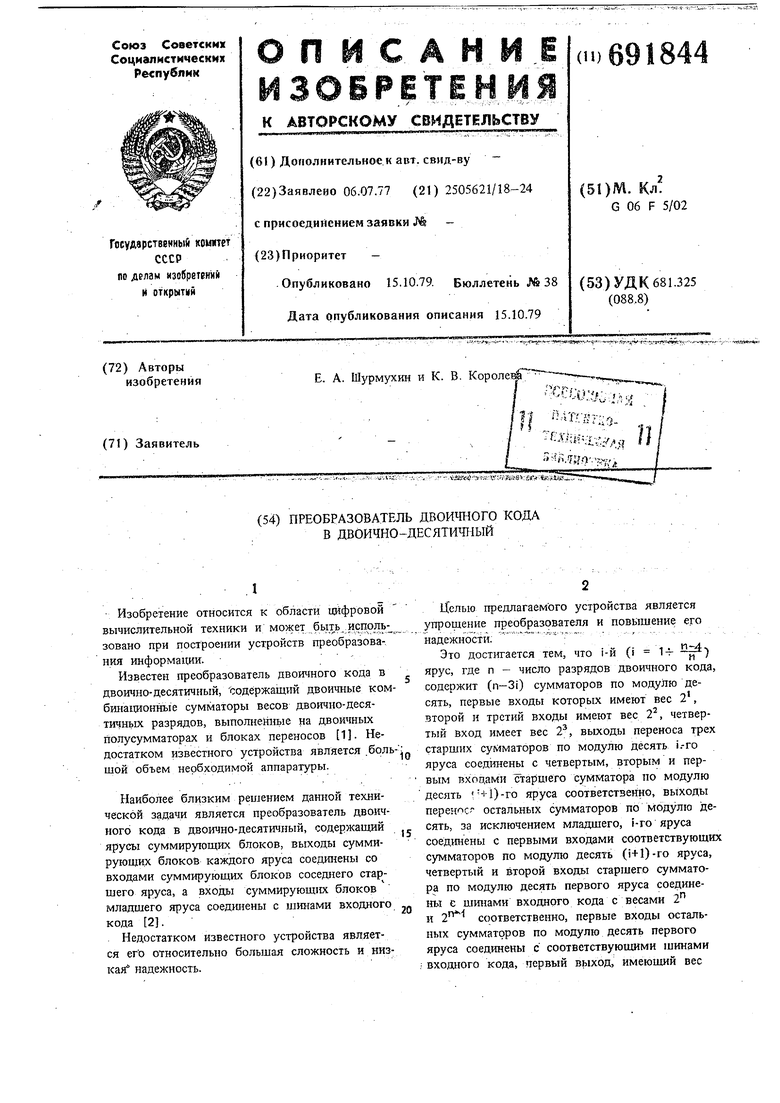

На фиг- 2 - блок-схема сумматора по модулю десять.

Предлагаемый преобраэователь содерн ит последовательно соединенные сумматоры 1 по модулю десять, которые образуют - яруса. Первый ярус содержит (п-0) сумматора 1 по модулю десять,. где п - количество разрядов преобразуемого двоичного числа. На 1ВХОД каждого комбинаш1онного сумматора ja-ln-3. кроме первого Il, образующих пер691844

ВЫЙ ярус, поступает один разряд преобразуе- . мого двоичного числа, а на сумматор l{ - тр старших разряда преобразуемого двоичного числа..

На выходах первого преобразователя; образуются (п-4) результата суммирования, кратных 10, которые постугеют на вход второго яруса преобразователя и четыре младших разряда двоично-десятичного числа -(,2) 10°, 2, 10, поступающие на выход преобразователя. Младший разряд двоичного числа 2 в преобразовании не участвует.

Второй ярус преобразования состоит из (п-6)-тй сумматоров Ь На второго яруса преобразователя образуются (п-7) результатов суммирования, кратных 10 и четыре последующие разряда двоично-десятичного числа - (2 2 2) 10 2-10 и т.д.

Каждый сумматор 1 по модулю десять содержит шесть элементов И-НЕ 2-f7, анализируюиЬгх наличие двоичных эквивалентов преобразуемого числа на входах сумматора и три элемента ИЛИ-НЕ 8410, формирующих выходные сигналы, причем входы элементов И-НЕ

2,3, 4 и прямые входы элементов И-НЕ 5, 6, 7 являются входами, сумматора I модулю Десять , выходы элементов И-НЕ 2,

3,4 соединены с инверсными входами элементов И-НЕ 5, 6, 7,первый вход элемента . ЙЛИ-НЕ 8 соединен с инверсным входом элемента И-НЕ 2 и выходом И-НЕ 3, второй вход -- с вь1х6дом элемейта И-НЕ 2 и вторым инверсным входом элемента И-НЕ 7, входы элемента ИЛИ-НЕ 9 соединены с выходами элементов И-НЕ 2, б, 7, Входы элемента ИЛИ-НЕ 10 соединенны с выходами элементов И-НЁ 5, 7 и инверсным входом элемента И-НЕ 4. Выход элемента И-НЕ 7 и вщоды ИЛИ-НЕ 8, 9, 10 являются выходами сумматора 1 по модулю десять.

Вначале рассмотрим работу сумматора 1 при УСЛОВИИ, что кдлнчество разрядов преобразуемого числа П 10. , ,

Элемент И-НЕ 3 анализирует наличие 9-го (2) и 7-го (2) разрядов преобразуемого ДВОИЧНОГО чиЬлаГ, ,

Нри одновременном присутствии этих разрядов с выхода элемента И-НЕ поступает запрещающий потенШ1ал на инверсные входы элементов И-НЕ 2 и 6 и разрешающий потенциал на элемент ИЛИ-НЕ 8.

На выход Сумматора 1 по модулю десять с выхода элемента ИЛИ-НЕ 8 поступает сигнал, несущий значение . .

Элемент И-НЕ 2 р алИзирует наличие 9-го (2) и 8-го (2) разрядов преобразуемого двр1«ного числа. При Ойновременном наличии этих разрядов и отсутствии запрещающего потенииала с выхода элемента 3 (7-й разряд двоичного числа отсутствует) с выхода эяе мента Й-НЕ 2 поступает запрещающий потенциал на инверсный вход эл1е мента Й-НЕ 5 н разрешающие потенциалы на элементы ИЛИ-Н 8 и 9. . г ; . : - : На выход сумматора 1 по модулю десять с выходов элементов ИЛИ-НЕ 8 и 9 поступают сигналы, HecyuiHe значение 2 10 и 2. IlipH наличии только 8-го (2) разряда тоитото шс элемента И-МВ 2 постуйает разрёгоаюший пбтенциал да йнверсНЬ1Й вхой элемента И-НЕ 5. 8-й разряд двоич нрго .чйсл (2) через элемент 5 и элемент ЙШ-НЕ10 поступает иавьиодсуммШра 1 . Tib гл60утоодесять.; - . -J-:.--;/ s-Л-. .. -,/ При н йичйй тблько 7-го разряда двоичного числа (2) на инверсный вход элёМёгйа Й-НЕ 6 с, вьйсода эремеща 3 поступает разрйдающйй пменциал, 7-й разряд Двоичного ко да через элемент Й-fIE 6 и ИЛИ-НЕ 9 поступает нXiB6IXoд cj/MMaTOpa i по модуШ Десять.;;;: -I- .:V--- «: -- -При 1Ш1Йчий только 9-го (2) разряда двойчиого йюлй на йяверсиьге вхбды Й-ЙЕ 7 йоступают разрешающие потегрйаль С элёгл0йтЬв И-ЙЕ 2 и 4, koTopbie разрёпгают ||р(й:дУс)Р11е1Ше 9-го разряда через элемент 7 на х«зйь1 10. ; . В этом случае на вызсод койбинациощгрго сумматора 1 с вь1х6йов элементов ИЛИ-НЕ

Сочетания разрядов на йходй х

.-:::: ;,буйматорй- It--.---; -

512,256, 128

,256 /;,;;

512-128 ,

; 256,12 :

;128 .:;..

:25б . , ;-512. ; -

Соч;етанйя вЫходаых сигналов

сумматора li

6404-25 +2 -I640:fi28 f 2 /

640 ; ;;aS64-128 , 2 +2 ---.;

ji58;- -/2 ;. .;.. ;25б «2« ;

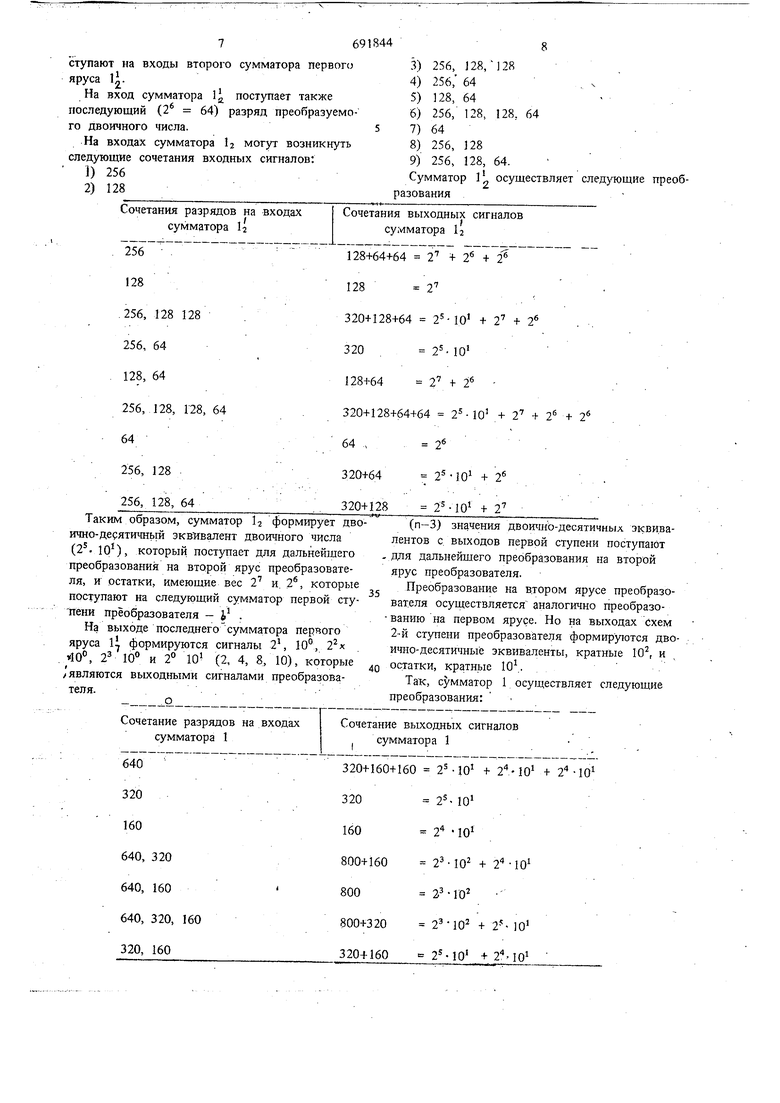

:256+l:28+l28 2 + 2 + 2 9, 10 и элемента И-НЕ 7 поступают сигналы, несущие значения 2, 2, 2 соответственно. Преобразование двоичного кода в двоичнодесятичный осуществляется следуюидим образом,; . . ; . ,. .-.-;, ,-. . Разряды преобразуемого двоичного числа поступают на сумматоры первого яруса преобразования. На 1-й сумматор первой ступени преобразования (li фиг 1) поступают 3 старших разрвда Преобразуемого двоичного числа. При п Ш эти разряды имеют йеса: 2 512, 256. -128. : .. ;..:,. л На быходё сумматора могут вбзникнуть : следующие сочетания поступающих на преобразование разрядо : 1)512; 256, 128 2)512, 256 3) 512, 128 :;. 4) 256, 128 t . .. . :5)128. /-;, ; , ..6) 256 / : . :,. .V.-: -1 7) 512 ; - : Г-::: :-.-..--.; Сумматор по мЬдулю десять осуществляет преобразование поступающих на еговход разрядов дбоич юго чисЯа в величину, кратную Ш, где а - номер яруса преобразователя. Образующиеся при этом Остатки имеют значения, равные весам последующих за Старшим разрядом двоичного числа. Сумматор 1J осуществляет следующие преобразования.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятичный | 1978 |

|

SU771659A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1277402A1 |

| Преобразователь последовательного двоичного кода в параллельный двоично-десятичный код | 1982 |

|

SU1084780A1 |

| Преобразователь двоично-десятичных чисел в коде 4,2,2,1 в двоичные | 1979 |

|

SU860055A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1977 |

|

SU690474A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1989 |

|

SU1667259A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1205137A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283979A1 |

| Преобразователь двоичных чисел в двоично-десятичные | 1978 |

|

SU779999A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1989 |

|

SU1662005A1 |

Таким образом, сумматор 1 формиг уёт Двоично-десятичный эквивалент двоичного чис ла (2 «10). Образующиеся при этом рстауки имеют веса: 2 и 2. ДвоичноЦасесятич ный эквивалент преобразуемого двоичного числа с выхода Сумматора 1 поступает для

i дальнейшего преобразования на второй ярус преобразователя, а образующиеся остатки поступают на входы второго сумматора первого яруса 1.

На вход сумматора 1 поступает также последующий (2 64) разряд преобразуемого двоичного числа.

На входах сумматора Ь могут возникнуть следующие сочетания входных сигналов; 1) 256

2) 128

Сочетания разрядов на входах

Сочетания выходных сигналов сумматора Ь 256,128 128 256,64 128,64 256,128, Г28 64 256,128 256,128, 64 Таким образом, сумматор Ь формирует дво ично-дедятичньш эквивалент двоичного числа (2. Ю ), который поступает для дальнейшего преобразования на второй ярус преобразователя, и остатки, имеющие вес 2 и. 2, которые поступают на следующий сумматор первой ступени преобразователя - i . На выходе последнего сумматора первого яруса 1 формируются сигналы 2, 10°, . 10°, 2 10° и 2° 10 (2, 4, 8, 10), которые /являются выходными сигналами преобразователя.

3)256, J28, 128

4)256, 64.4

5)128, 64

6)256/ 128, 128, 64

7)64

8)256, 28

9)256, 128, 64.

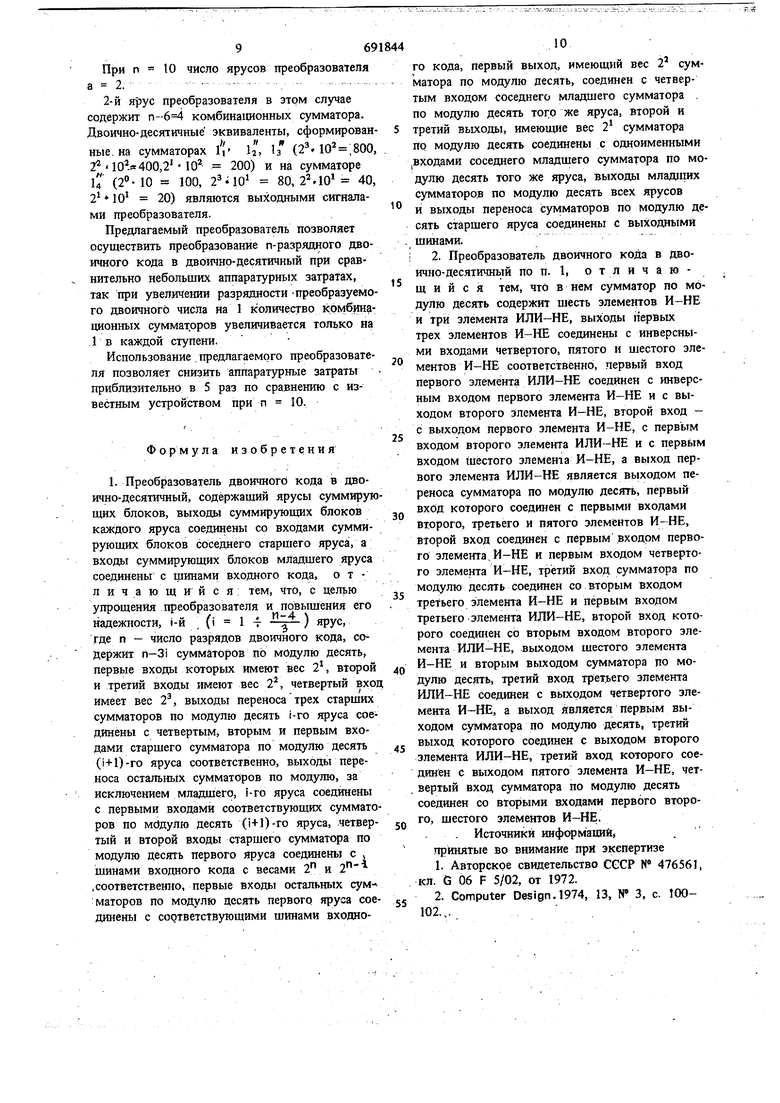

Сумматор 1 осуществляет следующие разования сумматора Ь 128+64+64 2 320+128+64 + 2 + 2 320 , 2-10 128+64 320+128+64+64 + 2 + 2 + 2 64 320+64 + 2 2-10 + 2 320+128 (п-3) значения двоичнО-десятичныА эквивалентов с выходов первой ступени поступают ДЛЯ дальнейшего преобразования на второй ярус преобразователя. Преобразование на втором ярусе преобразователя осуществляется аналогично преобразованию на первом ярусе. Но на выходах схем 2-й ступени преобразователя формируются двоично-десятичные эквиваленты, кратньш 10, и остатки, кратные 10, Так, сумматор 1 осуществляет следующие преобразования: 969 При n to число ярусов преобразователя а 2.- -- - 2-й ярус преобразователя в этом случае содержит комбинационных сумматора. Двоично-десятичные эквиваленты, сформирован ные. на сумматорах ij- l, Ь (2 10 ,800 .я400,2 10 - 200) и на сумматоре (2°-10 100, 80,22.10 40, 2 10 20) являются выходными сигналами преобразователя. Предлагаемый преобразователь позволяет осуществить преобразова1ше п-разрядного двоичного кода в двоично-десятичный при сравнительно небольших аппаратурных затратах, так при увеличе1ши разрядности преобразуемо го двоичного числа на 1 количество комбин ционных сумматоров увеличивается только на 1 в каждой ступени. Использование . предлагаемого преобразователя позволяет снизить аппаратурные затраты приблизительно в 5 раз по сравнению с известным устройством при п 10. Формула изобретения 1. Преобразователь двоичного кода в двоично-десятичный, содержащий ярусы суммирую щих блоков, выходы суммирующих блоков каждого яруса соединены со входами суммирующих блоков соседнего старщего яруса, а входы суммирующих блоков мЛадщего яруса соединены с шинами входного кода, отличающийся тем, что, с целью упрощения преобразователя и повышения его надежности, i-й (i 1 -f - - ) ярус, где п - число разрядов двоичного кода, содержит n-3i сумматоров по модулю десять, первые входы которых имеют вес 2, в1орой и третий входы имеют вес 2, четвертый вход имеет вес 2, выходы переноса трех старших сумматоров по модулю десять i-ro яруса соединены с четвертым, вторым и первым входами старщего сумматора по модулю десять (i+l)-ro яруса соответстветто, выходы переноса остальных сумматоров по модулю, за исключением младшего, i-ro яруса соединены с первыми входами соответствующих сумматоров по модулю десять (Н1)-го яруса, четвертый и второй входы старщего сумматора по модулю десять первого яруса соединены с , щинами входного кода с весами 2 и .соответственно, первые входы остальных сумматоров по модулю десять первого яруса соединены с соответствующими шинами входноГО кода, первый выход, имеющий вес 2 сумматора по модулю десять, соединен с четвертым входом соседнего младшего сумматора . по модулю десять того же яруса, второй и третий выходы, имеющие вес 2 сумматора по модулю десять соединены с одноименными .входами соседнего младшего сумматора по модулю десять того же яруса, выходы младлшх сумматоров по модулю десять всех ярусов и выходы переноса сумматоров по модулю десять старшего яруса соединены с выходными шинами. 2. Преобразователь двоичного кода в двоично-десятичньш по п. 1, отличающийся тем, что в нем сумматор по модулю десять содержит шесть элемеетов И-НЕ и три злемента ИЛИ-НЕ, выходы первых трех элементов И-НЕ соединены с инверсными входами четвертого, пятого и шестого элементов И-НЕ соответственно, первый вход первого элемента ИЛИ-НЕ соединен с инверсным входом первого элемента И-НЕ и с выходом второго элемента И-НЕ, второй вход с выходом первого элемента И-НЕ, с первым входом второго элемента ИЛИ-НЕ и с первым входом Шестого элемента И-НЕ, а выход первого элемента ИЛИ-НЕ является выходом переноса сумматора по модулю десять, первый вход которого соединен с первыми входами второго, третьего и пятого элементов И-НЕ, второй вход соединен с первым входом первого элемента, И-НЕ и первым входом четвертого элемента И-НЕ, третий вход сумматора по модулю десять соединен со вторым входом третьего элемента И-НЕ и первым входом третьего элемента ИЛИ-НЕ, BTOpoff вход которого соедю1ен со вторым входом второго элемента ИЛИ-НЕ, .выходом шестого элемента И-НЕ и вторым выходом сумматора по модулю десять, третий вход третьего элемента ИЛИ-НЕ соединен с выходом четвертого элемента И-НЕ, а выход является первым выходом сумматора по модулю десять, третий выход которого соединен с выходом второго элемента ИЛИ-НЕ, третий вход которого соединен с выходом пятого элемента И-НЕ, четвертый вход сумматора по модулю десять соединен со вторыми входами первого второго, шестого элементов И-НЕ. . Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР N 476561, кп. (3 06 F 5/02, от 1972. 2.Computer Design, 1974, 13, N 3, с. 100102.,.

n-j,n-i

2

п. г

,-

я-}

п-5 , 2 -W

п-ч , 2 -W

n-6 , 2 -W

-7 5n-S 2

г -w 2 -w

f w

2

Jr-fff

ii

.

/.//

/ n-6

2lO

4/2. Л

2

Авторы

Даты

1979-10-15—Публикация

1977-07-06—Подача