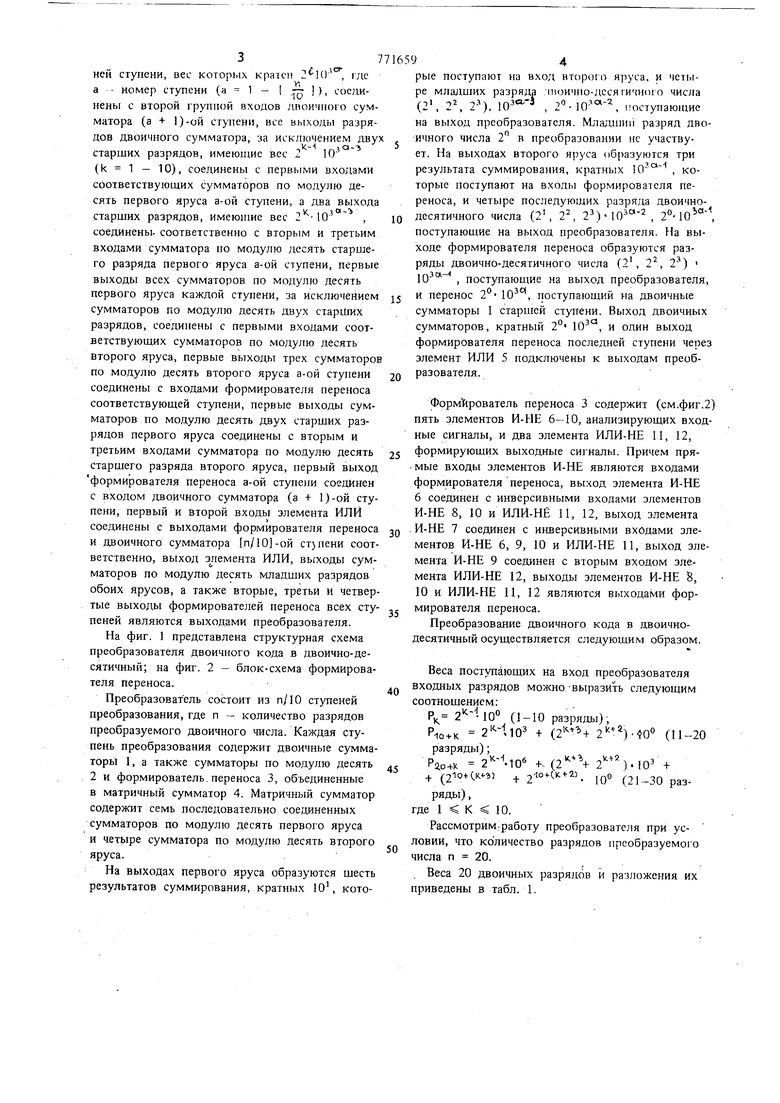

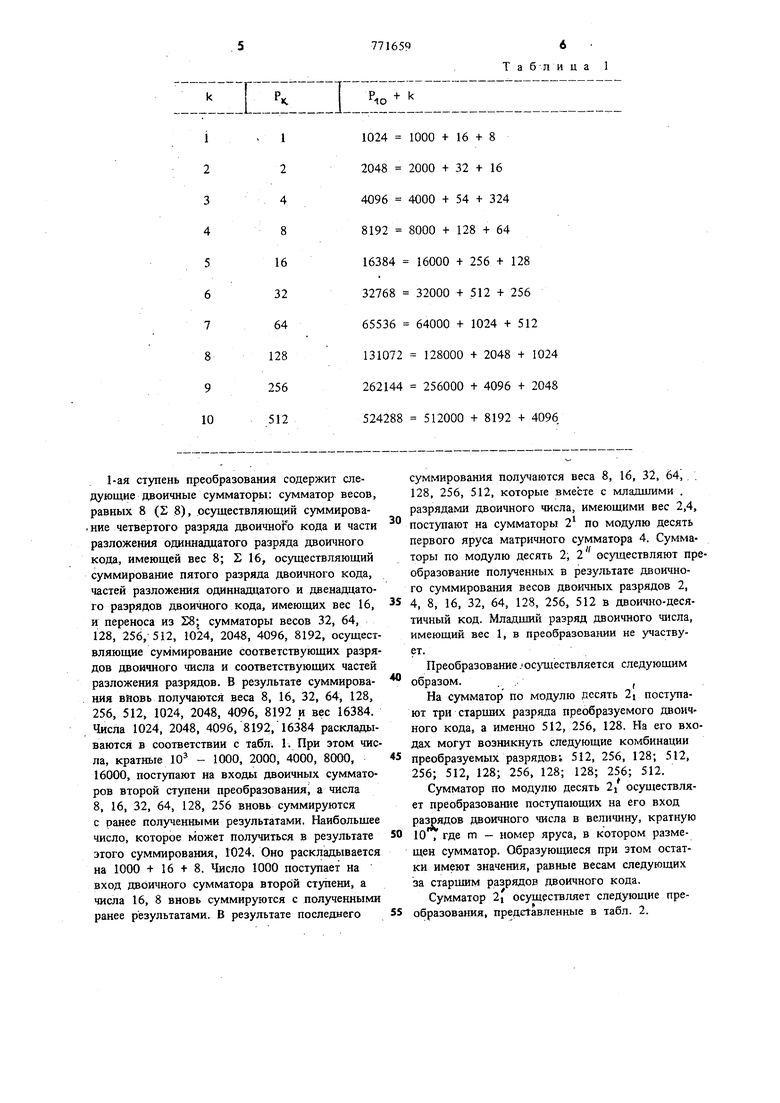

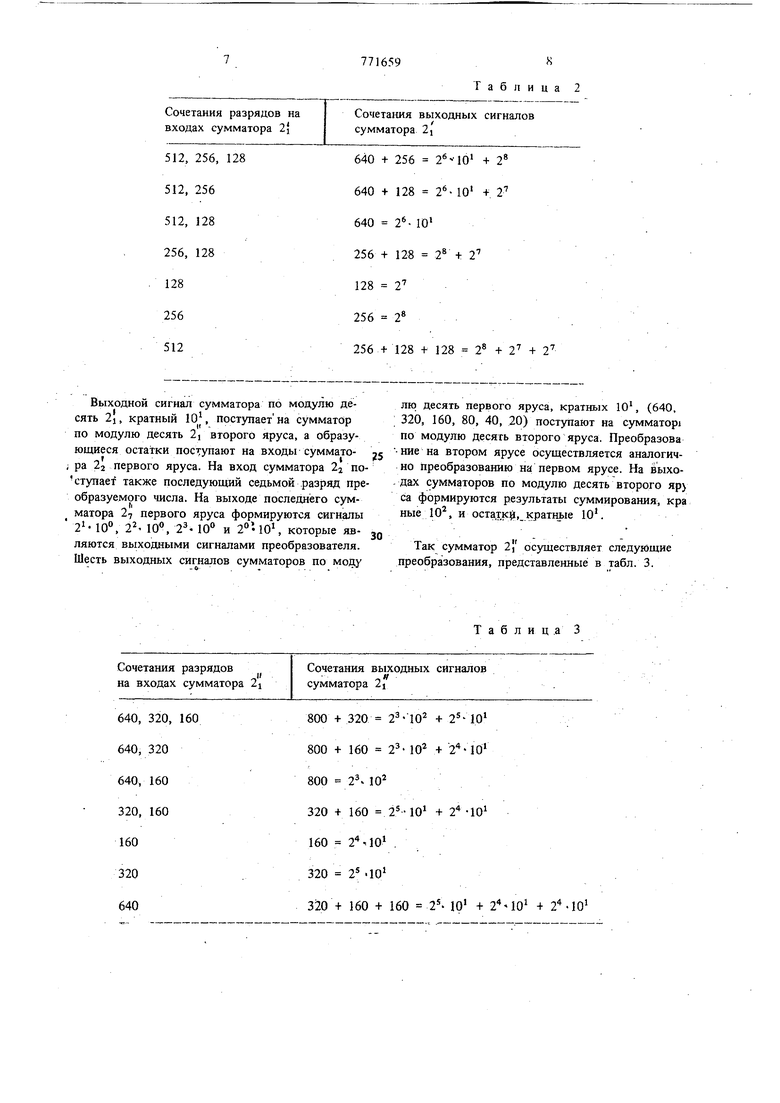

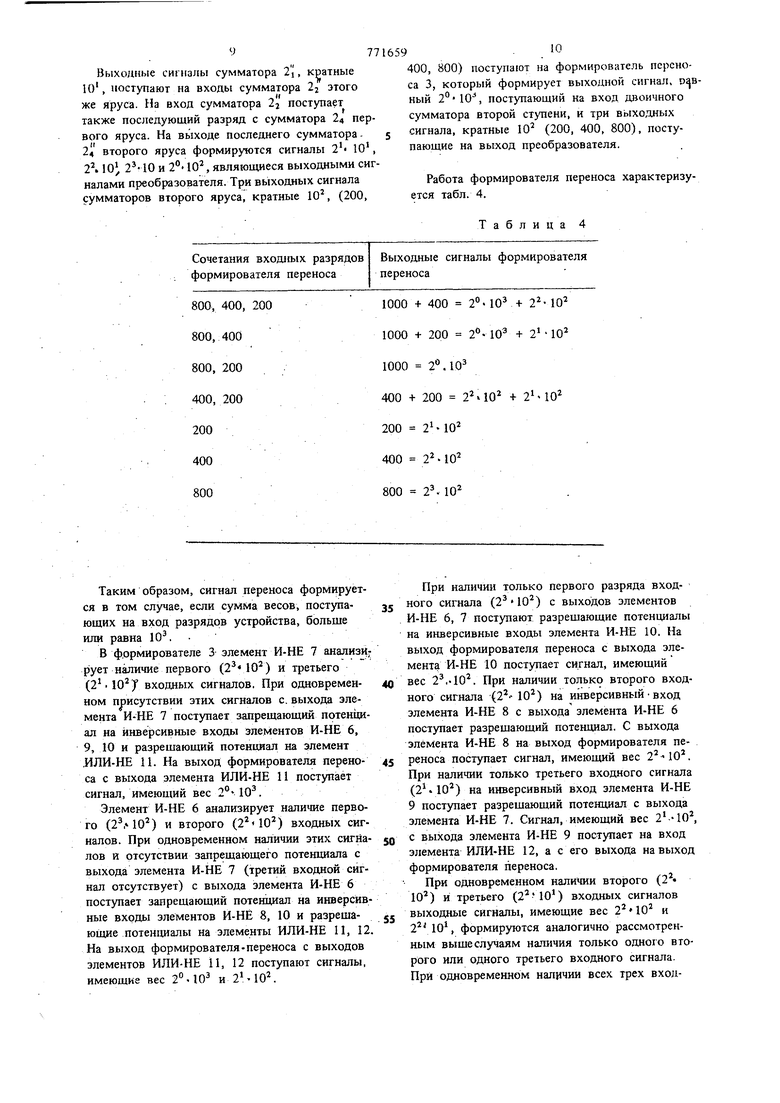

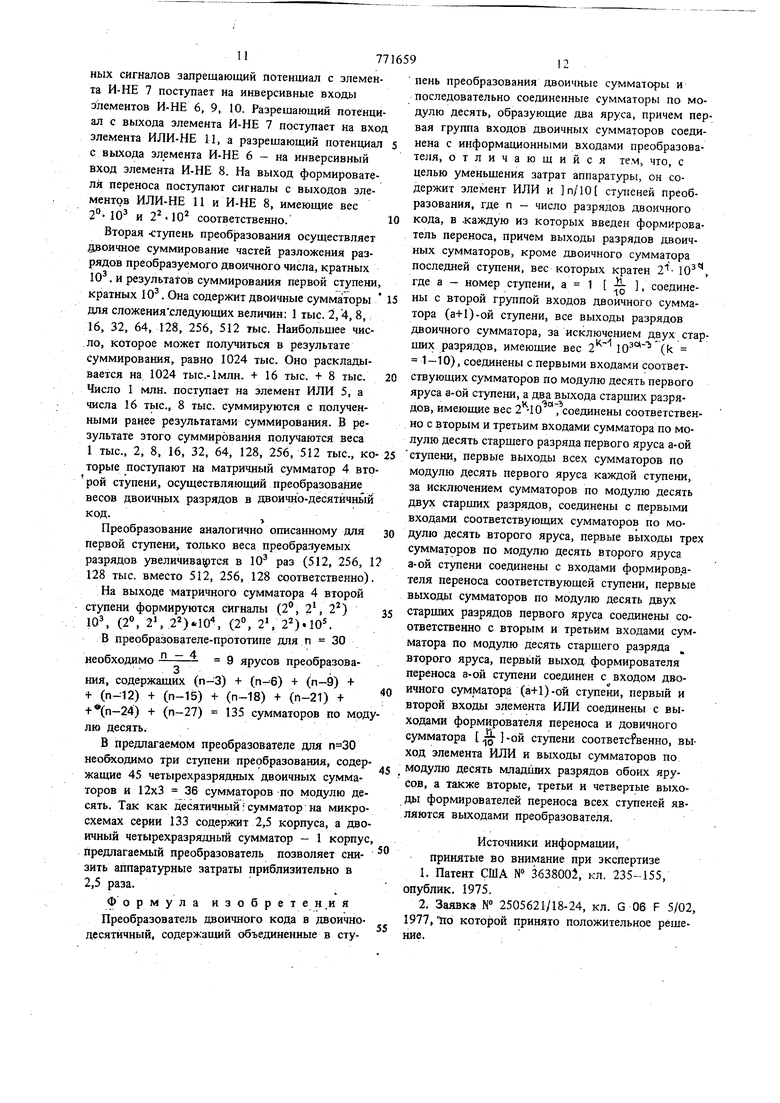

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при построении устройств для преобразования информации. Известен преобразователь двоишого кода в двоично-десятичный, содержащий ярусы последовательно соединенных сумматоров по модулю десять, причем выходы сумматоров пс модулю десять каждого яруса соединень с входами сумматоров по модулю десять соседнего яруса, а выходы сумматоров по модулю десять младшего яруса соединены с входами преобразователя 1 . Недостаток известного преобразователя состо ит в большом объеме оборудования и быстром его росте с увеличением разрядности преобразуемого кода. Наиболее близким по схемному решению и технической сущности к изобретению является преобразователь двоичного кода в двоичнодесятичный, содержаший двоичные сумма- : торы и последовательно соединенные сумматорь по модулю десять, образующие два яруса, причем первая группа входов двоичных су 5маторов соединена с входами преобразователя 2. Недостаток этого преобразователя состоит в большом объеме аппаратурь и низкой надежности. Целью изобретен1Ш является уменьшениз затрат аппаратуры и повышение надежности преобразователя. Это достигается за счет разбиения преобразователя на ряд ст511еней и специальной коммутацией входов и выходов сумматоров. Предлагаемый преобразователь двоичного кода в двоична-десятичный, содержащий объединенные в ступень преобразования двоичные сумматоры и последовательно соед1шенные сумматоры по . модулю десять, образующие два яруса, причем первая грут1па входов двоичных сумматоров соединена с информационными входами преобразователя, дополнительно содержит элемент ИЛИ и 1 п/10 ступеней преобразования, где п - число разрядов двоичного кода, в каждую из которых введен формирователь переноса, при этом выходы разрядов двоичных сумматоров, кроме двоичного сумматора послед37ней ступени, вес которых кратен () , i7ic а номер ступени (а 1 - | ), соединень с второй группой входов ппоичиого сумматора (а 1)-ой ступени, все выходы разрядов двоичного сумматора, за исключением двух старших разрядов, имеющие вес 2 10 (k 1 - 10), соединены с первыми входами соответствующих сумматоров по модулю десять первого яруса а-ой ступени, а два выхода старших разрядов, имеющие вес 2-10 , соединены, соответственно с вторым и третьим входами сумматора по модулю десять старшего разряда первого яруса а-ой ступени, первые выходы всех сумматоров по модулю десять первого яруса каждой ступени, за исключением сумматоров по модулю десять двух старших разрядов, соединены с первыми входами соответствующих сумматоров по модулю десять второго яруса, первые выходы трех сумматоров по модулю десять второго яруса а-ой ступени соединены с входами формирователя переноса соответствующей ступени, первые выходы сумматоров по модулю десять двух старших разрядов первого яруса соединены с вторым и третьим входами сумматора по модулю десять старшего разряда второго яруса, первый выход формирователя переноса а-ой ступени соединен с входом двоичного сумматора (а + 1)-ой ступени, первый и второй входы элемента ИЛИ соединены с выходами формирователя переноса и двоичного сумматора ст)пени соответственно, выход элемента ИЛИ, выходы сумматоров по модулю десять младших разрядов обоих ярусов, а также вторые, третьи и четвер тые выходы формирователей переноса всех сту пеней являются выходами преобразователя. На фиг. 1 представлена структурная схема преобразователя двоичного кода в двоично-десятичный; на фиг. 2 - блок-схема формирователя переноса. Преобразователь состоит из п/Ю ступеней преобразования, где п - количество разрядов преобразуемого двоичного числа. Каждая ступень преобразования содержит двоичные сумматоры 1, а также сумматоры по модулю десять 2 и формирователь, переноса 3, объединенные в матричный сумматор 4. Матричный сумматор содержит семь последовательно соединенных сумматоров по модулю десять первого яруса и четыре сумматора по модулю десять второго яруса. На выходах первого яруса образуются шесть результатов суммирования, кратных 10, кото4рые поступают на вход второго яруса, и четыре младших разряда ;111оичмо-дссятичнп1 о числа (2, 2 2-), , 2°-10 , поступающие на выход преобразователя. Младшии разряд двоичного числа 2 в преобразовании не участвует. На выходах второго яруса образуются три результата суммирования, кратных , которые поступают на входы формирователя переноса, и четыре последующих разряда двоичнодесятичного числа (2, 2 2), , поступающие на выход преобразователя. На выходе формирователя переноса образуются разряды двоично-десятичного числа (2, 2, 2) , поступающие на выход преобразователя, и перенос , поступающий на двоичнь е сумматоры 1 старшей ступени. Выход двоичных сумматоров, кратный 2° 10, и один выход формирователя переноса последней ступени через элемент ИЛИ 5 подключены к выходам преобразователя. ФормТйрователь переноса 3 содержит (см.фиг.2) пять элементов И-ЫЕ 6-10, анализирующих входные сигналы, и два элемента ИЛИ-НЕ 11, 12, формирующих выходные сигналы. Причем прямые входы элементов И-НЕ являются входами формировате.пя переноса, выход элемента И-НЕ 6 соединен с инверсивными входами элементов И-НЕ 8, 10 и ИЛИ-НЁ И, 12, выход элемента И-НЕ 7 соединен с инверсивными входами элементов И-НЕ 6, 9, 10 и ИЛИ-НЕ 11, выход элемента И-НЕ 9 соединен с вторым входом элемента ИЛИ-НЕ 12, выходы элементов И-НЕ 8, 10 и ИЛИ-НЕ И, 12 являются выходами формирователя переноса. Преобразование двоичного кода в двоичнодесятичный осуществляется следующим образом. Веса поступающих на вход преобразователя входных разрядов можно -выразить следующим соотнощением: Р 2 -10 (1-10 разряды); Р-10 + К гИюз + ( (11-20 разряды); PIO-.K .10 Н-.(.Ш Ч + (2 оНк-з) + . 10° (21-30 разряды) , где 1 К 10. Рассмотрим.-работу преобразователя при условии, что количество разрядов преобразуемого числа п 20. , Веса 20 двоичных разрядов и разложения их приведены в табл. 1.

1-ая ступень преобразования содержит следующие двоичные сумматоры: сумматор весов, равных 8 (2 8), осуществляющий суммирование четвертого разряда двоичного кода и части разложения одиннадцатого разряда двоичного кода, имеющей вес 8; Б 16, осуществляющий суммирование пятого разряда двоичного кода, частей разложения одиннадцатого и двенадцатого разрядов двоичного кода, имеющих вес 16, и переноса из 28; сумматоры весов 32, 64, 128, 256, 512, 1024, 2048, 4096, 8192, осуществляющие суммирование соответствующих разрядов двоичного числа и соответствующих частей разложения разрядов. В результате суммирования вновь получаются веса 8, 16, 32, 64, 128, 256, 512, 1024, 2048, 4096, 8192 и вес 16384. Числа 1024, 2048, 4096, 8192, 16384 раскладываются в соответствии с табл. 1. При этом числа, кратные 10 - 1000, 2000, 4000, 8000, 16000, поступают на входы двоичных сумматоров второй ступени преобразования, а числа 8, 16, 32, 64, 128, 256 вновь суммируются с ранее полученными результатами. Наибольшее число, которое может получиться в результате этого суммирования, 1024. Оно раскладывается на 1000 + 16 t 8. Число 1000 поступает на вход двоичного сумматора вторЬй ступени, а числа 16, 8 вновь суммируются с полученными ранее результатами. В результате последнего

суммирования пол чаются веса 8, 16, 32, 64, . 128, 256, 512, которые вместе с младшими . разрядами двоичного числа, имеющими вес 2,4,

поступают на сумматоры 2 по модулю десять первого яруса матричного сумматора 4. Сумматоры по модулю десять 2; 2 осуществляют преобразование полученных в результате двоичного суммирования весов двоичных разрядов 2,

4, 8, 16, 32, 64, 128, 256, 512 в двоично-десятичный код. Младший разряд двоичного числа, имеющий вес 1, в преобразовании не участвует.

Преобразование .осзществляется следующим

образом....J

На сумматор по модулю десять 2i поступают трн старших разряда преобразуемого двоичного кода, а именно 512, 256, 128. На его входах могут возникнуть следующие комбинации

преобразуемых разрядов; 512, 256, 128; 512, 256; 512, 128; 256, 128; 128; 256; 512.

Сумматор по модулю десять 2i осуществляет преобразование поступающих на его вход разрядов двоичного числа в величину, кратную

10 , где m - номер яруса, в котором размещен сумматор. Образующиеся при этом остатки имеют значения, равные весам следующих за старшим разрядов двоичного кода.

Сумматор 2i осуществляет следующие преобразования, представленные в табл. 2.

Сочетания разрядов на входах сумматора 2J

512, 256,

512, 256

512, 128

256, 128

128

256

512

Таблица

Сочетания выходных сигналов

/ сумматора 2j

640+ 256 + 2

640+ 128 10 - 2

640 10

256+ 128 2

128 2

256 2

256+ 128+ 128 2 + 2 +

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятичный | 1977 |

|

SU691844A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1277402A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1084779A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1977 |

|

SU690474A1 |

| Преобразователь последовательного двоичного кода в параллельный двоично-десятичный код | 1982 |

|

SU1084780A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1983 |

|

SU1095169A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1280702A1 |

| Преобразователь двоичного кода в двоично-десятично- шестидесятиричный код | 1982 |

|

SU1051529A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1989 |

|

SU1662005A1 |

| Преобразователь двоично-десятичных чисел в коде 4,2,2,1 в двоичные | 1979 |

|

SU860055A1 |

Выходной сигнал сумматора по модулю десять 2), кратный 10, поступаетна сумматор по модулю десять 2 второго яруса, а образующиеся остатки поступают на входы суммато- jj

; pa 22 первого яруса. На вход сумматора 22 поступает также последующий седьмой .разряд преобразуемого числа. На выходе последнего сумматора 2-J первого яруса формируются сигналы

2- 10 10, 2. 10° и 2° 10, которые яв- j ляются выходными сигналами преобразователя. Шесть выходных сигналов сумматоров по моду

лю десять первого яруса, кратных 10, (640, 320, 160, 80, 40, 20) поступают на сумматор по модулю десять второго яруса. Преобразова

ние на втором ярусе осуществляется аналогично Преобразованию на первом ярусе. На йыхо- дах сумматоров по модулю десять второго яр) са формируются результаты суммирования, кра ные 10. и оста,тк,кратнь1е Ю .

Так сумматор 2 осуществляет следующие преобразования, представленные в табл. 3.

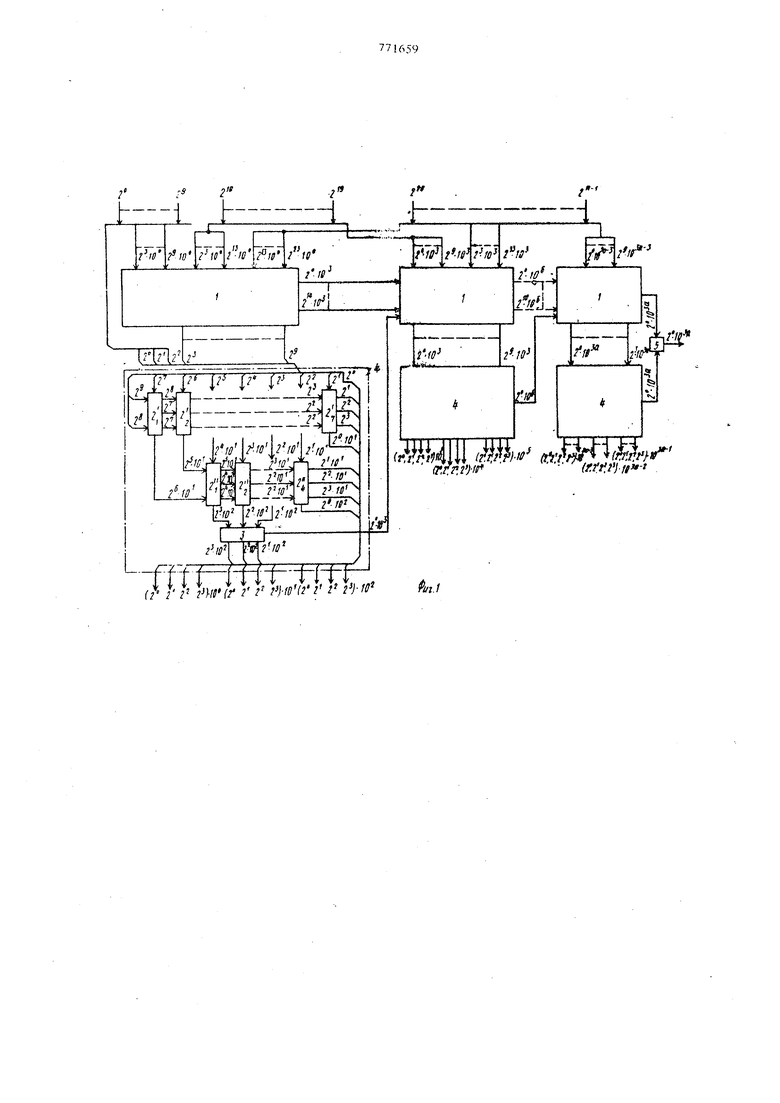

Таблица 3 Выходные сигналы сумматора 2i, кратные И), поступают на входы сумматора 2 этого же яруса. На вход сумматора 2i поступает также последующий разряд с сумматора 2 первого яруса. На выходе последнего сумматора24 второго яруса формируются сигналы 2« 10 , 2 0 2-10 и 2°-10, являющиеся выходными сигналами преобразователя. Три выходных сигнала сумматоров второго яруса, кратные 10, (200,

Сочетания входных разрядов формирователя переноса

800, 400, 200

800, 400

800, 200

400, 200

200

400

800

Таким образом, сигнал переноса формируется в том случае, если сумма весов, поступающих на вход разрядов устройства, больше или равна 10.

В ф.ормирователе 3-элемент И-НЕ 7 анализИг рует наличие первого () и третьего (2. входных сигналов. При одновременном присутствии этих сигналов с. выхода элемента И-НЕ 7 поступает запрещающий потенциал на инверсивные входы элементов И-НЕ 6, 9, 10 и разрещающий потенциал на элемент .ИЛИ-НЕ 11. На выход, формирователя переноса с выхода элемента ИЛИ-НЕ 11 поступает сигнал, имеющий вес 2 10.

Элемент И-НЕ 6 анализирует наличие первого (2л10) и второго () входных сигналов. При одновременном наличии этик скгналов и отсутствии запрещающего потенциала с выхода элемента И-НЕ 7 (третий входной сигнал отсутствует) с выхода элемента И-НЕ 6 поступает запрещающий потенциал на инверсивные входы элементов И-НЁ 8, 10 и разрешающие потенциалы на элементы ИЛИ-НЕ 11, 12 На выход формирователя-переноса с выходов элементов ИЛИ-НЕ II, 12 поступают сигналы, имеющие вес 2°.10 и 2-10

Выходные сигналы формирователя переноса

1000 + 400 2° 10

1000 + 200 2°- 10 + 2 -10

1000 2. 10

400 + 200 + 210

200 2-10

400 2 . 10

800 2 10

При наличии только первого разряда входного сигнала () с выходов элементов И-НЕ 6, 7 поступают разрешающие потенциалы на инверсивные входы элемента И-НЕ 10. На выход формирователя переноса с выхода элемента И-НЕ 10 поступает сигнал, имеющий вес 2,-10. При наличии только второго входного сигнала ( 10) на инверсивный вход элемента И-НЕ 8 с выхода элемента И-НЕ 6 поступает разрешающий потенциал. С выхода элемента И-НЕ 8 на выход формирователя переноса поступает сигнал, имеющий вес 210. При наличии только третьего входного сигнала (2. 10) на инверсивный вход элемента И-НЕ 9 поступает разрешающий потенциал с выхода элемента И-НЕ 7. Сигнал, имеющий вес 2 10 с выхода элемента И-НЕ 9 поступает на вход элемента ИЛИ-НЕ 12, а с его выхода на выход формирователя переноса.

При одновременном наличии второго (2 10) и третьего () входных сигналов выходные сигналы, имеющие вес 10 и 10, формируются аналогично рассмотренным выше случаям наличия только одного второго или одного третьего входного сигнала. При одновременном наличии всех трех вход400, 800) поступают на формирователь переноса 3, который формирует выходной сигнал, р вный 2°10, поступающий на вход двоичного сумматора второй ступени, и три выходных сигнала, кратные 10 (200, 400, 800), поступающие на выход преобразователя. Работа формирователя переноса характеризуется табл. 4. Таблица 4 ных сигналов запрещающий потенциал с элемен та И-НЕ 7 поступает на инверсивные входы элементов И-НЕ 6, 9, 10. Разрешающий потенци ал с выхода элемента И-НЕ 7 поступает на вхо элемента ИЛИ-НЕ 11, а разрещающий потенциал с выхода элемента И-НЕ 6 - на инверсивный вход элемента И-НЕ 8. На выход формирователя переноса поступают сигналы с выходов элементов ИЛИ-НЕ 11 и И-НЕ 8, имеющие вес 2°10 и 2.10 соответственно. Вторая -ступень преобразования осуществляет авоичное суммирование частей разложения разрядов преобразуемого двоичного числа, кратных 10. и результатов суммирования первой ступени кратных 10. Она содержит двоичные сумматоры для сложенияследуюших величин: 1 тыс. 2, 4, 8, 16, 32, 64, 128, 256, 512 тыс. Наибольщее число, которое может получиться в результате суммирования, равно 1024 тыс. Оно раскладывается на 1024 ТЫС.-1МЛН. + 16 тыс. + 8 тыс. Число 1 млн. поступает на элемент ИЛИ 5, а числа 16 ть1С., 8 тыс. суммируются с полученными ранее результатами суммирования. В результате этого суммирования получаются веса 1 тыс., 2, 8. 16, 32, 64, 128, 256, 512 тыс., ко торые поступают на матричный сумматор 4 вто рой ступени, осуществляющий преобразование весов двоичнь1х разрядов в двоично-десятйчньй код., Преобразование аналогично описанному для первой ступени, только веса преобразуемых разрядов увеличивается в 10 раз (512, 256, 1 128 тыс. вместо 512, 256, 128 соответственно). На выходе -матричного сумматора 4 второй ступени формируются сигналы (2, 2, 2) 10 (2«, 2, 22)10 (2°, 2S 2).10 В преобразователе-прототипе для п 30 необходимо 9 ярусов преобразова- 3 ния, содержащих (п-3) + (п--6) + (п-9) + + () + (п-15) + (п-18) + (п-21) + + (п-24) -(- (п-27) 135 сумматоров по мод лю десять. В предлагаемом преобразователе для необходимо три ступени преобразования, содержащие 45 четырехразрядных двоичных сумматоров и 12x3 36 сумматоров по модулю десять. Так как десятичный;сумматор:на микросхемах серии 133 содержит 2,5 корпуса, а дво ичный четырехразрядный сумматор - 1 корпус предлагаемый преобразователь позволяет снизить аппаратурные затраты приблизительно в 2,5 раза. Формула изобретен.и я Преобразователь двоичного кода в двоичнодесятичный, содержащий объединенные в ступень преобразования двоичные сумматоры и последовательно соединенньш сумматоры по модулю десять, образующие два яруса, причем первая группа входов двоичных сумматоров соединена с информационными входами преобразователя, отличающийся тем, что, с целью уменьщения затрат аппаратуры, он содержит элемент ИЛИ и п/10( ступеней преобразования, где п - число разрядов двоичного кода, в .каждую из которых введен формирователь переноса, причем выходы разрядов двоичных сумматоров, кроме двоичного сумматора последней ступени, вес которых кратен 10 , где а - номер ступени, а 1 ; , соединены с второй группой входов двоичного сумматора (а+1)-ой ступени, все выходы разрядов двоичного сумматора, за исключением двух старпшх разрядов, имеющие вес 2 (k 1-10), соединены с первыми входами соответствующих сумматоров по модулю десять первого яруса а-ой ступени, а два выхода старших разрядов, имеющие вес 2-10 , соединены соответственно с вторым и третьим входами сумматора по молулю десять старщего разряда первого яруса а-ой ступени, первые выходы всех сумматоров по модулю десять первого яруса каждой ступени, за исключением сумматоров по модулю десять двзХ старших разрядов, соединены с первыми входами соответствующих сумматоров по модулю десять второго яруса, первые выходы трех сумматоров по модулю десять второго яруса а-ой ст)шени соединены с входами формирователя переноса соответствующей ступени, первые выходы сумматоров по модулю десять двух старших разрядов первого яруса соединены соответственно с вторым и третьим входами сумматора по модулю десять старшего разряда второго яруса, первь1й выход формирователя переноса а-ой ступени соединен с входом двоичного сумматора (а+1)-ой ступени, первый и второй входы элемента ИЛИ соединены с выходами формирователя переноса и довичного сумматора .1-ой CTjoieHH соответс венно, выход элемента ИЛИ и выходы сумматоров по модулю десять младших разрядов обоих ярусов, а также вторые, третьи и четвертые выходы формирователей переноса всех ступеней являются выходами преобразователя. Источники информации, принятые во внимание при экспертизе 1,Патент США № 3638001, кл. 235-155, опублик. 1975. 2.Заявка Н° 2505621/18-24, кл. G 06 F 5/02, 1977, °по которой принято положительное рещение.

;

h-i h-

-d r fbsMwfi-M-W jMf/

I

-1

iz

. (ЖЖПда «//jH Sv -.y r«i.A. /.. л1| . . л (fff.lS-fiM-t (f,r.P.l)-4 .;./

Авторы

Даты

1980-10-15—Публикация

1978-07-11—Подача