цзиг.1

1

Изобретение относится к внчисли тельной технике и может быть исползовано в специализированных вычислителях.

Целью изобретения является повышние быстродействия за счет предварительного параллельного суммирования составляющих аргументов вектора.

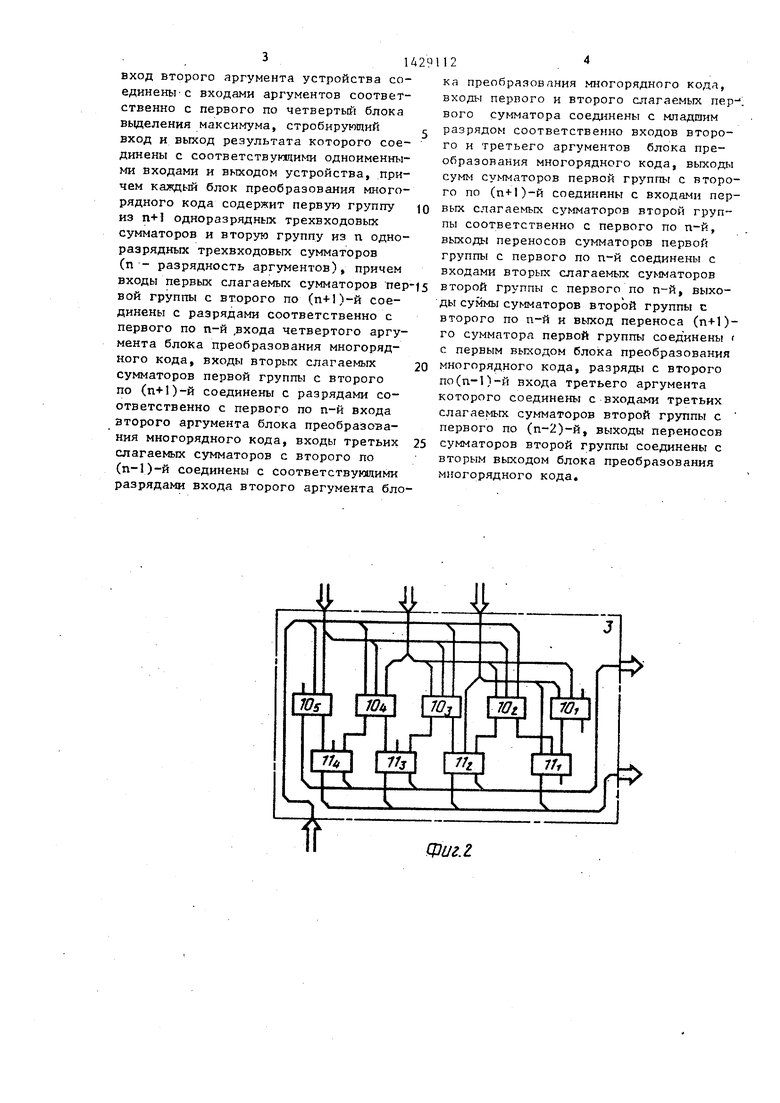

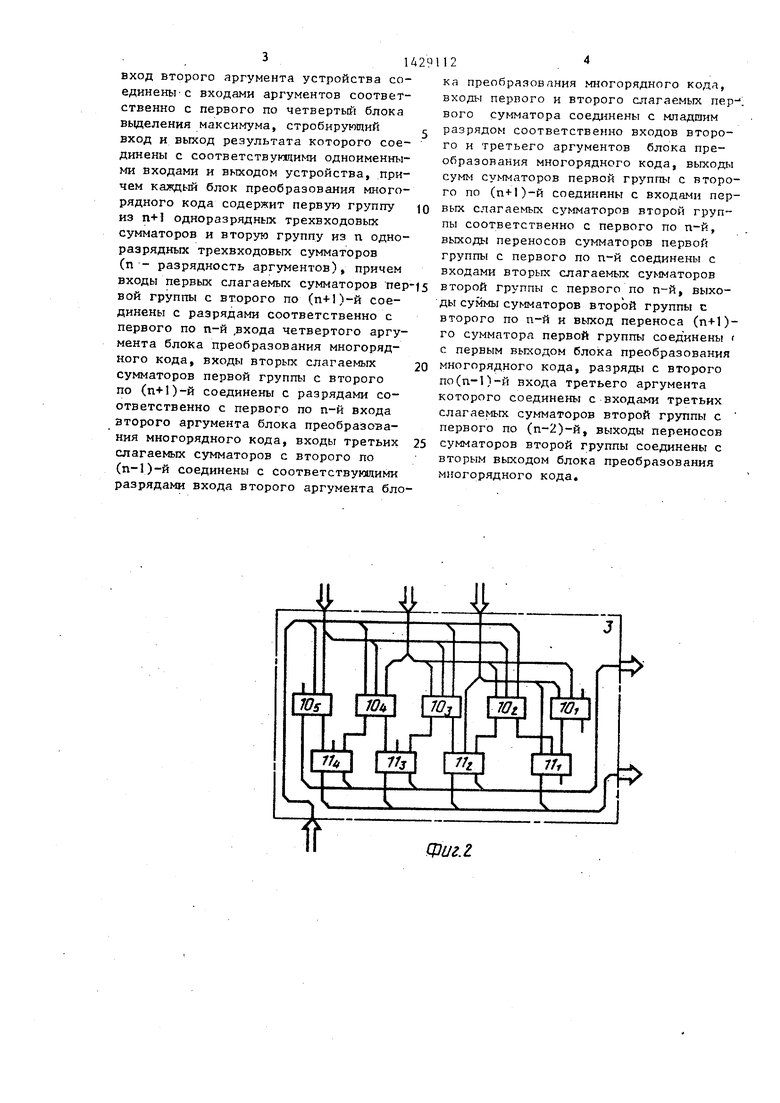

На фиго представлена структурна схема ycтpoйcтвa на фиг.2 - пример реализации-блока преобразования мнорядного кода при разрядности аргумента 4; на фиг.З - процесс преобразования кодов в блоке преобразовани многорядного кода.

Устройство содержит первый 1 и второй 2 сумматоры, первый 3 и второй А блоки преобразования многорядного кода, блок 5 выявления максимума, вход 6 первого аргумента, вход второго аргумента, выход 8 результата, стробирующий вход 9.

Влок преобразования многорядного кода содержит (п+1) одноразрядных

Трехвходовых сумматоров 10

, э«

.,10

первой группы и п одноразрядных

11

.Пп

трехвходовых сумматоров второй группы.

Устройство функционирует следующим Образом.

Устройство реализует следующую аппроксимирующую зависимость

У

макс г

lYf;

- /У/о I - I ,

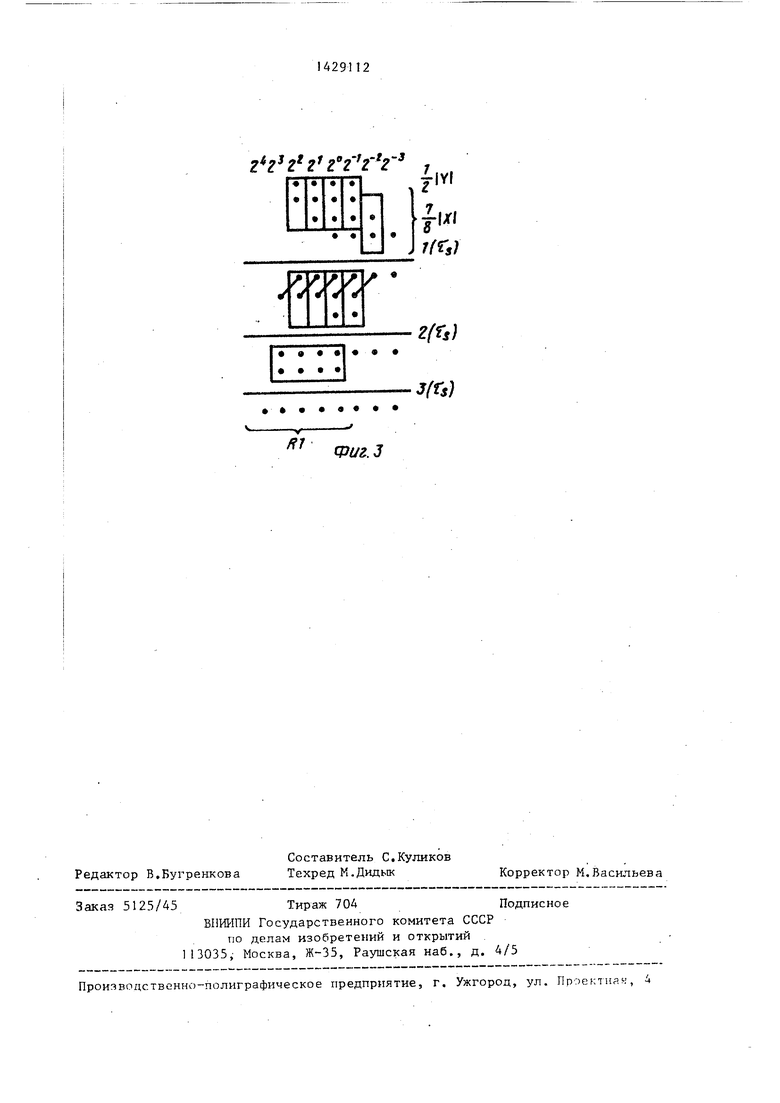

На входы первого и второго аргументов 6 и 7 поступают двоичные коды /X/. и /Y). На входы преобразователя 3 поступают коды /У //2, /Х//2, (Х//4, |Х//8, которые образуют четырехстрочную кодовую матршгу /КМ/ R1 /У//2 + + 7/XI/8.

Фиг.З иллюстрирует процесс преобразования КМ R1 с помощью первой группы сумматоров 10 до трехстрочной КМ за один такт работы одноразрядного сумматора и с помощью второй группы сумматоров 11 до двухстрочной КМ, которая первьш сумматором 1 преобразуется в однострочный, код результата за п тактов работы одноразрядного сумматора.

10

На фиг,3 точками обозначены двоичные разряды кодов соответствующего веса. Рамки окружамт разрядь, подаваемые на входы сумматоров. Номера шагов преобразования поставлены возле горизонтальных линий.

Аналогичным образом одновременно в блоке 4 преобразования многорядного кода и во втором сумматоре 2 формируется значение R2 /X//2 + I7/Y//8.

Значения |Xf, R1, R2, |Y/ записываются в регистры блока 5 выделения максимума и по сигналу, подаваемому на 15 стробирующий вход 9, производится сравнение, в результате чего на выходе 8 результата образуется значение функции .

20 Формула и.3 обретения

25

30

35

40

45

в +

п

55

Устройство для вычисления модуля вектора, содержащее блок вьщеления максим гма, два сумматора, отличающееся тем, что, с целью повьпаения быстродействия за счет предварительного параллельного суммирования аргументов, в него введены два блока преобразования многорядного кода, причем вход первого аргумента устройства соединен со сдвигом соответственно на один, два и три разряда в сторону младших разрядов с вхог дами первого, второго и третьего аргументов первого блока преобразования многорядного кода, вход второго аргумента устройства соединен со сдвигом соответственно на один, два и три разряда в сторону младших разрядов с входами первого, второго и третьего аргументов второго блока пре: образования многорядного кода, входы первого и второго аргументов устройства соединены со сдвигом на один разряд в сторону младпшх разрядов с входами четвертых аргументов соответственно первого и второго блоков преобразования многорядного кода, первый и второй выходы первого блока преобразования мно1 орядного кода соединены соответственно с входами первого и второго слагаемых первого сумматора, первый и второй выхощ; второго блока преобразования многорядного кода соединены с входами соответственно первого и второго слагаемых второго сумматора, выход первого сумматора, выход второго сумматора, вход первого аргумента устройства.

3U

вход второго аргумента устройства соединены -с входами аргументов соответственно с первого по четвертый блока вьщеления максимума, стробирумщий вход и выход результата которого соединены с соответствуквдими одноименными входами и выходом устройства, причем каждый блок преобразования многорядного кода содержит первую группу из п+1 одноразрядньк трехвходовых сумматоров и вторую группу из п одноразрядных трехвходовых сумматоров Сп - разрядность аргументов), причем входы первых слагаемых сумматоров пер вой группы с второго по (п-И)-й соединены с разрядами соответственно с первого по п-й .входа четвертого аргумента блока преобразования многорядного кода, входы вторых слагаемых сумматоров первой группы с второго по (п+1)-й соединены с разрядами соответственно с первого по п-й входа второго аргумента блока преобра:зова- ния многорядного кода, входы третьих слагаемых сумматоров с второго по (п-1)-й соединены с соответствуквдими разрядами входа второго аргумента бло12.

ка преобразования многорядного кода, входы первого и второго слагаемых первого сумматора соединены с младшим разрядом соответственно входов второго и третьего аргументов блока преобразования многорядного кода, выход, сумм сумматоров первой группы с второго по ()-й соединр.ны с входами первых слагаемых сумматоров второй группы соответственно с первого по п-й, выходы переносов сумматоров первой группы с первого по п-й соединены с входами вторых слагаемых сумматоров второй группы с первого по п-й, выходы суммы сумматоров второй группы с второго по п-й и выход переноса (п+1)- го сумматора первой группы соединены f с первым выходом блока преобразования многорядного кода, разряды с второго по(п-1)-й входа третьего аргумента которого соединены с входами третьих слагаемых сумматоров второй группы с первого по (п-2)-й, выходы переносов сумматоров второй группы соединены с вторым выходом блока преобразования многорядного кода.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления модуля вектора | 1989 |

|

SU1635182A1 |

| Устройство для вычисления модуля вектора | 1988 |

|

SU1559344A1 |

| Устройство для вычисления модуля комплексного числа | 1985 |

|

SU1305674A1 |

| Устройство для вычисления модуля вектора | 1988 |

|

SU1541602A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ МОДУЛЯ ВЕКТОРА | 1991 |

|

RU2022340C1 |

| Устройство для умножения | 1985 |

|

SU1322265A1 |

| Устройство для деления @ -разрядных чисел | 1984 |

|

SU1223224A1 |

| Устройство для умножения чисел | 1991 |

|

SU1797112A1 |

| Устройство для вычисления логарифма | 1979 |

|

SU783798A1 |

| Устройство для умножения | 1991 |

|

SU1803914A1 |

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислителях. Целью изобретения является повьш:ение быстродействия за счет предварительного параллельного суммирования составляющих аргументов вектора. Устройство содержит сумматоры 1,2, блоки преобразования многоразрядного кода 3,4,блок 5 выявления максимума, вход 6 первого аргумента, вход 7 второго -аргумента, выход 8 результата, стробирующий вход 9, Устройство реализует следующую аппроксимирующую зависимость: /X/ 7/8/Х/ + 1/2 /Y/ I/2/X/ + 7/8 /Y/ /У/ 4 X + Y макс 3 ил. о

rWi LS

W W

rP

-p

Фиг. 2

i LS

-p

Фиг. 2

eJ yt yt yOy-fa-ty-S

ffr

fPui.3

Авторы

Даты

1988-10-07—Публикация

1987-01-19—Подача