8

&0 4ь

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислителях..

Целью изобретения является сокращение аппаратурных затрат.

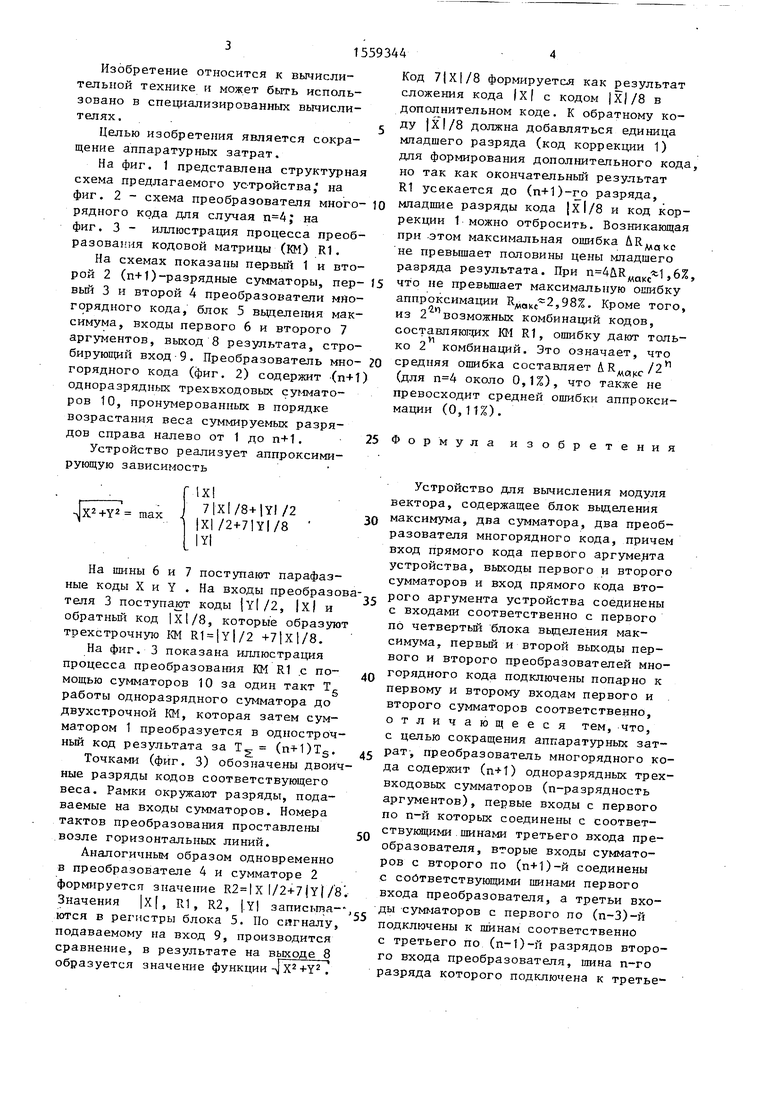

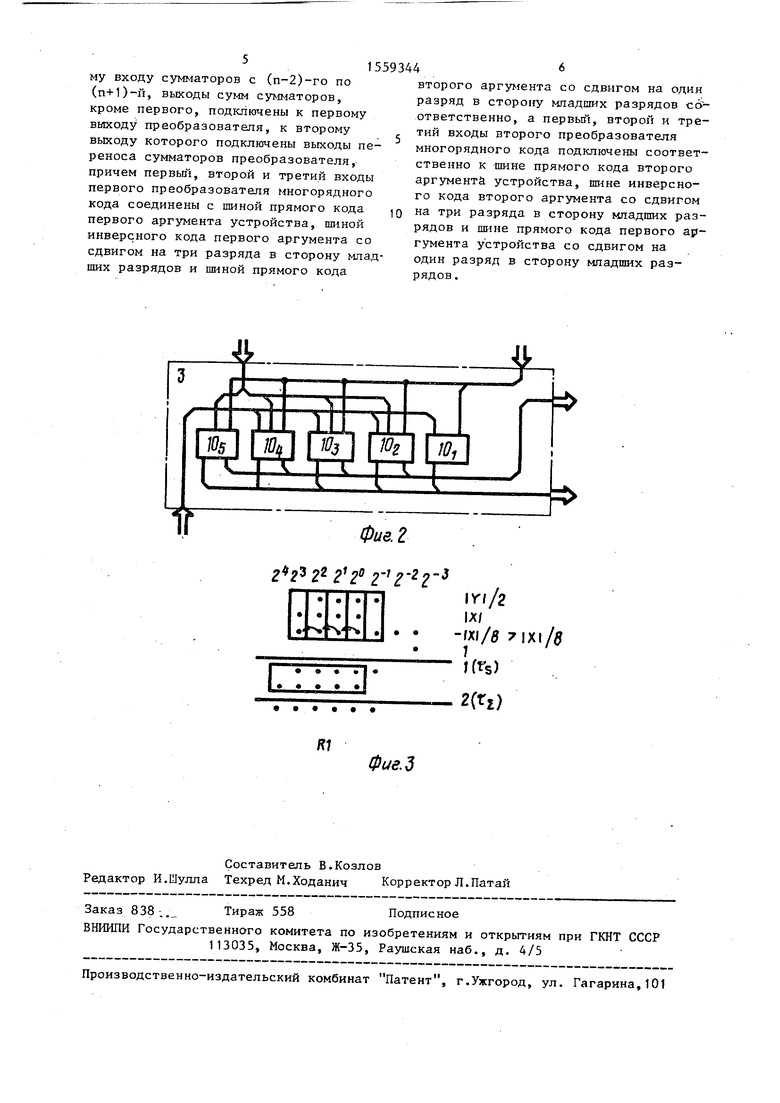

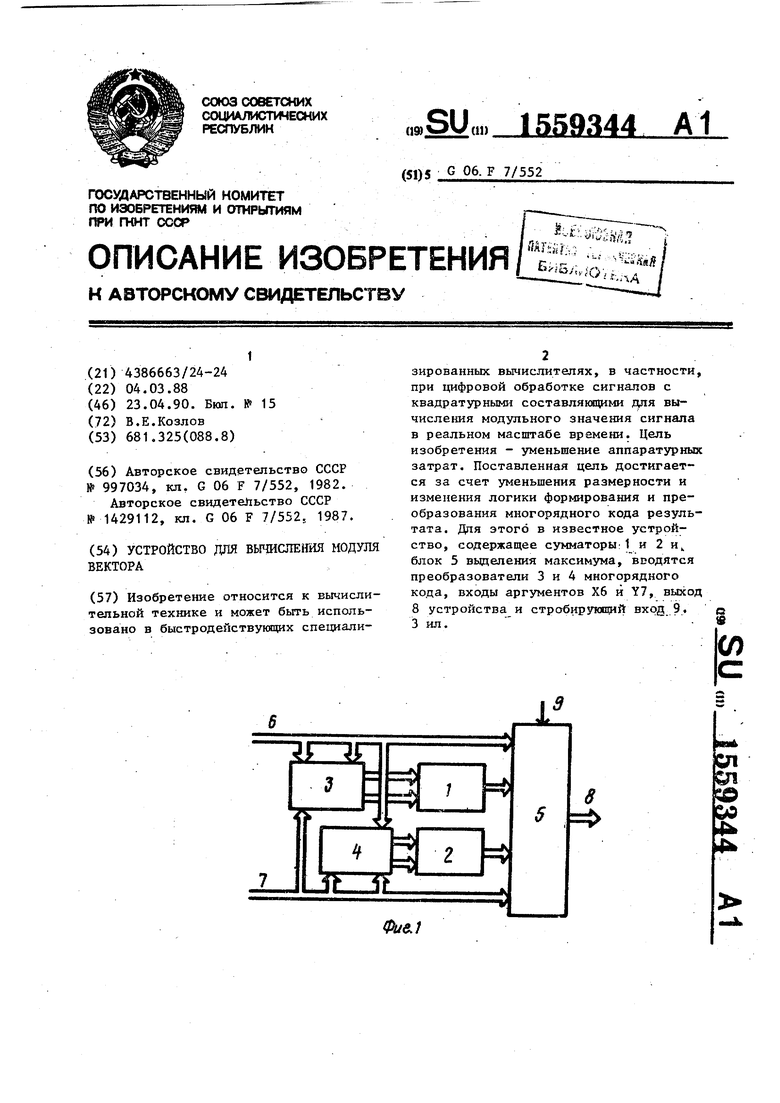

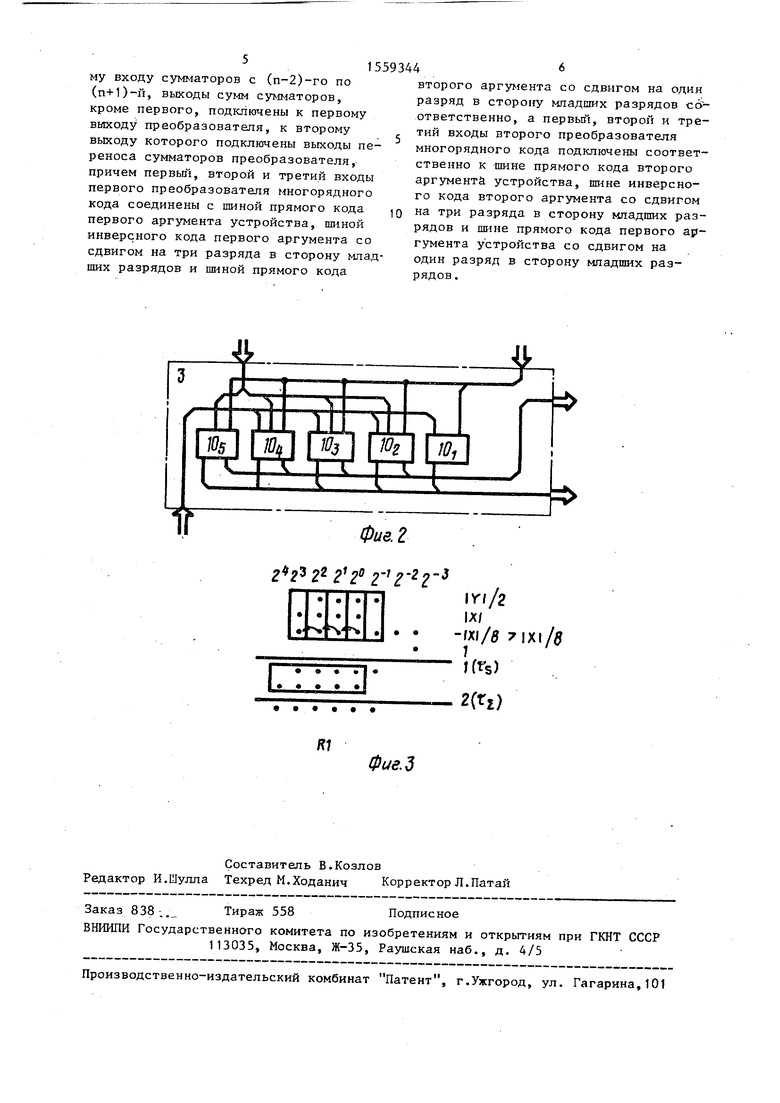

На фиг. 1 представлена структурная схема предлагаемого устройства, на фиг. 2 - схема преобразователя много- рядного кода для случая на фиг. 3 - иллюстрация процесса преобразования кодовой матрицы (KM) R1.

На схемах показаны первый 1 и второй 2 (п+1)-разрядные сумматоры, пер- вый 3 и второй 4 преобразователи многорядного кода, блок 5 выделения максимума, входы первого 6 и второго 7 аргументов, выход 8 результата, стро- бирующий вход 9. Преобразователь мно- горядного кода (фиг. 2) содержит (п+1 одноразрядных трехвходовых сумматоров 10, пронумерованных в порядке возрастания веса суммируемых разрядов справа налево от 1 до п+1.

Устройство реализует аппроксимирующую зависимость

IX

7|Xl/8+|Y /2 |X|/2+7|Y|/8

IYI

На шины 6 и 7 поступают парафаз- ные коды X и Y . На входы преобразователя 3 поступают коды , |х| и обратный код |Х|/8, которые образуют трехстрочную KM R1 |Y|/2 +7|Х|/8.

На фиг. 3 показана иллюстрация процесса преобразования KM R1 с по- мощью сумматоров 10 за один такт Tg работы одноразрядного сумматора до двухстрочной КМ, которая затем сумматором 1 преобразуется в однострочный код результата за Tg (n+1)Ts.

Точками (фиг. 3) обозначены двоичные разряды кодов соответствующего веса. Рамки окружают разряды, подаваемые на входы сумматоров. Номера тактов преобразования проставлены возле горизонтальных линий.

Аналогичным образом одновременно в преобразователе 4 и сумматоре 2 формируется значение X l/2+7|Y| /8 . Значения |Х, R1 , R2, |Y| записыла-- ются в регистры блока 5. По сигналу, подаваемому на вход 9, производится сравнение, в результате на выходе 8 образуется значение функции -J X2 +Y2 .

Код 7|Х|/8 формируется как результат сложения кода |Х| с кодом |Х|/8 в дополнительном коде. К обратному коду |Xl/8 должна добавляться единица младшего разряда (код коррекции 1) для формирования дополнительного кода но так как окончательный результат R1 усекается до (п+1)-гр разряда, младшие разряды кода |xl/8 и код коррекции 1 можно отбросить. Возникающая при -этом максимальная ошибка ARMaKC не превышает половины цены младшего разряда результата. При n 4uRMQKC 1,6% что не превышает максимальную ошибку аппроксимации RMa),98%. Кроме того, из 2 пвозможных комбинаций кодов, составлякицих KM R1, ошибку дают только 2 комбинаций. Это означает, что средняя ошибка составляет A RMCtKC /211 (для около 0,1%), что также не превосходит средней ошибки аппроксимации (0,11%).

Формула изобретения

0

5

Q45

,.

50

Устройство для вычисления модуля вектора, содержащее блок выделения максимума, два сумматора, два преобразователя многорядного кода, причем вход прямого кода первого аргумента устройства, выходы первого и второго сумматоров и вход прямого кода второго аргумента устройства соединены с входами соответственно с первого по четвертый блока выделения максимума, первый и второй выходы первого и второго преобразователей многорядного кода подключены попарно к первому и второму входам первого и второго сумматоров соответственно, отличающееся тем, что, с целью сокращения аппаратурных затрат-, преобразователь многорядного кода содержит (п+1) одноразрядных трехвходовых сумматоров (п-разрядность аргументов), первые входы с первого по n-й которых соединены с соответствующими шинами третьего входа преобразователя, вторые входы сумматоров с второго по (п+1)-и соединены с соответствующими шинами первого входа преобразователя, а третьи входы сумматоров с первого по (п-З)-й подключены к шинам соответственно с третьего по (п-1)-й разрядов второго входа преобразователя, шина п-го разряда которого подключена к третьему входу сумматоров с (п-2)-го по (п+1)-й, выходы сумм сумматоров, кроме первого, подключены к первому выходу преобразователя, к второму выходу которого подключены выходы переноса сумматоров преобразователя, причем первый, второй и третий входы первого преобразователя многорядного кода соединены с шиной прямого кода первого аргумента устройства, шиной инверсного кода первого аргумента со сдвигом на три разряда в сторону младших разрядов и шиной прямого кода

второго аргумента со сдвигом на один разряд в сторону младших разрядов соответственно, а первый, второй и третий входы второго преобразователя многорядного кода подключены соответственно к шине прямого кода второго аргумента устройства, шине инверсного кода второго аргумента со сдвигом на три разряда в сторону младших разрядов и шине прямого кода первого аргумента устройства со сдвигом на один разряд в сторону младших разрядов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления модуля вектора | 1989 |

|

SU1635182A1 |

| Устройство для вычисления модуля вектора | 1987 |

|

SU1429112A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ МОДУЛЯ ВЕКТОРА | 1991 |

|

RU2022340C1 |

| Устройство для вычисления модуля комплексного числа | 1985 |

|

SU1305674A1 |

| Арифметическое устройство | 1985 |

|

SU1305662A2 |

| Устройство для вычисления коэффициентов преобразования по Уолшу-Адамару | 1986 |

|

SU1361575A1 |

| Устройство для деления @ -разрядных чисел | 1984 |

|

SU1223224A1 |

| Цифровой функциональный преобразователь | 1981 |

|

SU1008735A1 |

| СПОСОБ СЛОЖЕНИЯ-ВЫЧИТАНИЯ ЧИСЕЛ, КОДИРУЕМЫХ СИГНАЛАМИ, И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1997 |

|

RU2109325C1 |

| Устройство для извлечения квадратного корня | 1988 |

|

SU1608652A1 |

Изобретение относится к вычислительной технике и может быть использовано в быстродействующих специализированных вычислителях, в частности при цифровой обработке сигналов с квадратурными составляющими для вычисления модульного значения сигнала в реальном масштабе времени. Цель изобретения - уменьшение аппаратурных затрат. Поставленная цель достигается за счет уменьшения размерности и изменения логики формирования и преобразования многорядного кода результата. Для этого в известное устройство, содержащее сумматоры 1 и 2 И блок 5 выделения максимума, вводятся преобразователи многорядного кода 3 и 4, входы аргументов X6 и Y7, выход 8 устройства и синхронизирующий вход 9. 3 ил.

Фиг. 2 г 2 222 2°

1

К1

т/2

1Л/

- XI/8 7JXI/5 7 Ifts)

2(2)

фиг.З

| Устройство для вычисления квадратного корня из суммы квадратов двух чисел | 1981 |

|

SU997034A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления модуля вектора | 1987 |

|

SU1429112A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-04-23—Публикация

1988-03-04—Подача