УС

4

СО

со ел vj

00

Изобрете} ие относится к вычисли- т&гЕьной технике и может быть использовано в процессорах ЭВМо

Цель изобретения - упрощение сум матора,.

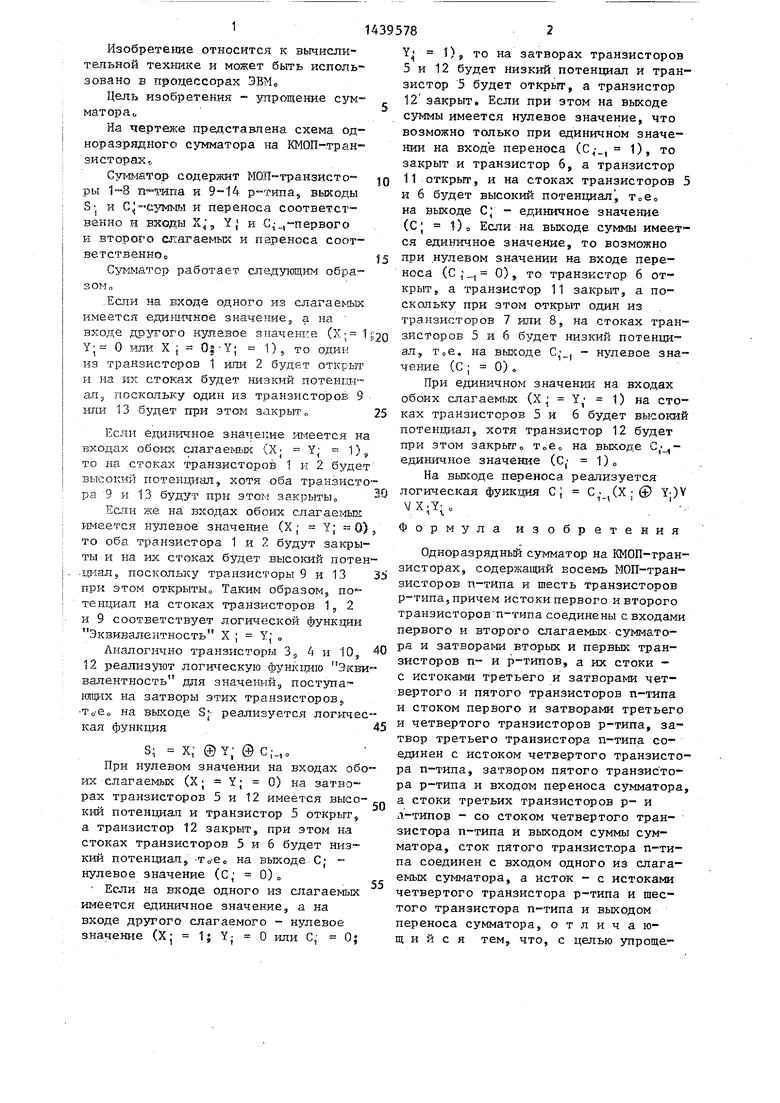

На чертеже представпена схема одноразрядного сумматора на КМОП-тран- зисторах-,

Су1 матор содержит МОП-транзисто ры 1--8 и 9-14 р-типа, выкоды S и С с ту1мы и переноса соответственно и вкоды X;, Y; и С,-,-первого к второго отагаемых и переноса соот ветственнОо

Сумматор работает следу101цим обра.Если на входе одного из слагаемых имеется еди ютное значение, а на

входе дрзтого нулевое значение (Х; 1 ;;2о зисторов 5 и 6 будет т1зкий потенциал, Тое, на выходе С,, - нулевое значение (с ; 0) ,

При единичном значении на входах обоих слагаемых (X Y,- 1) на сто- 25 ках транзисторов 5 и 6 будет высокий потенциал, хотя транзистор 12 будет при этом закрыто на выходе С, единичное значение (С,- 1)„

На выходе переноса реализуется логическая функция С) (Х,;@ Yj)Y

Y; О или X i 0|-Y; 1)., то одни из транзисторов 1 или 2 будет открыт и иа их стоках будет низкий потенпи™ ап;., поскольку один из транзисторов 9 или 13 будет при этом закрыт „

Если еди1 Р1чное значение имеется на входах o6oi-ibS cjiaraeMbix (X Yj 1) j. то на стоках транзисторов 1 и 2 будет высокий потенщ ал, хотя оба транзистора 9 и 13 будут при этом закрыты

Если же на входах обоих слагаемых 1-1меется нулевое значение (X; Y; 0) то оба транзистора 1 и 2 будут закрыты и на их стоках будет высокий потен- .цт-хал, поскольку транзисторы 9 и 13 3 при этом открыты Таким образом, потенциал на стоках транзисторов 1, 2 и 9 соответствует логической функции Эквивалентность X ; Y; ,

Аналогично транзисторы 3, 4 и 10, 40 12 реализуют логическую функцию Экви™ валентность для значенийд поступа- нтщх на затворы этих транзисторов., То ео на выходе S;- реализуется логическая функция45

S X,- ® Y; @ С;.,, При нулевом значении на входах обоих слагаемых (X; Y; 0) на затворах транзисторов 5 и 12 имеется высо кий потенциал и транзистор 5 открыг, а транзистор 12 закрыт, при этом на стоках транзисторов 5 и 6 будет низкий потенциал, на выходе С; - нулевое значение (С; 0)„

Если на входе одного из cJiaraeMisix имеется единичное значение, а на входе другого слагаемого - нулевое значение (Xj 1 YJ О или С,- 0;

50

55

V X УЧЛ 1 „

Формула изобретения

Одноразрядный сумматор на КМОП-тран- зисторах, содержащий восемь МОП-транзисторов п-типа и шесть транзисторов р-типа, причем истоки первого и второго транзисторов п-типа соединены с входами первого и второго слагаемых сумматора и затворами вторых и первых транзисторов п и р-типов, а юс стоки - с истоками третьего и затворами четвертого и пятого транзисторов п-типа и стоком первого и затворами третьего и четвертого транзисторов р-типа, затвор третьего транзистора п-типа соединен с истоком четвертого транзистора п-типа, затвором пятого транзис то- ра р-типа и входом переноса сумматора, а стоки третьих транзисторов р- и л-типо - со стоком четвертого транзистора п-типа и выходом суммы сумматора, сток пятого транзист.ора п-типа соединен с входом одного из слагаемых сумматора, а исток - с истоками четвертого транзистора р-типа и шестого транзистора п-типа и выходом переноса сумматора, о т л и ч а rent и и с я тем, что, с целью упроще

Y 1), то на затворах транзисторов 5 и 12 будет низкий потенциал и транзистор 5 будет открыт, а транзистор 12 закрыт. Если при этом на выходе суммы имеется нулевое значение, что возможно только при единичном значении на входе переноса (С,-, 1), то закрыт и транзистор 6, а транзистор 11 открыт, и на стоках транзисторов 5 и 6 будет высокий потенциал, на выходе С; - единичное значение (с I 1)., Если на выходе суммы имеется единичное значение, то возможно при нулевом значении на входе переноса (С,-, 0), то транзистор б открыт, а транзистор 11 закрыт, а поскольку при этом открыт один из транзисторов 7 или 8, на стоках тран

0 5

0

5

V X УЧЛ 1 „

Формула изобретения

Одноразрядный сумматор на КМОП-тран- зисторах, содержащий восемь МОП-транзисторов п-типа и шесть транзисторов р-типа, причем истоки первого и второго транзисторов п-типа соединены с входами первого и второго слагаемых сумматора и затворами вторых и первых транзисторов п и р-типов, а юс стоки - с истоками третьего и затворами четвертого и пятого транзисторов п-типа и стоком первого и затворами третьего и четвертого транзисторов р-типа, затвор третьего транзистора п-типа соединен с истоком четвертого транзистора п-типа, затвором пятого транзис то- ра р-типа и входом переноса сумматора, а стоки третьих транзисторов р- и л-типо - со стоком четвертого транзистора п-типа и выходом суммы сумматора, сток пятого транзист.ора п-типа соединен с входом одного из слагаемых сумматора, а исток - с истоками четвертого транзистора р-типа и шестого транзистора п-типа и выходом переноса сумматора, о т л и ч а rent и и с я тем, что, с целью упроще314395784

ния сумматора, затворы шестых транзис-торов п-гкпа и входами первого и втоторов п-типа и р-типа сЬедйнены с вы-рого слипаемых сумматора, истоки втоходом суммы сумматора, а исток шесто-рого, пятого и шестого транзисторов

го транзистора п-типа - со стоками р-типа соединены с шиной питания сумседьмого и восьмого транзисторов матора, а их стоки - с истоками перп-типа, истоки которых соединены свого, третьего и четвертого транзисзатворами восьмого и седьмого транзис-торов р-типа„

| название | год | авторы | номер документа |

|---|---|---|---|

| Одноразрядный сумматор | 1986 |

|

SU1432504A1 |

| Одноразрядный сумматор | 1987 |

|

SU1509874A1 |

| Узел формирования переноса в сумматоре | 1985 |

|

SU1287147A1 |

| Счетный триггер на КМОП-транзисторах | 1986 |

|

SU1398069A1 |

| Одноразрядный сумматор на МОП-транзисторах | 1986 |

|

SU1357945A1 |

| Комбинационный сумматор | 1987 |

|

SU1543399A1 |

| Комбинационный сумматор | 1988 |

|

SU1596321A1 |

| Комбинационный сумматор | 1987 |

|

SU1411737A1 |

| Одноразрядный двоичный сумматор | 1983 |

|

SU1149249A1 |

| Устройство для формирования группового переноса | 1985 |

|

SU1335981A1 |

Изобретение относится к вычислительной технике и может бьггь использовано в процессорах ЭВМ Цель изобретения - упрощение сумматора Одноразрядньй сумматор на КМОП-транзисто- рах содержит транзисторы 1-8 п-типа и 9-14 р-типа, истоки транзистора 1, 5, 7 и 2,8 соединены с входами первого и второго слагаемых и затворами транзисторов 2, 8, 13 и 1, 7, 9, стоки транзисторов 1, 2, 9 - с истоком транзистора 3 и затворами транзисторов 4, 5, 10, 11, затворами транзисторов 3, 12 и исток транзистора 4 - . с входом переноса, стоки транзисторов 3, 4, 10 -с выходом суммы и затворами транзисторов 6, 14, стоки транзисторов 5, 6, 11 - с выходом, переноса, а исток транзистора 6 - со стоками транзисторов 7, 8, истоки транзисторов 12, 13 и 14 соединены с шиной питания сумматора, а их стоки - с истоками транзисторов 10, 9, 11. 1 ил. (О (Л

| Букреев ИоН,, Мансуров В,М., Горячев В„Но Микроэлектронные схемы цифровых устройств, Советское радио, 1975, с 45, рис | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-11-23—Публикация

1987-05-27—Подача