114

Изобретение относится к вычислительной технике и может быть использовано в процессорах ЭВМ.

Цель изобретения - упрощение одноразрядного сумматора на МОП-транзисторах.

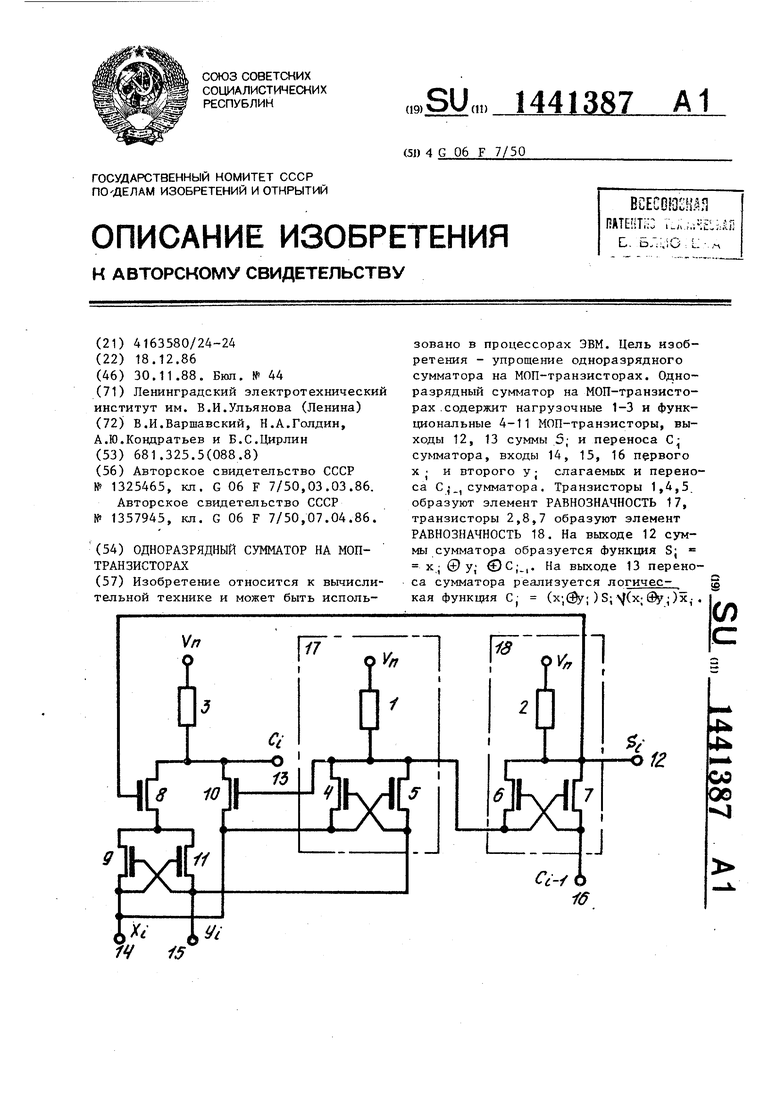

На чертеже представлена схема одноразрядного сумматора на МОП-транзисторах.

Одноразрядный сумматор на МОП- транзисторах содержит нагрузочные 1-3 и функдаональные 4-11 МОП тран- зисторы, выходы 12 и 13 суммы (S,-) и переноса (С;) соответственно и входы 14, 15 и 16 первого (х,-) и второго (у. ) слагаемых и переноса (С , ) соответственно. Транзисторы 4,5 и 1и6,7и2 образуют соответственно первый 17 и второй 18 элементы РАВНОЗНАЧНОСТЬ.

Сумматор работает следующим образом.

на выходе суммы имеется единичное значение (S , 1), что, очевидно, возможно только при нулевом значении на входе переноса (С 0), то транзистор 8 открыт, а поскольку при этом открыт и один из транзисторов 9 или 11, на затворе которого имеется единичное значение с входа одного из слагаемых, а стоке - нулевое значение с входа другого слагаемого, на выходе переноса будет нулевое значение (С- 0).

При единичном значении на входах обоих слагаемых (х; у;. 1) на стоках транзисторов 9,10 и 11 имеются единичные значения и такое же значение будет на выходе переноса (С 1).

На выходе переноса реализуется ло- гическая функция

С; (х; ®y;)S; Y (х; @ у,- )5; .

| название | год | авторы | номер документа |

|---|---|---|---|

| Одноразрядный сумматор на МОП-транзисторах | 1986 |

|

SU1357945A1 |

| Одноразрядный сумматор | 1986 |

|

SU1325465A1 |

| Одноразрядный сумматор | 1987 |

|

SU1432505A1 |

| Одноразрядный сумматор на МОП-транзисторах | 1986 |

|

SU1381490A1 |

| Одноразрядный сумматор | 1986 |

|

SU1432504A1 |

| Одноразрядный сумматор | 1987 |

|

SU1509874A1 |

| Одноразрядный сумматор на КМОП-транзисторах | 1987 |

|

SU1439578A1 |

| ОДНОРАЗРЯДНЫЙ СУММАТОР НА МОП ТРАНЗИСТОРАХ | 1996 |

|

RU2152641C1 |

| Комбинационный сумматор | 1987 |

|

SU1543399A1 |

| Комбинационный сумматор | 1988 |

|

SU1527630A1 |

Изобретение относится к вычислительной технике и может быть исполь/4 i5 зовано в процессорах ЭВМ. Цель изобретения - упрощение одноразрядного сумматора на МОП-транзисторах. Одноразрядный сумматор на МОП-транзисторах .содержит нагрузочные 1-3 и функциональные 4-11 МОП-транзисторы, выходы 12, 13 суммы 5; и переноса С- сумматора, входы 14, 15, 16 первого X j и второго у; слагаемых и переноса С ,, сумматора . Транзисторы 1,4,5. образуют элемент РАВНОЗНАЧНОСТЬ 17, транзисторы 2,8,7 образуют элемент РАВНОЗНАЧНОСТЬ 18. На выходе 12 суммы сумматора образуется функция S; Xj ©У; ©С;,. На выходе 13 переноса сумматора реализуется логичес-3 кая функция С| (х;(Эу; ) S; f(x; ЙУ)х,-. (Л 00 оо

Значения слагаемьк с входов х| и

yj- поступают на входы первого элемен та 17 РАВНОЗНАЧНОСТЬ, значение с выхода которого поступает на первый вход второго элемента 18 РАВНОЗНАЧНОСТЬ, на второй вход которого поступает значение переноса с входа С,, . |Таким-образом, на выходе второго элемента 18 РАВНОЗНАЧНОСТЬ, т.е. на на выходе Sj суммы, реализуется функ

ция

г,. - . /

S; X;

у; ® С;.,.

. При нулевом значении на входах обоих слагаемых (х- у; 0) на затворе транзистора 10 имеется единичное

значение с выхода первого элемента 17 РАВНОЗНАЧНОСТЬ, открьгаающее этот транзистор, а на выходе переноса - нулевое значение (С 0).

Если на входе одного из слагаемых имеется единичное значение, а на входе другого слагаемого - нулевое значение (х; 1, у О или х, О, У,; f) то на выходе первого элемента 17 РАВНОЗНАЧНОСТЬ имеется нулевое значение, которое, поступая на зат- вор тразистора 10, закрывает последний. Если при этом на выходе суммы имеется нулевое значение (S; 0), что,очевидно возможно только при единичном значении на входе переноса (С; . 1), то закрыт и транзистор 8, затвор которого соединен с выходом суммы, и на выходе переноса будет единичное значение (С; 1). Если же

входам х

Транзисторы 9 и 11 подключены к

и у. первого и второго слагаемых так же, как и транзисторы 4 и 5, образующие первый элемент 17 РАВНОЗНАЧНОСТЬ. Однако непосредственное подключение вькода первого эле- мента 17 РАВНОЗНАЧНОСТЬ к стоку транзистора 8 вместо транзисторов 9 и 11 недопустимо. При нулевых значениях на входах обоих слагаемых (х У 0) на выходе первого элемента 17 РАВНОЗНАЧНОСТЬ должно быть единичное

значение, а на выходе переноса - нулевое значение (С; 0), но при единичном значении на выходе суммы (S;

1) это нулевое значение с выхода

I

переноса через открытый транзистор

8 поступило бы на выход первого элемента 17 РАВНОЗНАЧНОСТЬ, что привело бы к искажению значения как на выходе первого элемента.17 РАВ- НОЗНАЧНОСТЬ, так и на выходе суммы и переноса.

Формула изобретения

Одноразрядный сумматор на МОП- транзисторах, содержащий два элемента РАВНОЗНАЧНОСТЬ, четыре функциональных транзистора и один нагрузочный транзистор, причем входы первого и второго слагаемых сумматора соединены соответственно с первым и вторы входами первого элемента РАВНОЗНАЧНОСТЬ, выход которого и вход переноса сумматора соединены соответст3144

венно с первым и вторым входами второго элемента РАВНОЗНАЧНОСТЬ, вькод которого соединен с выходом суммы сумматора и затвором первого функхдао- нального транзистора, сток которого соединен с истоком второго функционального транзистора, а исток - с выходом переноса сумматора и истоком третьего функционального транзистора, затвор и исток которого соединены соответственно с выходом первого элемента РАВНОЗНАЧНОСТЬ и входом пер74

вого слагаемого сумматора, а исток- со стЬком нагрузочного транзистора, исток которого соединен с шиной питания сумматора, отличающий- с я тем, что, с целью упрощения, истоки второго и четвертого функциональных транзисторов соединены между собой, а их затворы - со стоками четвертого и второго функциональных

транзисторов и входами соответственно первого и второго слагаемых сумматора.

| Одноразрядный сумматор | 1986 |

|

SU1325465A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Одноразрядный сумматор на МОП-транзисторах | 1986 |

|

SU1357945A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-11-30—Публикация

1986-12-18—Подача