Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах ЭВМ,

Целью изобретения является расширение функциональных возможностей за счет деления чисел переменного формата.

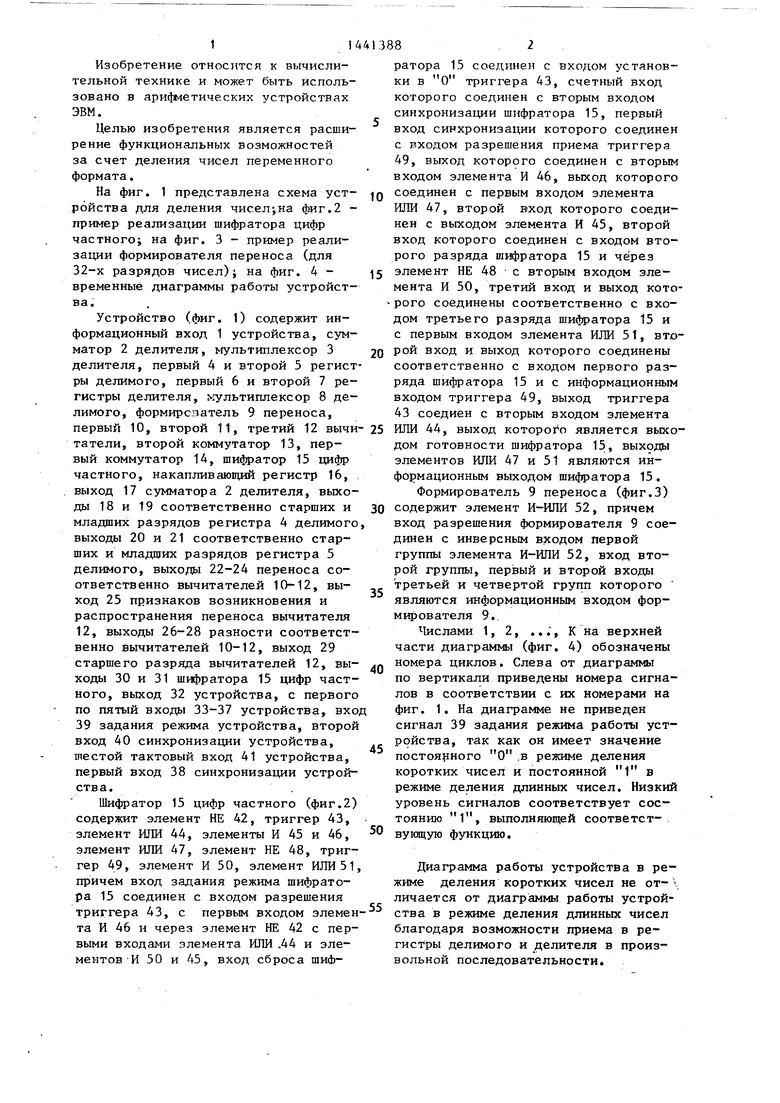

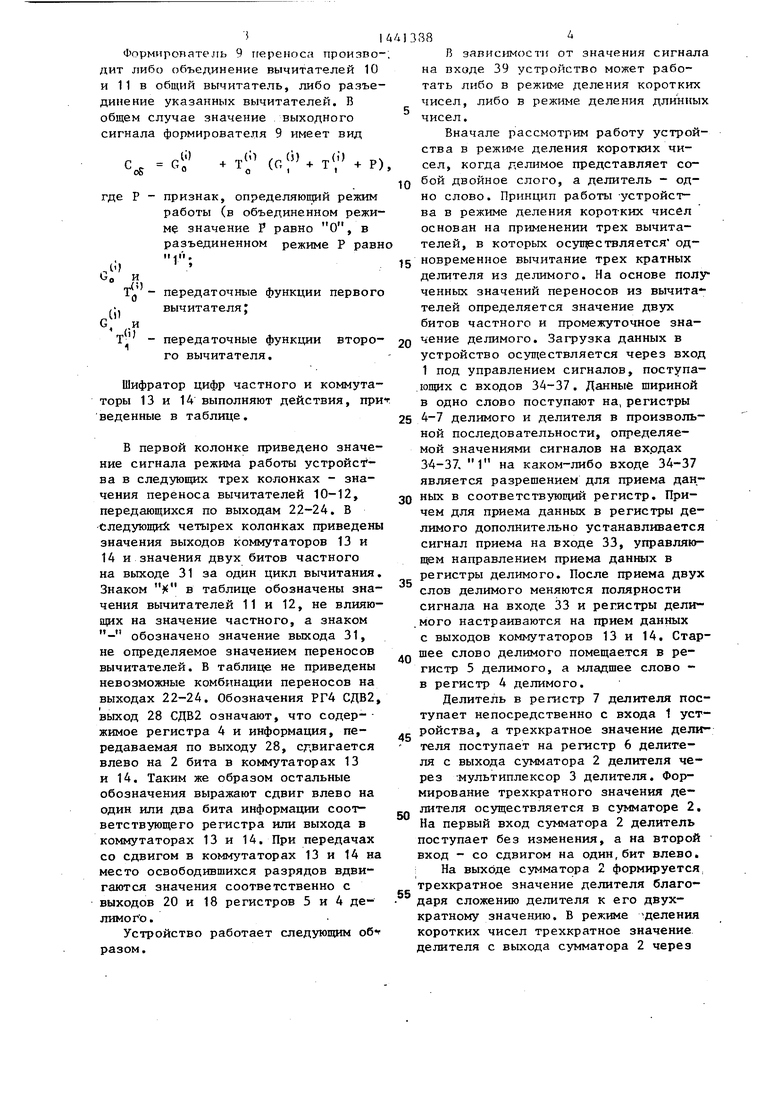

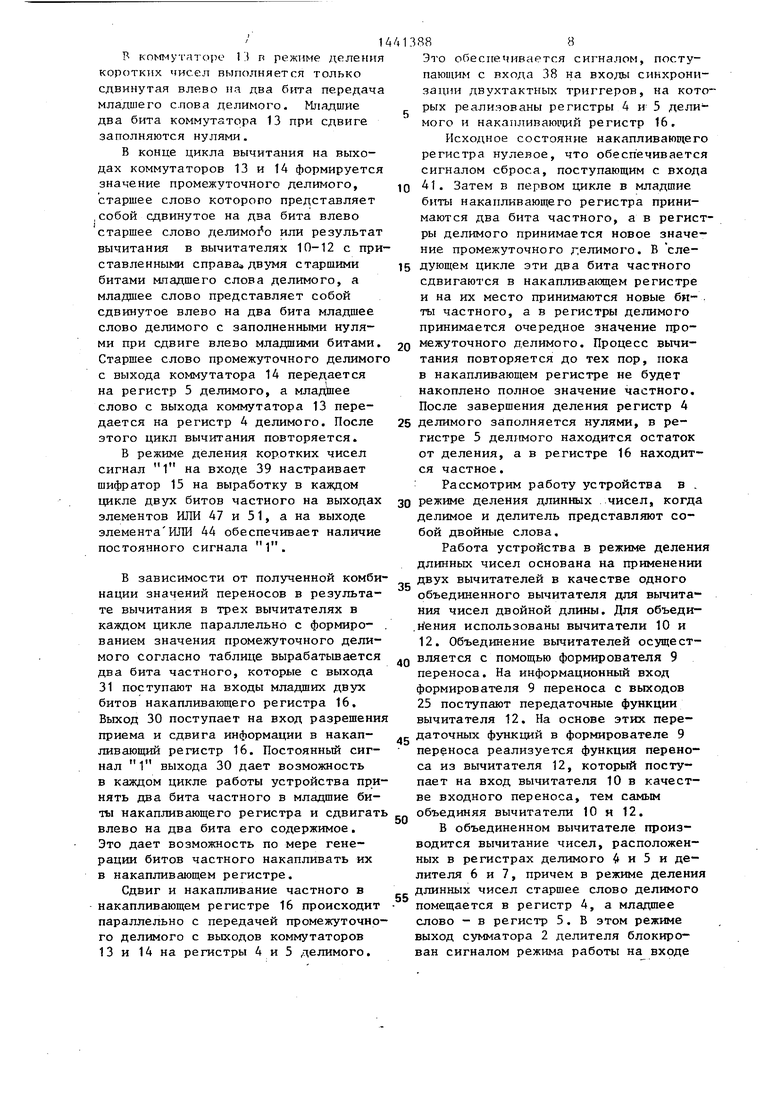

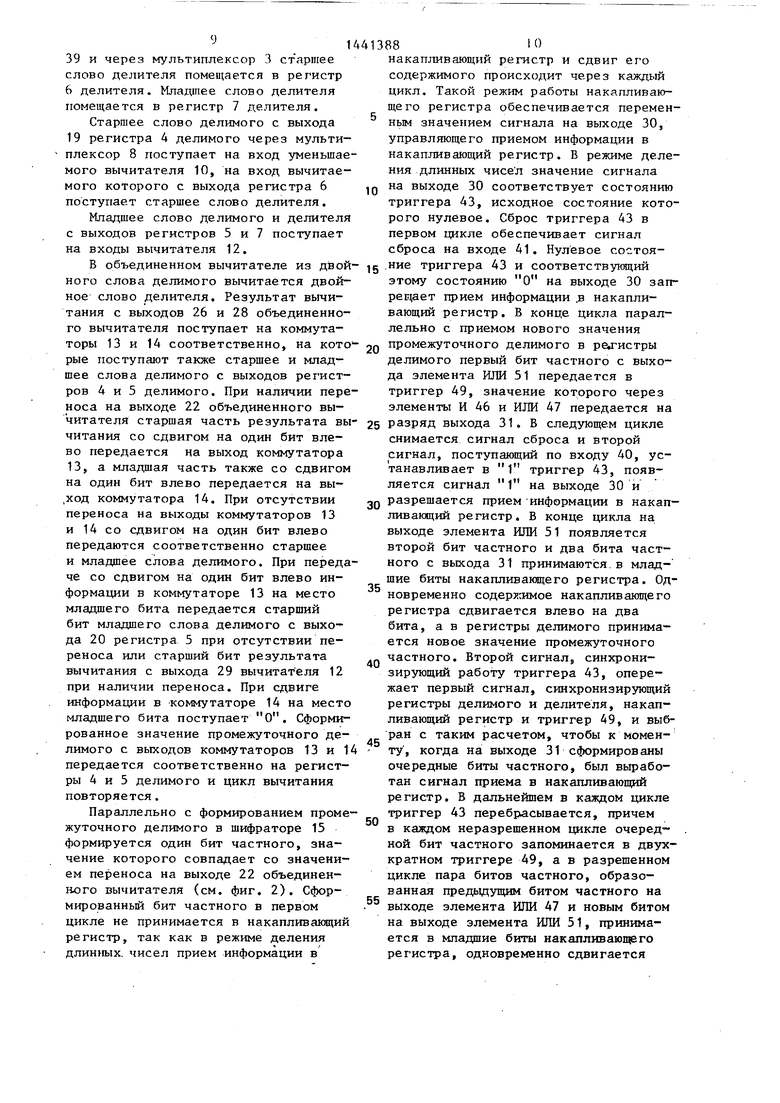

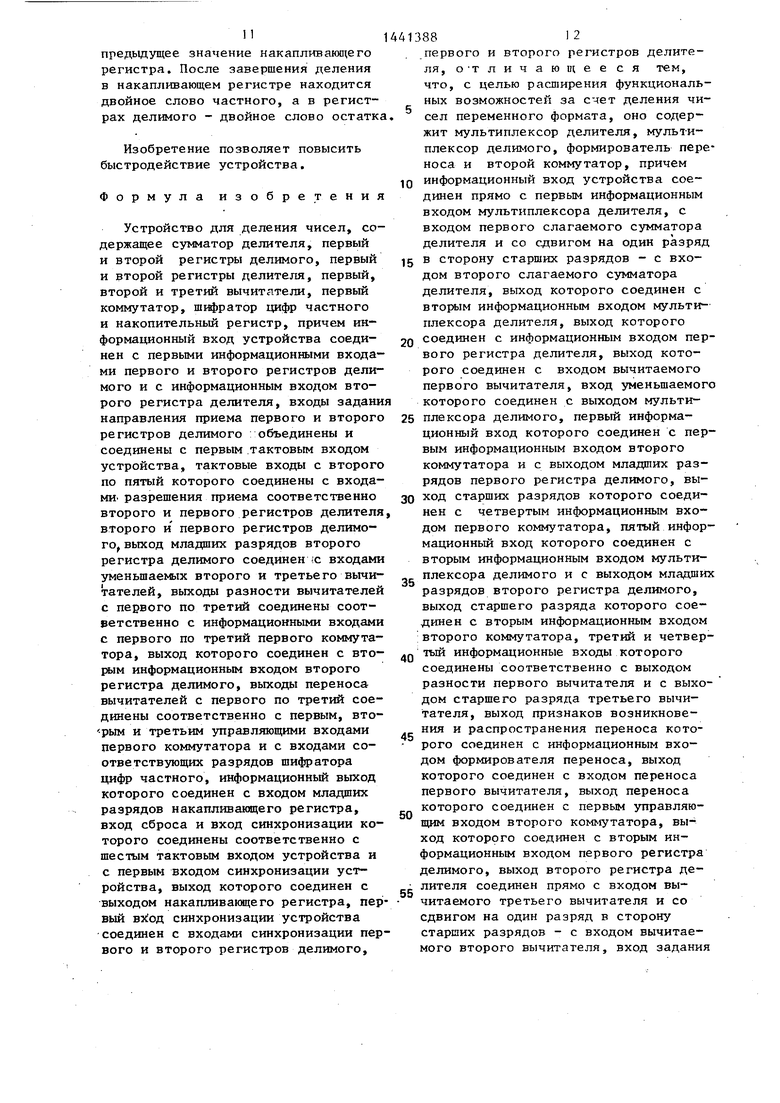

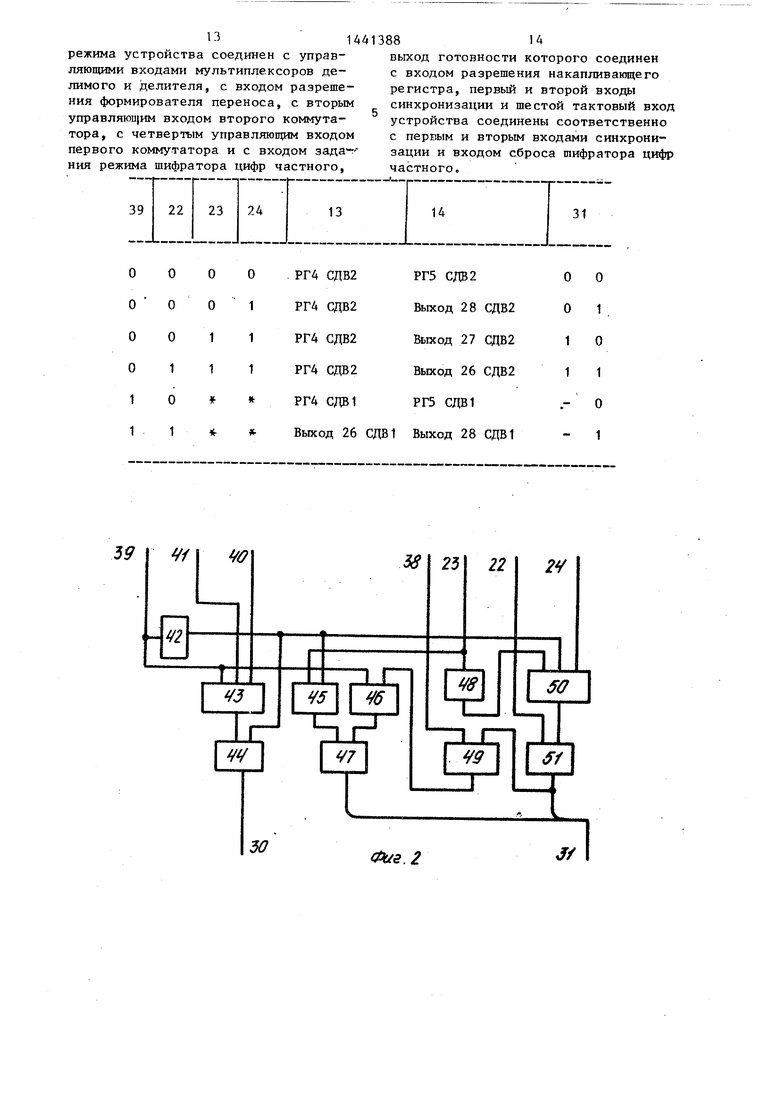

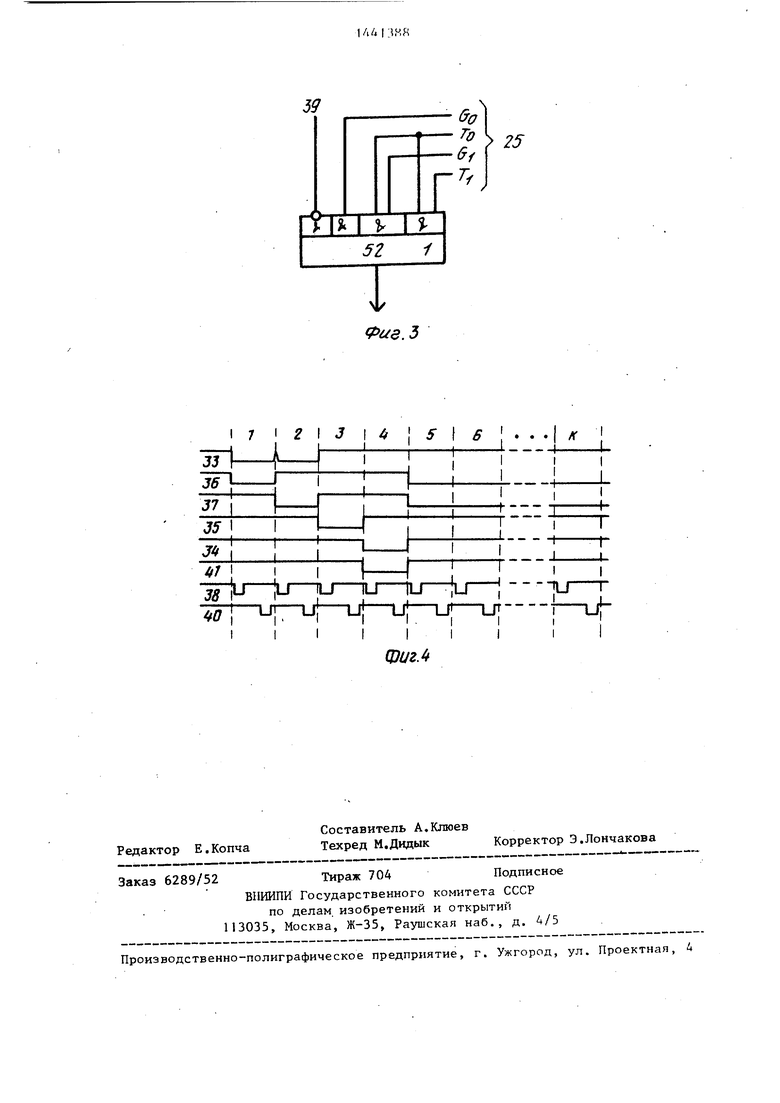

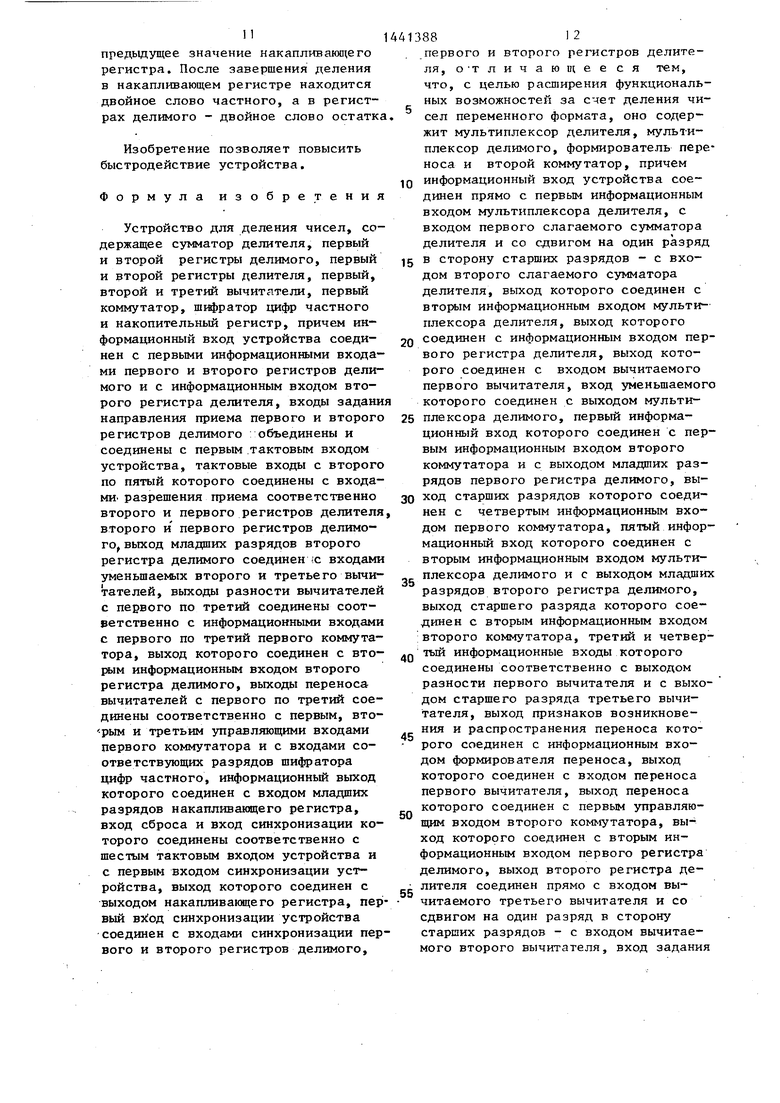

На фиг. 1 представлена схема устройства для деления чисел;на фиг.2 - пример реализации шифратора цифр частного; на фиг. 3 - пример реализации формирователя переноса (для 32-х разрядов чисел) на фиг. 4 - временные диаграммы работы устройства.

Устройство (фиг. 1) содержит информационный вход 1 устройства, сумматор 2 делителя, мультиплексор 3 делителя, первый 4 и второй 5 регистры делимого, первый 6 и второй 7 регистры делителя, мультиплексор 8 делимого, формирователь 9 переноса.

ратора 15 соединен с входом установки в О триггера 43, счетный вход которого соединен с вторым входом синхронизации шифратора 15, первый вход синхронизации которого соединен с входом разрешения приема триггера 49, выход которого соединен с вторым входом элемента И 46, выход которого

соединен с первым входом элемента ИЛИ 47, второй вход которого соединен с выходом элемента И 45, второй вход которого соединен с входом второго разряда ши|)ратора 15 и через элемент НЕ 48 -с вторым входом элемента И 50, третий вход и выход кото- рого соединены соответственно с входом третьего разряда шифратора 15 и с первым входом элемента ИЛИ 51, второй вход и выход которого соединены соответственно с входом первого разряда шифратора 15 и с информационным входом триггера 49, выход триггера 43 соедиен с вторым входом элемента

| название | год | авторы | номер документа |

|---|---|---|---|

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕЛИТЕЛЬ ТРОИЧНЫХ ЦЕЛЫХ ЧИСЕЛ | 2023 |

|

RU2810609C1 |

| Устройство для умножения | 1986 |

|

SU1432506A1 |

| Устройство для деления | 1990 |

|

SU1709352A1 |

| Устройство для деления | 1989 |

|

SU1619255A1 |

| Устройство для деления | 1984 |

|

SU1249551A1 |

| Устройство для деления чисел | 1981 |

|

SU1119006A1 |

| Устройство для деления | 1989 |

|

SU1767497A1 |

| Устройство для деления десятичных чисел | 1990 |

|

SU1774328A1 |

| Устройство для деления | 1990 |

|

SU1783521A1 |

| Устройство для деления | 1985 |

|

SU1282117A1 |

Изобретение относится к вычислительной Технике и может быть использовано в арифметических устройствах ЭВМ. Цель изобретения - расширение функциональных возможностей за счет деления чисел переменного формата. Поставленная цель достигается тем, что устройство для деления чисел, содержащее сумматор 2 делителя, регистры 4, 5 делимого, регистры 6, 7 делителя, вычитатели 10- 12,коммутатор 14,шифратор 15 цифр частного и накапливающий регистр 16,содержит мультиплексор 3 делителя,мультиплексор 8 делителя, формирователь 9 переноса и коммутатор 13 с соответствующими связями. 4 ил., 1 табл.

первый 10, второй 11, третий 12 вычи- 25 ИЛИ 44, выход которо1 о является выхо

татели, второй коммутатор 13, первый коммутатор 14, шифратор 15 цифр частного, накапливающий регистр 16, , выход 17 сумматора 2 делителя, выходы 18 и 19 соответственно старших и младших разрядов регистра 4 делимого выходы 20 и 21 соответственно старших и младших разрядов регистра 5 делимого, выходы 22-24 переноса соответственно вычитателей 10-12, выход 25 признаков возникновения и распространения переноса вычитателя 12, выходы 26-28 разности соответственно вычитателей 10-12, выход 29 старшего разряда вычитателей 12, выходы 30 и 31 шифратора 15 цифр частного, выход 32 устройства, с первого по пятый входы 33-37 устройства, вхо 39 задания режима устройства, второй вход 40 синхронизации устройства, шестой тактовый вход 41 устройства, первый вход 38 синхронизации устройства.

Шифратор 15 цифр частного (фиг.2) содержит элемент НЕ 42, триггер 43, элемент ИЛИ 44, элементы И 45 и 46, элемент ИЛИ 47, элемент НЕ 48, триггер 49, элемент И 50, элемент ИЛИ 51, причем вход задания режима шифратора 15 соединен с входом разрешения триггера 43, с первым входом элемен та И 46 и через элемент НЕ 42 с первыми входами элемента ИЛИ .44 и элементов И 50 и 45, вход сброса шиф

5

0

дом готовности шифратора 15, вых9ДЫ элементов ИЛИ 47 и 51 являются информационным выходом шифратора 15.

Формирователь 9 переноса (фиг.З) 0 содержит элемент И-ИЛИ 52, причем вход разрешения формирователя 9 соединен с инверсным входом первой группы элемента И-ИЛИ 52, вход второй группы, первый и второй входы третьей и четвертой групп которого являются информационным входом формирователя 9..

Числами 1, 2, ..;, К на верхней части диаграммы (фиг, 4) обозначены номера циклов. Слева от диаграммы по вертикали приведены номера сигналов в соответствии с юс номерами на фиг. 1. На диаграмме не приведен сигнал 39 задания режима работы устройства, так как он имеет значение

5

0

постоянного о .в режиме деления коротких чисел и постоянной 1 в режиме деления длинных чисел. Низкий уровень сигналов соответствует состоянию 1, выполняющей соответст- вунлцую функцию.

Диаграмма работы устройства в режиме деления коротких чисел не от- личается от диаграммы работы устройства в режиме деления длинных чисел благодаря возможности приема в регистры делимого и делителя в произвольной последовательности.

14Д1338

Формирователь 9 rrepenoca произво-, ит либо объединение вычитателей 10 11 в общий вычитатель, либо разъеинение указанных вычитателей. В бщем случае значение выходного игнала формирователя 9 имеет вид

на та чи чи

ст се бо но ва ос те 5 но де че те би че ус 1 .ющ в 25 4номо 34 яв 30 ны че ли си ще ре сл си МО с в ше ги в р

G

li)

+ Т

(О

(с; Чт

- признак, определяющий режим работы (в объединенном режиме значение Р равно О

10

разъединенном

равно режиме Р равно

- передаточные функции первого вычитателя

передаточные функции второ- 20 го вычитателя.

5 25 30

Шифратор цифр частного и коммутаторы 13 и 14 выполняют действия, при веденные в таблице.

В первой колонке приведено значение сигнала режима работы устройства в следующих трех колонках - значения переноса вычитателей 10-12, передающихся по выходам 22-24. В Следующи с четырех колонках приведены значения выходов коммутаторов 13 и 14 и значения двух битов частного на вьпсоде 31 за один цикл вычитания, Знаком ){ в таблице обозначены значения вычитателей 11 и 12, не влияющих на значение частного, а знаком - обозначено значение вькода 31, не определяемое значением переносов вычитателей. В таблице не приведены невозможные комбинации переносов на выходах 22-24. Обозначения РГ4 СДВ2, выход 28 СДВ2 означают, что содер- жимое регистра 4 и информация, передаваемая по выходу 28, сдвигается влево на 2 бита в коммутаторах 13 и 14. Таким же образом остальные обозначения выражают сдвиг влево на один или два бита информации соответствующего регистра или выхода в коммутаторах 13 и 14. При передачах со сдвигом в коммутаторах 13 и 14 на место освободившихся разрядов вдвигаются значения соответственно с выходов 20 и 18 регистров 5 и 4 делимо г о.

Устройство работает следующим обт разом.

, .

10

о

20

г

В зависимости от значения сигнала на входе 39 устройство может работать либо в режиме деления коротких чисел, либо в режиме деления длинных чисел.

Вначале рассмотрим работу устройства в режиме деления коротких чисел, когда делимое представляет собой двойное слого, а делитель - одно слово. Принцип работы -устройства в режиме деления коротких чисел основан на применении трех вычитателей, в которых осуществляется од- 5 новременное вычитание трех кратных делителя из делимого. На основе полу ченных значений переносов из вычитателей определяется значение двух битов частного и промежуточное значение делимого. Загрузка данных в устройство осуществляется через вход 1 под управлением сигналов, поступа- .ющих с входов 34-37. Данные шириной в одно слово поступают на, регистры 25 47 делимого и делителя в произвольной последовательности, определяемой значениями сигналов на вхрдах 34-37. 1 на каком-либо входе 34-37 является разрешением для приема дан- 30 ных в соответствующий регистр. Причем для приема данных в регистры делимого дополнительно устанавливается сигнал приема на входе 33, управляющем направлением приема данных в регистры делимого. После приема двух слов делимого меняются полярности сигнала на входе 33 и регистры дели МОго настраиваются на прием данных с выходов коммутаторов 13 и 14. Старшее слово делимого помещается в регистр 5 делимого, а младшее слово - в регистр 4 делимого.

Делитель в регистр 7 делителя поступает непосредственно с входа 1 устройства, а трехкратное значение делителя поступает на регистр 6 делителя с выхода сумматора 2 делителя через .мультиплексор 3 делителя. Формирование трехкратного значения делителя осуществляется в сумматоре 2. На первый вход сумматора 2 делитель поступает без изменения, а на второй вход - со сдвигом на один,бит влево, i На выходе сумматора 2 формируется, трехкратное значение делителя благодаря сложению делителя к его двухкратному значению. В режиме -деления коротких чисел трехкратное значение делителя с выхода сумматора 2 через

35

40

50

55

мультиплексор 3 поступает на регистр 6 делителя.

. Сигнал О на входе 39 соответствует режиму деления коротких чисел, который настраивает мультиплексор 8 на передачу на вход уменьшаемого вы- читателя tO выхода 21 регистра 5 делимого и запирает формирователь 9 переноса, тем самым устанавливается разъединенный режим работы вычитате- лей 10 и 12, когда запрещается передача переноса с выхода вычитателя 12 через схему передачи переноса на младший бит вычитателя 10. Сигнал режима работы устройства на входе 39 устанавливает также соответствующий режим работы коммутаторов 13 и 14 и шифратора 15 цифр частного.

После того как загружены регистры делимого и делителя, начинается циклический процесс вычитания трех кратных делителя из старшей части делимого в вычитателях 10-12, В вы- читателе 12 выполняется вычитание из старшей части делимого значения делителя, в вычитателе 11 - вычитани двухкратного значения делителя, в вычитателе 10 - вычитание трехкратного значения делителя.

Старшая часть делимого на входы уменьшаемого вычитателей 11 и 12 поступает непосредственно с выхода 21 регистра 5 делимого, а на вход уменьшаемого вычитателя 10 - через мультиплексор 8. На вход вычитаемого вычитателя 12 делитель поступает с выхода регистра 7 делителя без преобразования, а на вход вычитаемого вычитателя 11 поступает двухкратное значение делителя. Удвоение значения делителя осуществляется путем коммутации выхода регистра 7 делителя с входом вычитателя 11 со сдвигом на один бит влево. На вход вычитаемого вычитателя 10 трехкратное значение делителя поступает с выхода регистра 6 делителя.

Образовавшиеся разности в результате вычитания трех кратных делителя из старшей части делимого с выходов 26-28 вычитателей 10-12 поступают на информационные входы коммутатора 14, ла управляющие входы которого поступают переносы с выходов 22-24 вычитателей 10-12. Разность с выхода 26 и перенос с выхода 22 вычитателя 10 поступают также на .информационный и

0

управляющий входы коммутатора 13, на другой информационный вход которого поступает младшая часть делимого с выхода 19 регистра 4 делимого. На информационный вход коммутатора 14 поступает старшая часть делимого с выхода 21 регистра 5 делимого. Переносы с выходов 22-24 вычитателей 10- 12 поступают также на входы разрядов шифратора 15,

В коммутаторе 14 в режиме деления коротких чисел на основе полученной комбинации значений переносов из

g трех вычитателей осзпцествляется выбор одного из значений разностей с выходов трех вычитателей и старшей части делимого, сдвиг на два бита влево выбранного значения чиспа и передача его на вход регистра 5 делимого (см. таблицу).

Отсутствие переносов из всех вычитателей является признаком того, что старшая часть делимого меньше

5 делителя и она должна быть сдвинута влево для нового цикла вычитания. В этом случае через коммутатор 14 передается выход 21 регистра 5 делимого со сдвигом влево на два бита, а значение очередных двух битов частного устанавливается в О, При наличии переноса только из третьего вычитателя старшая часть больше делителя, но меньше его двухкратного значения, В этом случае через коммутатор 14 передается выход 28 вычитателя 12 со сдвигом на два бита влево и значение двух битов частного устанавливается 01. При наличии переносов только из вычитателей 11 и 12 старшая часть делимого больше двухкратного значения делителя, но меньше его трехкратного значения. В этом случае через коммутатор 14 передается выход 27 вычитателя 11 со сдвигом на два бита влево и значение битов частного устанавливается 10, Таким же образом при наличии переносов из всех вычитателей через коммутатор 14 передается выход 26 вычитателя 10 со сдвигом на два бита влево и значение битов частного устанавливается 11.

При сдвинутой передаче информации через коммутатор 14 освободившиеся два младших бита заполняются старшими двумя битами слова делимого, которые поступают с выхода 18 регистра 4 делимого.

0

5

0

5

0

5

Р коь(мутаторе 1 в деления коротких чисел выполняется только сдвинутая влево на два бита передача младшего слова делимого. Младшие два бита коммутатора 13 при сдвиге заполняются нулями.

В конце цикла вычитания на выходах коммутаторов 13 и 14 формируется значение промежуточного делимого, старшее слово которого представляет , собой сдвинутое на два бита влево старшее слово делимог о или результат вычитания в вычитателях 10-12 с приставленными справа двумя старшими битами мпадшего слова делимого, а младшее слово представляет собой сдвинутое влево на два бита младшее слово делимого с заполненными нулями при сдвиге влево младшими битами. Старшее слово промежуточного делимог с выхода коммутатора 14 передается на регистр 5 делимого, а мла;йпее слово с выхода коммутатора 13 передается на регистр 4 делимого. После этого цикл вычитания повторяется.

В режиме деления коротких чисел сигнал 1 на входе 39 настраивает шифратор 15 на выработку в каждом цикле двух битов частного на выходах элементов ИЛИ 47 и 51, а на выходе элемента ИЛИ 44 обеспечивает наличие постоянного сигнала 1.

В зависимости от полученной комбинации значений переносов в результате вычитания в трех вычитателях в каждом цикле параллельно с формиро- ванием значения промежуточного делимого согласно таблице вырабатьшается два бита частного, которые с выхода 31 поступают на входы младших двух битов накапливающего регистра 16. Выход 30 поступает на вход разрешения приема и сдвига информации в накапливающий регистр 16. Постоянный сигнал 1 выхода 30 дает возможность в каждом цикле работы устройства принять два бита частного в младшие бита накапливающего регистра и сдвигать влево на два бита его содержимое. Это дает возможность по мере генерации битов частного накапливать их в накапливающем регистре.

Сдвиг и накапливание частного в накапливающем регистре 16 происходит параллельно с передачей промежуточного делимого с выходов коммутаторов 13 и 14 на регистры 4 и 5 делимого.

5

0

Это обеспечивается сигналом, поступающим с входа 38 на входы синхронизации двухтактньпс триггеров, на которых реализованы регистры 4 и 5 делимого и накапливаюр1ий регистр 16,

Исходное состояние накапливающего регистра нулевое, что обеспечивается сигналом сброса, поступающим с входа 41. Затем в первом цикле в младшие биты накапливающего регистра принимаются два бита частного, а в регистры делимого принимается новое значение промежуточного делимого. В сле- 5 дующем цикле эти два бита частного сдвигаются в накапливаклцем регистре и на их место принимаются новые би- . ты частного, а в регистры делимого принимается очередное значение про- Q межуточного делимого. Процесс вычитания повторяется до тех пор, пока в накапливающем регистре не будет накоплено полное значение частного. После завершения деления регистр 4 5 делимого заполняется нулями, в регистре 5 находится остаток от деления, а в регистре 16 находится частное.

- Рассмотрим работу устройства в . 0 режиме деления длинных чисел, когда делимое и делитель представляют собой двойные слова.

Работа устройства в режиме деления длинных чисел основана на применении двух вычитателей в качестве одного объединенного вычитателя для вьгаита- ния чисел двойной длины. Для объеди- .йения использованы вычитатели 10 и 12, Объединение вычитателей осуществляется с помощью формирователя 9 переноса. На информационный вход формирователя 9 переноса с выходов 25 поступают передаточные функции вычитателя 12. На основе этих передаточных функций в формирователе 9 переноса реализуется функция переноса из вычитателя 12, который поступает на вход вычитателя 10 в качестве входного переноса, тем самым объединяя вычитатели 10 и 12.

В объединенном вычитателе производится вычитание чисел, расположенных в регистрах делимого 4 и 5 и делителя 6 и 7, причем в режиме деления длинных чисел старшее слово делимого помещается в регистр 4, а младшее слово - в регистр 5. В этом режиме выход сумматора 2 делителя блокирован сигналом режима работы на входе

5

0

5

0

5

накапливающий регистр и сдвиг его содержимого происходит через каждый цикл. Такой режим работы накапливающего регистра обеспечивается переменным значением сигнала на выходе 30, управляющего приемом информации в накапливающий регистр. В режиме деления длинных чисе л значение сигнала на выходе 30 соответствует состоянию триггера 43, исходное состояние которого нулевое. Сброс триггера 43 в первом цикле обеспечивает сигнал сброса на входе 41. Нулевое состоя39 и через мультиплексор 3 ст аршее слово делителя помещается в регистр 6 делителя. Младшее слово делителя помещается в регистр 7 делителя.

Старшее слово делимого с выхода 19 регистра 4 делимого через мультиплексор 8 поступает на вход уменьщае- мого вычитателя 10, на вход вычитаемого которого с выхода регистра 6 поступает старщее слово делителя.

Младшее слово делимого и делителя с выходов регистров 5 и 7 поступает на входы вычитателя 12,

В объединенном вычитателе из двои- ig ие триггера 43 и соответствующий ного слова делимого вычитается двои- этому состоянию О на выходе 30 зап- ное слово делителя. Результат вычи- рещает прием информации .в накапли- тания с вьгходов 26 и 28 объединенно- вающий регистр. В конце цикла парал10

го вычитателя поступает на коммутаторы 13 и 14 соответственно, на кото - рые поступают также старщее и младшее слова делимого с выходов регистров 4 и 5 делимого. При наличии переноса на выходе 22 объединенного вычитателя старшая часть результата вычитания со сдвигом на один бит влево передается на выход коммутатора 13, а младшая часть также со сдвигом на один бит влево передается на вы- ,ход коммутатора 14. При отсутствии переноса на выходы коммутаторов 13 и 14 со сдвигом на один бит влево передаются соответственно старшее и младшее слова делимого. При передаче со сдвигом на один бит влево информации в коммутаторе 13 на место младшего бита передается старший бит младшего слова делимого с выхода 20 регистра 5 при отсутствии переноса или старший бит результата вычитания с выхода 29 вычитат еля 12 при наличии переноса. При сдвиге информации в -коммутаторе 14 на место младшего бита поступает О. Сформированное значение промежуточного делимого с выходов коммутаторов 13 и 14 передается соответственно на регистры 4 и 5 делимого и цикл вычитания повторяется.

Параллельно с формированием промежуточного делимого в шифраторе 15 формируется один бит частного, значение которого совпадает со значением переноса на выходе 22 объединенного вычитателя (см. фиг. 2). Сфор- мированньй бит частного в первом цикле не принимается в накапливающий регистр, так как в режиме деления длинных, чисел прием информации в

44138810

накапливающий регистр и сдвиг его содержимого происходит через каждый цикл. Такой режим работы накапливающего регистра обеспечивается переменным значением сигнала на выходе 30, управляющего приемом информации в накапливающий регистр. В режиме деления длинных чисе л значение сигнала на выходе 30 соответствует состоянию триггера 43, исходное состояние которого нулевое. Сброс триггера 43 в первом цикле обеспечивает сигнал сброса на входе 41. Нулевое состоя

10

0

5

лельно с приемом нового значения промежуточного делимого в редкиетры делимого первый бит частного с выхода элемента ИЛИ 51 передается в триггер 49, значение которого через элементы И 46 и ИЛИ 47 передается на

5 разряд выхода 31. В следующем цикле снимается сигнал сброса и второй сигнал, поступающий по входу 40, устанавливает в 1 триггер 43, появляется сигнал 1 на выходе 30 и

Q разрешается прием информации в накапливающий регистр. В конце цикла на выходе элемента ИЛИ 51 появляется второй бит частного и два бита частного с выхода 31 принимаются, в млад- шие биты накапливаклцего регистра. Одновременно содерлдамое накапливающего регистра сдвигается влево на два бита, а в регистры делимого принимается новое значение промежуточного частного. Второй сигнал, синхронизирующий работу триггера 43, опережает первый сигнал, синхронизирующий регистры делимого и делителя, накапливающий регистр и триггер 49, и выбран с таким расчетом, чтобы к моменту , когда на выходе 31 сформированы очередные биты частного, был вьфабо- тан сигнал приема в накапливающий регистр. В дальнейшем в каждом цикле триггер 43 перебрасывается, причем в каждом неразрешенном цикле очеред ной бит частного запоминается в двухкратном триггере А9, а в разрешенном цикле пара битов частного, образованная предьщущим битом частного на выходе элемента ИЛИ А7 и новым битом на выходе элемента ИЛИ 51, принимается в младшие биты накапливающего регистра, одновременно сдвигается

5

0

предыдущее значение накаплива да1его регистра. После завершения деления в накапливающем регистре находится двойное слово частного, а в регистрах делимого - двойное слово остатка

Изобретение позволяет повысить быстродействие устройства.

Формула изобретения

Устройство для деления чисел, содержащее сумматор делителя, первый и второй регистры делимого, первый и второй регистры делителя, первый, второй и третий вычитатели, первый коммутатор, шифратор гщфр частного и накопительный регистр, причем информационный вход устройства соединен с первыми информационными входами первого и второго регистров делимого и с информационным входом второго регистра делителя, входы задани направления приема первого и второго регистров делимого объединены и соединены с первым .тактовым входом устройства, тактовые входы с второго по пятый которого соединены с входами разрешения приема соответственно второго и первого регистров делителя второго и первого регистров делимого выход младших разрядов второго регистра делимого соединен ic входами уменьшаемых второго и третьего вычи- тателей, выходы разности вычитателей с первого по третий соединены соответственно с информационными входами с первого по третий первого коммутатора, выход которого соединен с вторым информационным входом второго регистра делимого, выходы переноса вычитателей с первого по третий соединены соответственно с первым, вто- рым и третьим управляющими входами первого коммутатора и с входами соответствующих разрядов шифратора цифр частного, информационный выход которого соединен с входом младших разрядов накапливающего регистра, вход сброса и вход синхронизации которого соединены соответственно с шестым тактовым входом устройства и с первым входом синхронизации устройства, выход которого соединен с выходом накапливающего регистра, пер1- вый синхронизации устройства соединен с входами синхронизации первого и второго регистров делимого.

первого и второго регистров делителя,

о-тличаюп;ее ся

тем.

0

5

0

5

0

5

0

5

0

5

что, с целью расширения функциональных возможностей за счет деления чисел переменного формата, оно содержит мультиплексор делителя, мультиплексор делимого, формирователь переноса и второй коммутатор, причем информационный вход устройства соединен прямо с первым информационным входом мультиплексора делителя, с входом первого слагаемого сумматора делителя и со сдвигом на один разряд в сторону старших разрядов - с входом второго слагаемого сумматора делителя, выход которого соединен с вторым информационным входом мультиплексора делителя, выход которого соединен с информационным входом первого регистра делителя, выход которого соединен с входом вычитаемого первого вычитателя, вход уменьшаемого которого соединен с выходом мультиплексора делимого, первый информационный вход которого соединен с первым информационным входом второго коммутатора и с выходом младших разрядов первого регистра делимого, выход старших разрядов которого соединен с четвертым информационным входом первого коммутатора, пятый информационный вход которого соединен с вторым информационным входом мультиплексора делимого и с выходом младших разрядов второго регистра делимого, выход старшего разряда которого соединен с вторым информационным входом второго коммутатора, третий и четвертый информационные входы которого соединены соответственно с выходом разности первого вычитателя и с выходом старшего разряда третьего вычи- тателя, выход признаков возникновения и распространения переноса которого соединен с информационным входом формирователя переноса, выход которого соединен с входом переноса первого вычитателя, выход переноса которого соединен с первым управляющим входом второго коммутатора, вы- ход которого соединен с вторым информационным входом первого регистра делимого, выход второго регистра делителя соединен прямо с входом вычитаемого третьего вычитателя и со сдвигом на один разряд в сторону старших разрядов - с входом вычитаемого второго вычитателя, вход задания

П144

режима устройства соединен с управляющими входами мультиплексоров делимого и делителя, с входом разрешения формирователя переноса, с вторым ущ)авляюи}им входом второго коммутатора, с четвертым управляющим входом первого коммутатора и с входом зада - ния режима шифратора цифр частного.

13881

выход готовности которого соединен с входом разрешения накапливающего регистра, первый и второй входы синхронизации и шестой тактовый вход устройства соединены соответственно с первым и вторым входами синхронизации и входом сброса шифратора цифр частного.

U I . I

2 i

Т

17 I f I J

JL

X

2 i

Фие.

Ц)игЛ

| Устройство для деления | 1979 |

|

SU773618A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления десятичных чисел | 1984 |

|

SU1241235A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Патент США № 3293418, кл | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Двухтактный двигатель внутреннего горения | 1924 |

|

SU1966A1 |

Авторы

Даты

1988-11-30—Публикация

1987-03-31—Подача