Изобретение относится к вычислительной технике и может быть исполь- Ьовано в устройствах управления Цифровых электронных вычислительных машин (ЭВМ).

Цель изобретения .- сокращение объема блока памяти микрокоманд.

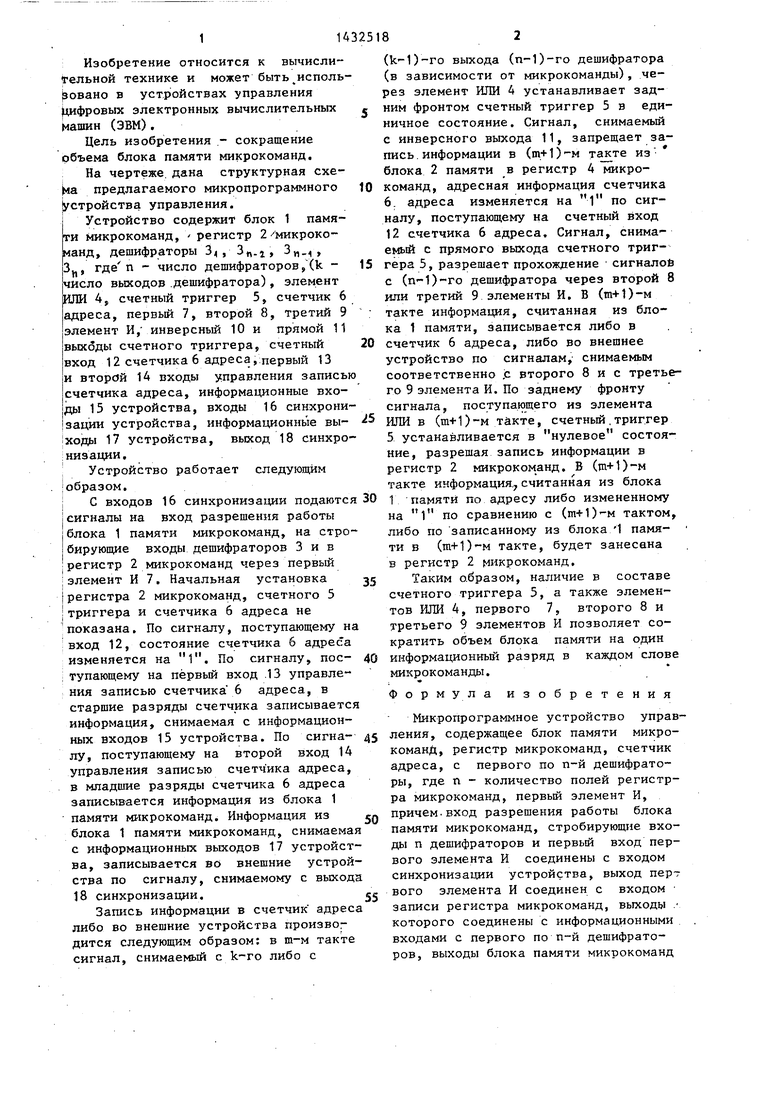

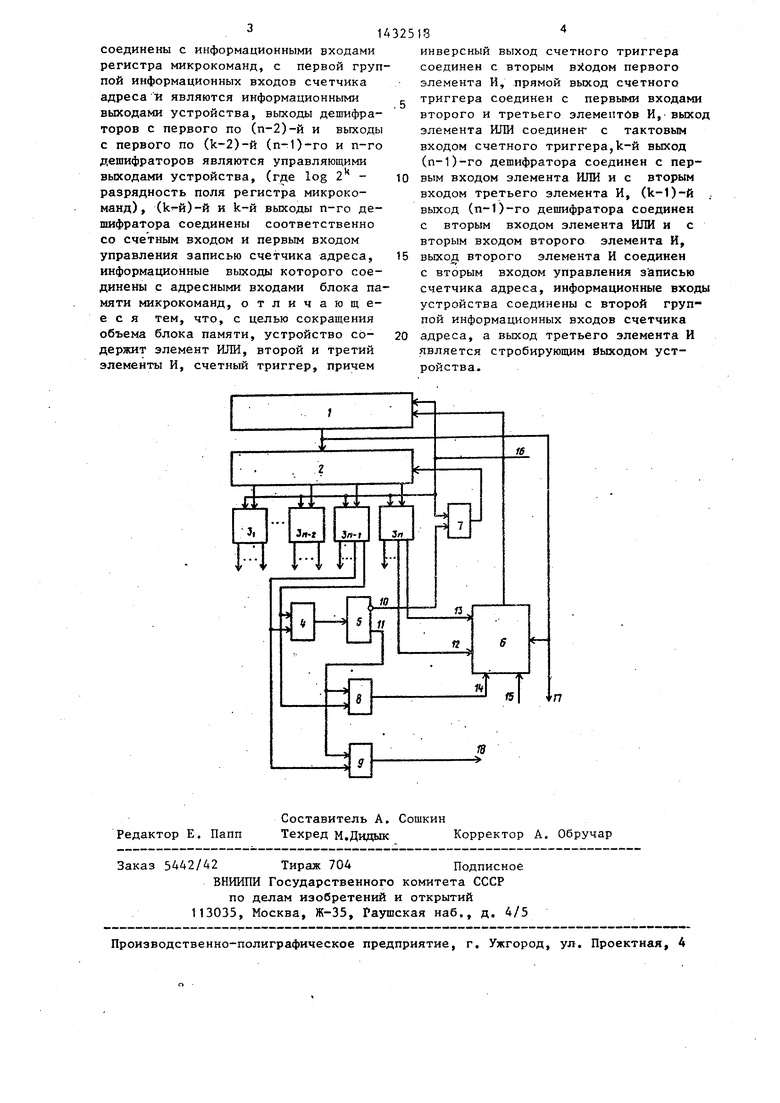

На чертеже, дана структурная схе- Иа предлагаемого микропрограммного устройства управления.

Устройство содержит блок 1 памяти микрокоманд, регистр 2 микрокоманд, дешифраторы З.З., 3„,,, 3jj, где п - число дешифраторов j,Xk - число выходов .дешифратора), элемент рЖ 4, счетный триггер 5, счетчик 6 адреса, первьй 7, второй 8, третий 9 элемент И, инверсный 10 и прямой 11 выходы счетного триггера, счетный |вход 12 счетчика 6 адреса,:первый 13 и второй 14 входы управления записью счетчика адреса, информационные входы 15 устройства, входы 16 синхрони- |зации устройства, информационные вы- |ходы 17 устройства, выход 18 синхро- : низации,

: Устройство работает следующим Iобразом.

: с входов 16 синхронизации подаются I сигналы на вход разрешения работы I блока 1 памяти микрокоманд, на стро- I бирую1цие входы дешифраторов 3 и в I регистр 2 микрокоманд через первый ;элемент И 7, Начальная установка регистра 2 микрокоманд, счетного 3 триггера и счетчика 6 адреса не показана. По сигналу, поступающему на вход 12, состояние счетчика 6 адреса изменяется на 1. По сигналу, пос- тупающему на первый вход .13 управления записью счетчика 6 адреса, в старшие разряды счетчика записывается информация, снимаемая с информационных входов 15 устройства. По сигна- лу, поступающему на второй вход 14 управления записью счетчика адреса, в младшие разряды счетчика 6 адреса записывается информация из блока 1 памяти микрокоманд. Информация из блока 1 памяти микрокоманд, снимаемая с информационных выходов 17 устройства, записывается во внешние устройства по сигналу, снимаемому с выхода 18 синхронизации.

Запись информации в счетчик адреса либо во внешние устройства произвог дится следующим образом: в т-м такте сигнал, снимаемый с k-ro либо с

(k-l)-ro выхода (п-1)-го дешифратора (в зависимости от микрокоманды), через элемент ИЛИ 4 устанавливает задним фронтом счетный триггер 5 в единичное состояние. Сигнал, снимаемый с инверсного выхода 11, запрещает запись, информации в (т+1)-м такте из блока 2 памяти в регистр 4 микрокоманд, адресная информация счетчика 6. адреса изменяется на 1 по сигналу, поступающему на счетный вход 12 счетчика 6 адреса. Сигнал, снима- емьй с прямого выхода счетного триггера 5, разрешает прохождение сигналов с ( дешифратора через второй 8 или третий 9 элементы И. В (т+1)-м такте информация, считанная из блока 1 памяти, записывается либо в счетчик 6 адреса, либо во внешнее устройство по сигналам, снимаемым соответственно р второго 8 и с третьего 9 элемента И. По заднему фронту сигнала, поступающего из элемента ИЛИ в (т+1 )-м такте, счетный,триггер 5 устанавливается в нулевое состояние, разрешая запись информации в регистр 2 микрокоманд. В (щ+1)-м такте информация,считанная из блока 1 памяти по адресу либо измененному на l по сравнению с (in-t-l) -M тактом либо по записанному из блока 1 памя- ти в (m+D-M такте, будет занесена в регистр 2 микрокоманд.

Таким о.бразом, наличие в составе счетного триггера 5, а также элементов ИЛИ 4, первого 7, второго 8 и третьего 9 элементов И позволяет сократить объем блока памяти на один информационный разряд в каждом слове микрокоманды.

Форм у л а изобретения

Микропрограммное устройство управления, содержащее блок памяти микрокоманд, регистр микрокоманд, счетчик адреса, с первого по п-й дешифраторы, где п - количество полей регистр- ра микрокоманд, первый элемент И, причем.вход разрешения работы блока памяти микрокоманд, стробирующие входы п дешифраторов и первый вход первого элемента И соединены с входом синхронизации устройства, выход первого элемента И соединен с входом записи регистра микрокоманд, выходы которого соединены с информационными входами с первого по п-й дешифраторов, выходы блока памяти микрокоманд

соединены с информационными входами регистра микрокоманд, с первой группой информационных входов счетчика адреса « являются информационными выходами устройства, выходы депшфра- торов с первого по (п-2)-й и выходы с первого по (k-2)-ft (п-1)-го и п-го дешифраторов являются управляющими выходами устройства, (где log 2 разрядность поля регистра микрокоманд), (k -й)-й и k-й выходы п-го дешифратора соединены соответственно со счетным входом и первым входом управления записью счетчика адреса, информационные выходы которого соединены с адресными входами блока памяти микрокоманд, отличающееся тем, что, с целью сокращения объема блока памяти, устройство со- держит элемент ИЛИ, второй и третий элементы И, счетный триггер, причем

IS4

инверсный выход счетного триггера соединен с вторым вводом первого злемента И, прямой выход счетного триггера соединен с первыми входами второго и третьего элементов И,- выхо элемента ИЛИ соединен- с тактовым входом счетного триггера,k-й выход (n-l)-ro дешифратора соединен с первым входом элемента ИЛИ и с вторым входом третьего элемента И, (k-l)-A выход (n-l)-ro дешифратора соединен с вторым входом элемента ИЛИ и с вторым входом второго элемента И, выхо второго элемента И соединен с вторым входом управления з аписью счетчика адреса, информационные входы устройства соединены с второй группой информационных входов счетчика адреса, а выход третьего элемента И является стробирующим йыходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микро-ЭВМ | 1982 |

|

SU1124316A1 |

| Устройство микропрограммного управления | 1981 |

|

SU985788A1 |

| Электронная вычислительная машина | 1988 |

|

SU1520533A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1140120A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| Микропрограммный процессор | 1981 |

|

SU1037262A1 |

| Программируемое устройство управления | 1988 |

|

SU1659983A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

| Мультимикропрограммное устройство управления с контролем | 1985 |

|

SU1272333A1 |

| Мультимикропрограммное устройство управления | 1985 |

|

SU1256026A1 |

Изобретение относится к вычислительной технике, в частности к микропрограммным устройствам управления. Целью изобретения является сокращение объема блока памяти микрокоманд. В устройство, содержащее блок памяти микрокоманд, регистр микрокоманд, дешифраторы, первый элемент И, счётчик адреса, введены второй и третий элементы И, элемент ИЛИ и счетный триггер, что позволяет сократить объем блока памяти на один информационный разряд в каждом слове микрокоманды. 1 ил.

II

Н ИР F

}

11

3л-г

Зя

Ю

/3

II

о

п

13

| Вертикальный осевой насос | 1979 |

|

SU861747A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления | 1980 |

|

SU947861A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-10-23—Публикация

1986-10-10—Подача